#### **DETAILED DESCRIPTION**

#### SPEECH/SOUND QUALITY

The ISD4004 ChipCorder series includes devices offered at 4.0, 5.3, 6.4, and 8.0 KHz sampling frequencies, allowing the user a choice of speech quality options. Increasing the duration within a product series decreases the sampling frequency and bandwidth, which affects sound quality. Please refer to the ISD4004 Series Product Summary table on the second page to compare filter pass band and product durations.

The speech samples are stored directly into on-chip nonvolatile memory without the digitization and compression associated with other solutions. Direct analog storage provides a natural sounding reproduction of voice, music, tones, and sound effects not available with most solid-state solutions.

#### **DURATION**

To meet end system requirements, the ISD4004 series products are single-chip solutions at 8, 10, 12, 16 minutes.

#### **FLASH STORAGE**

One of the benefits of ISD's ChipCorder technology is the use of on-chip nonvolatile memory, which provides zero-power message storage. The message is retained for up to 100 years (typically) without power. In addition, the device can be re-recorded (typically) over 100,000 times.

#### MICROCONTROLLER INTERFACE

A four-wire (SCLK, MOSI, MISO,  $\overline{SS}$ ) SPI interface is provided for ISD4004 control and addressing functions. The ISD4004 is configured to operate as a peripheral slave device, with a microcontroller-based SPI bus interface. Read/Write access to all the internal registers occurs through this SPI interface. An interrupt signal ( $\overline{INT}$ ) and internal readonly Status Register are provided for handshake purposes.

#### **PROGRAMMING**

The ISD4004 series is also ideal for playback-only applications, where single or multiple message Playback is controlled through the SPI port. Once the desired message configuration is created, duplicates can easily be generated via an ISD programmer.

#### PIN DESCRIPTIONS

## **VOLTAGE INPUTS (V\_{CCA}, V\_{CCD})**

To minimize noise, the analog and digital circuits in the ISD4004 devices use separate power busses. These +3 V busses are brought out to separate pins and should be tied together as close to the supply as possible. In addition, these supplies should be decoupled as close to the package as possible.

## GROUND INPUTS (VSSA, VSSD)

The ISD4004 series utilizes separate analog and digital ground busses. The analog ground ( $V_{SSA}$ ) pins should be tied together as close to the package as possible and connected through a low-impedance path to power supply ground. The digital ground ( $V_{SSD}$ ) pin should be connected through a separate low-impedance path to power supply ground. These ground paths should be large enough to ensure that the impedance between the  $V_{SSA}$  pins and the  $V_{SSD}$  pin is less than 3  $\Omega$ . The backside of the die is connected to  $V_{SS}$  through the substrate resistance. In a chip-on-board design, the die attach area must be connected to  $V_{SS}$  or left floating.

28 ☐ SCLK □ V<sub>CCD</sub> MOSI [ 27 ☐ XCLK MISO [ 26  $\Box$   $\overline{\mathsf{INT}}$ V<sub>SSD</sub> [ 25 V<sub>SSA</sub> □ 28 □ NC ☐ NC NC [ ☐ RAC 24 RAC □ 27 26 F V<sub>CCA</sub> NC [  $\square$   $\lor_{SSA}$ 23 NC  $\square$ 25 ANA IN+ NC □ □ NC NC [ ISD4004 24 ANA IN-NT □ NC [ □ NC □ 8 21 23 🗖 NC XCLK 🗀 22 AM CAP NC [ ☐ NC V<sub>CCD</sub> SCLK 🗖 21 🗖 NC ISD4004 NC [ □ NC 10 20 AUD OUT SS  $\square$ □ V<sub>CCA</sub> V<sub>SSA</sub> 11 19 🗖 NC MOSI 🗖 10 MISO 🗖 11 18 🗖 V<sub>SSA</sub> V<sub>SSA</sub> 12 17 ☐ ANA IN+ 17 V<sub>SSA</sub> NC V<sub>SSD</sub> □ 12 AUD OUT [ ANA IN-13 NC 🗖 13 AM CAP NC □ 14 15 🗖 NC ☐ NC 14 15 28-PIN TSOP PDIP/SOIC

Figure 1: ISD4004 Series TSOP and PDIP/SOIC Pinouts

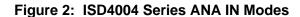

## NON-INVERTING ANALOG INPUT (ANA IN+)

This pin is the non-inverting analog input that transfers the signal to the device for recording. The analog input amplifier can be driven single ended or differentially. In the single-ended input mode, a 32 mVp-p (peak-to-peak) maximum signal should be capacitively connected to this pin for optimal signal quality. This capacitor value, together with the 3 K $\Omega$  input impedance of ANA IN+, is selected to give cutoff at the low frequency end of the voice passband. In the differential-input mode, the maximum input signal at ANA IN+ should be 16 mVp-p for optimal signal quality. The circuit connections for the two modes are shown in Figure 2 on page 2.

## INVERTING ANALOG INPUT (ANA IN-)

This pin is the inverting analog input that transfers the signal to the device for recording in the differential-input mode. In this differential-input mode, a 16 mVp-p maximum input signal at ANA INshould be capacitively coupled to this pin for optimal signal quality as shown in the ISD4004 Series ANA IN Modes, Figure 2. This capacitor value should be equal to the coupling capacitor used on the ANA IN+ pin. The input impedance at ANA INis nominally 56 K $\Omega$ . In the single-ended mode, ANA IN- should be capacitively coupled to  $V_{SSA}$ through a capacitor equal to that used on the ANA IN+ input.

## **AUDIO OUTPUT (AUD OUT)**

This pin provides the audio output to the user. It is capable of driving a 5 K $\Omega$  impedance. It is recommended that this pin be AC coupled.

**NOTE** The AUDOUT pin is always at 1.2 volts when the device is powered up. When in playback, the output buffer connected to this pin can drive a load as small as 5  $K\Omega$ . When in record, a resistor connects AUD-OUT to the internal 1.2 volt analog ground supply. This resistor is approximately 850  $K\Omega$ , but will vary somewhat according to the sample rate of the device. This relatively high impedance allows this pin to be connected to an audio bus without loading it down.

# **SLAVE SELECT (SS)**

This input, when LOW, will select the ISD4004 device.

## **MASTER OUT SLAVE IN (MOSI)**

This is the serial input to the ISD4004 device. The master microcontroller places data on the MOSI line one half-cycle before the rising clock edge to be clocked in by the ISD4004 device.

## MASTER IN SLAVE OUT (MISO)

This is the serial output of the ISD4004 device. This output goes into a high-impedance state if the device is not selected.

## SERIAL CLOCK (SCLK)

This is the clock input to the ISD4004. It is generated by the master device (microcontroller) and is used to synchronize data transfers in and out of the device through the MISO and MOSI lines. Data is latched into the ISD4004 on the rising edge of SCLK and shifted out of the device on the falling edge of SCLK.

## **INTERRUPT (INT)**

The ISD4004 interrupt pin goes LOW and stays LOW when an Overflow (OVF) or End of Message (EOM) marker is detected. This is an open drain output pin. Each operation that ends in an EOM or Overflow will generate an interrupt including the message cueing cycles. The interrupt will be cleared the next time an SPI cycle is initiated. The interrupt status can be read by an RINT instruction.

Overflow Flag (OVF)—The Overflow flag indicates that the end of the ISD4004's analog memory has been reached during a record or playback operation.

End of Message (EOM)—The End-of-Message flag is set only during playback operation when an EOM is found. There are eight EOM flag position options per row.

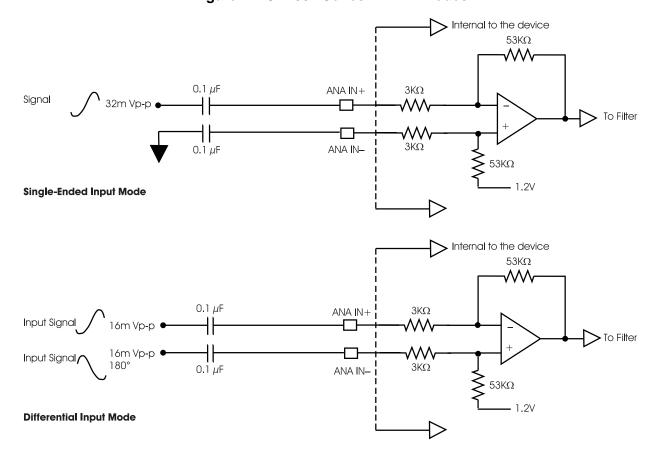

## **ROW ADDRESS CLOCK (RAC)**

This is an open drain output pin that provides a signal with a 200 ms period at the 8 KHz sampling frequency. (This represents a single row of memory and there are 2400 rows of memory in the ISD4004 series devices.) This signal stays HIGH for 175 ms and stays LOW for 25 ms when it reaches the end of a row.

The RAC pin stays HIGH for  $109.38~\mu sec$  and stays LOW for  $15.63~\mu sec$  in Message Cueing mode (see page 5 for a more detailed description of Message Cueing). Refer to the AC Parameters table for RAC timing information on other sample rate products.

When a record command is first initiated, the RAC pin remains HIGH for an extra  $T_{RACLO}$  period. This is due to the need to load sample and hold circuits internal to the device. This pin can be used for message management techniques.

#### **EXTERNAL CLOCK INPUT (XCLK)**

The external clock input for the ISD4004 products has an internal pull-down device. These products are configured at the factory with an internal sampling clock frequency centered to  $\pm 1$  percent of specification. The frequency is then maintained to a variation over the entire commercial temperature and operating voltage ranges as defined by the minimum/maximum limits in the applicable AC Parameters table. The internal clock has a tolerance, over the extended temperature, industrial temperature and voltage ranges as defined by the minimum/maximum limits in the applicable AC Parameters table. A regulated power supply is recommended for industrial temperature range parts. If greater precision is required, the device can be clocked through the XCLK pin in Table 1.

Table 1: External Clock Input Clocking

Table

| Part Number | Sample Rate | Required Clock |

|-------------|-------------|----------------|

| ISD4004-08M | 8,0 KHz     | 1024 KHz       |

| ISD4004-10M | 6.4 KHz     | 819.2 KHz      |

| ISD4004-12M | 5.3 KHz     | 682.7 KHz      |

| ISD4004-16M | 4.0 KHz     | 512 KHz        |

These recommended clock rates should not be varied because the antialiasing and smoothing filters are fixed. Thus, aliasing problems can occur if the sample rate differs from the one recommended. The duty cycle on the input clock is not critical, as the clock is immediately divided by two internally. If the XCLK is not used, this input should be connected to ground.

## **AUTOMUTE™ FEATURE (AM CAP)**

This pin is used in controlling the AutoMute feature. The AutoMute feature attenuates the signal when it drops below an internally set threshold. This helps to eliminate noise (with 6 dB of attenuation) when there is no signal (i.e., during periods of silence). A 1 μF capacitor to ground should be connected to the AM CAP pin. This capacitor becomes a part of an internal peak detector which senses the signal amplitude (peak). This peak level is compared to an internally set threshold to determine the Auto-Mute trip point. For large signals the AutoMute attenuation is set to 0 dB while 6 dB of attenuation occurs for silence. The 1 µF capacitor also affects the rate at which the AutoMute feature changes with the signal amplitude (or the attack time). The Automute feature can be disabled by connecting the AM CAP pin to V<sub>CCA</sub>

# SERIAL PERIPHERAL INTERFACE (SPI) DESCRIPTION

The ISD4004 series operates from an SPI serial interface. The SPI interface operates with the following protocol.

The data transfer protocol assumes that the microcontroller's SPI shift registers are clocked on the falling edge of the SCLK. With the ISD4004, data is clocked in on the MOSI pin on the rising clock edge. Data is clocked out on the MISO pin on the falling clock edge.

- 1. All serial data transfers begin with the falling edge of SS pin.

- 2. SS is held LOW during all serial communications and held HIGH between instructions.

- 3. Data is clocked in on the rising clock edge and data is clocked out on the falling clock edge.

- 4. Play and Record operations are initiated by enabling the device by asserting the \$\overline{SS}\$ pin LOW, shifting in an opcode and an address field to the ISD4004 device (refer to the Opcode Summary on the page 6).

- 5. The opcodes and address fields are as follows: <8 control bits> and <16 address bits>.

- **6.** Each operation that ends in an EOM or Overflow will generate an interrupt, including the Message Cueing cycles. The Interrupt will be cleared the next time an SPI cycle is initiated.

- 7. As Interrupt data is shifted out of the ISD4004 MISO pin, control and address data is simultaneously being shifted into the MOSI pin. Care should be taken such that the data shifted in is compatible with current system operation. It is possible to read interrupt data and start a new operation within the same SPI cycle.

- **8.** An operation begins with the RUN bit set and ends with the RUN bit reset.

- **9.** All operations begin with the rising edge of  $\overline{SS}$ .

#### **MESSAGE CUEING**

Message cueing allows the user to skip through messages, without knowing the actual physical location of the message. This operation is used during playback. In this mode, the messages are skipped 1600 times faster than in normal playback mode. It will stop when an EOM marker is reached. Then, the internal address counter will point to the next message.

**Table 2: Opcode Summary**

| Instruction       | Opcode <8 bits><br>Address <16 bits> | Operational Summary                                                                                                               |

|-------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| POWERUP           | 00100XXX                             | Power-Up: Device will be ready for an operation after T <sub>PUD</sub> ,                                                          |

| SETPLAY           | 11100XXX < A15-A0>                   | Initiates Playback from address <a15-a0>.</a15-a0>                                                                                |

| PLAY              | 11110XXX                             | Playback from the current address (until EOM or OVF).                                                                             |

| SETREC            | 10100XXX <a15-a0></a15-a0>           | Initiates a Record operation from address <a15-a0>.</a15-a0>                                                                      |

| REC               | 10110XXX                             | Records from current address until OVF is reached.                                                                                |

| SETMC             | 11101XXX <a15-a0></a15-a0>           | Initiates Message Cueing (MC) from address <a15-a0>.</a15-a0>                                                                     |

| MC <sup>1</sup>   | 111111XXX                            | Performs a Message Cue. Proceeds to the end of the current message (EOM) or enters OVF condition if no more messages are present. |

| STOP              | 0X110XXX                             | Stops current operation.                                                                                                          |

| STOPPWRDN         | 0X01XXXX                             | Stops current Operation and enters stand-by (power-down) mode.                                                                    |

| RINT <sup>2</sup> | 0X110XXX                             | Read Interrupt status bits: Overflow and EOM.                                                                                     |

- 1. Message Cueing can be selected only at the beginning of a play operation.

- 2. As the Interrupt data is shifted out of the ISD4004, control and address data is being shifted in. Care should be taken such that the data shifted in is compatible with current system operation. It is possible to read interrupt data and start a new operation at the same time. See Figure 5 through Figure 8 for Opcode format.

#### **POWER-UP SEQUENCE**

The ISD4004 will be ready for an operation after  $T_{PUD}$  (25 ms approximately for 8 KHz sample rate). The user needs to wait  $T_{PUD}$  before issuing an operational command. For example, to play from address 00 the following programing cycle should be used.

## Playback Mode

- 1. Send POWERUP command.

- 2. Wait T<sub>PUD</sub> (power-up delay).

- 3. Send SETPLAY command with address 00.

- 4. Send PLAY command.

The device will start playback at address 00 and it will generate an interrupt when an EOM is reached. It will then stop playback.

#### **Record Mode**

- 1. Send POWERUP command.

- 2. Wait T<sub>PUD</sub> (power-up delay).

- 3. Send POWERUP command.

- **4.** Send SETREC command with address 00.

- **5.** Send REC command.

The device will start recording at address 00 and it will generate an interrupt when an overflow is reached (end of memory array). It will then stop recording.

#### **SPI PORT**

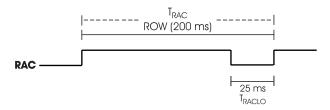

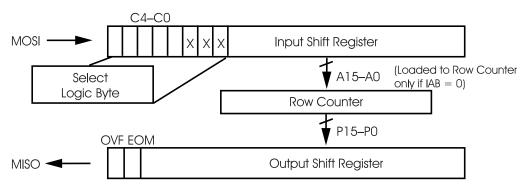

The following diagram describes the SPI port and the control bits associated with it.

Figure 3: SPI Port

#### **SPI CONTROL REGISTER**

The SPI control register provides control of individual device functions such as Play, Record, Message Cueing, Power-Up and Power-Down, Start and Stop operations, and Ignore Address pointers.

**Table 3: SPI Control Register**

| Control<br>Register | Bit    | Device Function                                 | Control<br>Register | Bit    | Device Function                                                                                          |

|---------------------|--------|-------------------------------------------------|---------------------|--------|----------------------------------------------------------------------------------------------------------|

| RUN                 |        | Enable or Disable an operation                  | PU                  |        | Master power control                                                                                     |

| =                   | 1<br>0 | Start<br>Stop                                   | 11 11               | 1<br>0 | Power-Up<br>Power-Down                                                                                   |

| P/R                 |        | Selects Play or Record operation                | IAB                 |        | Ignore address control bit                                                                               |

| =                   | 1<br>0 | Play<br>Record                                  | =                   | 1<br>0 | Ignore input address register (A15–A0) Use the input address register contents for an operation (A15–A0) |

| MC                  |        | Enable or Disable Message Cueing                | P15-P0              |        | Output of the row pointer register                                                                       |

| =                   | 1<br>0 | Enable Message Cueing<br>Disable Message Cueing | A15-A0              |        | Input address register                                                                                   |

Figure 4: SPI Interface Simplified Block Diagram

Table 4: Absolute Maximum Ratings (Packaged Parts)<sup>(1)</sup>

| Condition                                                         | Value                                                     |

|-------------------------------------------------------------------|-----------------------------------------------------------|

| Junction temperature                                              | 150°C                                                     |

| Storage temperature range                                         | -65°C to +150°C                                           |

| Voltage applied to any pin                                        | (V <sub>SS</sub> - 0.3 V) to<br>(V <sub>CC</sub> + 0.3 V) |

| Voltage applied to any pin (Input current limited to $\pm 20$ mA) | (V <sub>SS</sub> - 1.0 V) to<br>(V <sub>CC</sub> + 1.0 V) |

| Lead temperature<br>(soldering – 10 seconds)                      | 300°C                                                     |

| V <sub>CC</sub> - V <sub>SS</sub>                                 | -0.3 V to +7.0 V                                          |

Stresses above those listed may cause permanent damage to the device. Exposure to the absolute maximum ratings may affect device reliability. Functional operation is not implied at these conditions.

Table 5: Operating Conditions (Packaged Parts)

| Condition                                             | Value            |

|-------------------------------------------------------|------------------|

| Commercial operating temperature range <sup>(1)</sup> | 0°C to +70°C     |

| Extended operating temperature <sup>(1)</sup>         | -20°C to +70°C   |

| Industrial operating temperature <sup>(1)</sup>       | -40°C to +85°C   |

| Supply voltage (V <sub>CC</sub> ) <sup>(2)</sup>      | +2.7 V to +3.3 V |

| Ground voltage (V <sub>SS</sub> ) <sup>(3)</sup>      | 0 V              |

- 1. Case temperature.

- $2. \quad V_{CC} = V_{CCA} = V_{CCD}.$

- $\mathbf{3.} \quad V_{SS} = V_{SSA} = V_{SSD}.$

Table 6: DC Parameters (Packaged Parts)

| Symbol               | Parameters                                                    | Min <sup>(2)</sup>    | Typ <sup>(1)</sup> | Max <sup>(2)</sup>    | Units    | Conditions                                        |

|----------------------|---------------------------------------------------------------|-----------------------|--------------------|-----------------------|----------|---------------------------------------------------|

| V <sub>IL</sub>      | Input Low Voltage                                             |                       |                    | V <sub>CC</sub> x 0.2 | V        |                                                   |

| V <sub>IH</sub>      | Input High Voltage                                            | V <sub>CC</sub> x 0,8 |                    |                       | V        |                                                   |

| V <sub>OL</sub>      | Output Low Voltage                                            |                       |                    | 0,4                   | V        | $I_{OL} = 10 \mu\text{A}$                         |

| V <sub>OL1</sub>     | RAC, INT Output Low Voltage                                   |                       |                    | 0,4                   | V        | $I_{OL} = 1 \text{ mA}$                           |

| V <sub>OH</sub>      | Output High Voltage                                           | V <sub>CC</sub> - 0.4 |                    |                       | V        | $I_{OH} = -10  \mu A$                             |

| lcc                  | V <sub>CC</sub> Current (Operating)<br>— Playback<br>— Record |                       | 15<br>25           | 30<br>40              | mA<br>mA | $R_{EXT} = \infty^{(3)}$ $R_{EXT} = \infty^{(3)}$ |

| I <sub>SB</sub>      | V <sub>CC</sub> Current (Standby)                             |                       | 1                  | 10                    | μΑ       | (3) (4)                                           |

| I <sub>IL</sub>      | Input Leakage Current                                         |                       |                    | ±1                    | μΑ       |                                                   |

| l <sub>HZ</sub>      | MISO Tristate Current                                         |                       | 1                  | 10                    | μΑ       |                                                   |

| R <sub>EXT</sub>     | Output Load Impedance                                         | 5                     |                    |                       | КΩ       |                                                   |

| R <sub>ANA IN+</sub> | ANA IN+ Input Resistance                                      | 2.2                   | 3,0                | 3,8                   | КΩ       |                                                   |

| R <sub>ANA IN</sub>  | ANA IN- Input Resistance                                      | 40                    | 56                 | 71                    | ΚΩ       |                                                   |

| A <sub>ARP</sub>     | ANA IN+ or ANA IN- to AUD OUT Gain                            |                       | 25                 |                       | dB       | (5)                                               |

- **1.** Typical values:  $T_A = 25^{\circ}C$  and 3.0 V.

- 2. All min/max limits are guaranteed by ISD via electrical testing or characterization. Not all specifications are 100 percent tested.

- **3.**  $V_{CCA}$  and  $V_{CCD}$  connected together.

- **4.**  $\overline{SS} = V_{CCA} = V_{CCD}$ ,  $XCLK = MOSI = V_{SSA} = V_{SSD}$  and all other pins floating.

- 5. Measured with AutoMute feature disabled.

Table 7: AC Parameters (Packaged Parts)

| Symbol           | Characteristic        |                                                          | Min <sup>(2)</sup> | Typ <sup>(1)</sup>       | Max <sup>(2)</sup> | Units                    | Conditions                                                                                                                                                           |

|------------------|-----------------------|----------------------------------------------------------|--------------------|--------------------------|--------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F <sub>S</sub>   | Sampling<br>Frequency | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 8.0<br>6.4<br>5.3<br>4.0 |                    | KHz<br>KHz<br>KHz<br>KHz | (5)<br>(5)<br>(5)<br>(5)                                                                                                                                             |

| F <sub>CF</sub>  | Filter Pass Band      | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 3.4<br>2.7<br>2.3<br>1.7 |                    | KHz<br>KHz<br>KHz<br>KHz | 3-dB Roll-Off Point <sup>(3)</sup> (7)<br>3-dB Roll-Off Point <sup>(3)</sup> (7)<br>3-dB Roll-Off Point <sup>(3)</sup> (7)<br>3-dB Roll-Off Point <sup>(3)</sup> (7) |

| T <sub>REC</sub> | Record Duration       | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 8<br>10<br>12<br>16      |                    | min<br>min<br>min<br>min | (6)<br>(6)<br>(6)<br>(6)                                                                                                                                             |

Table 7: AC Parameters (Packaged Parts)

| Symbol                                     | Characte                                        | ristic                                                   | Min <sup>(2)</sup> | Typ <sup>(1)</sup>               | Max <sup>(2)</sup> | Units                        | Conditions                          |

|--------------------------------------------|-------------------------------------------------|----------------------------------------------------------|--------------------|----------------------------------|--------------------|------------------------------|-------------------------------------|

| T <sub>PLAY</sub>                          | Playback Duration                               | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 8<br>10<br>12<br>16              |                    | min<br>min<br>min<br>min     |                                     |

| T <sub>PUD</sub>                           | Power-Up Delay                                  | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 25<br>31.25<br>37.5<br>50        |                    | msec<br>msec<br>msec<br>msec |                                     |

| T <sub>STOP</sub> or<br>T <sub>PAUSE</sub> | Stop or Pause in<br>Record or Play              | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 50<br>62.5<br>75<br>100          |                    | msec<br>msec<br>msec<br>msec |                                     |

| T <sub>RAC</sub>                           | RAC Clock Period                                | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 200<br>250<br>300<br>400         |                    | msec<br>msec<br>msec<br>msec | (9)<br>(9)<br>(9)<br>(9)            |

| T <sub>RACLO</sub>                         | RAC Clock Low<br>Time                           | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 25<br>31.25<br>37.5<br>50        |                    | msec<br>msec<br>msec<br>msec |                                     |

| T <sub>RACM</sub>                          | RAC Clock Period<br>in Message<br>Cueing Mode   | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 125<br>156.3<br>187.5<br>250     |                    | µsec<br>µsec<br>µsec<br>µsec |                                     |

| T <sub>RACML</sub>                         | RAC Clock Low<br>Time in Message<br>Cueing Mode | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 15.63<br>19.53<br>23.44<br>31.25 |                    | µsec<br>µsec<br>µsec<br>µsec |                                     |

| THD                                        | Total Harmonic Dist                             | ortion                                                   |                    | 1                                | 2                  | %                            | @ 1 KHz                             |

| V <sub>IN</sub>                            | ANA IN Input Voltag                             | le                                                       |                    |                                  | 32                 | mV                           | Peak-to-Peak <sup>(4) (7) (8)</sup> |

- **1.** Typical values:  $T_A = 25^{\circ}C$  and 3.0 V.

- 2. All min/max limits are guaranteed by ISD via electrical testing or characterization. Not all specifications are 100 percent tested

- 3. Low-frequency cut off depends upon the value of external capacitors (see Pin Descriptions).

- **4.** Single-ended input mode. In the differential input mode,  $V_{IN}$  maximum for ANA IN+ and ANA IN- is 16mVp-p.

- 5. For greater stability, an external clock can be utilized (see Pin Descriptions).

- **6.** Filter specification applies to the antialiasing filter and the smoothing filter. Therefore, from input to output, expect a 6dB drop by nature of passing through both filters.

- **7.** The typical output voltage will be approximately 570mVp-p with  $V_{\rm IN}$  at 32mVp-p.

- 8. For optimal signal quality, this maximum limit is recommended.

- **9.** When a record command is sent,  $T_{RAC} = T_{RAC} + T_{RACLO}$  on the first row addressed.

**Table 8:** Absolute Maximum Ratings (Die)<sup>(1)</sup>

| Condition                                                    | Value                                                     |

|--------------------------------------------------------------|-----------------------------------------------------------|

| Junction temperature                                         | 150°C                                                     |

| Storage temperature range                                    | -65°C to +150°C                                           |

| Voltage applied to any pad                                   | (V <sub>SS</sub> - 0.3 V) to<br>(V <sub>CC</sub> + 0.3 V) |

| Voltage applied to any pad (Input current limited to ±20 mA) | (V <sub>SS</sub> - 1.0 V) to<br>(V <sub>CC</sub> + 1.0 V) |

| V <sub>CC</sub> - V <sub>SS</sub>                            | -0.3 V to +7.0 V                                          |

Stresses above those listed may cause permanent damage to the device. Exposure to the absolute maximum ratings may affect device reliability. Functional operation is not implied at these conditions.

**Table 9: Operating Conditions (Die)**

| Condition                                        | Value            |

|--------------------------------------------------|------------------|

| Commercial operating temperature range           | 0°C to +50°C     |

| Supply voltage (V <sub>CC</sub> ) <sup>(1)</sup> | +2.7 V to +3.3 V |

| Ground voltage (V <sub>SS</sub> ) <sup>(2)</sup> | 0 V              |

1.

$$V_{CC} = V_{CCA} = V_{CCD}$$

$$2. \quad V_{SS} = V_{SSA} = V_{SSD}.$$

Table 10: DC Parameters (Die)

| Symbol               | Parameters                                                    | Min <sup>(2)</sup>    | Typ <sup>(1)</sup> | Max <sup>(2)</sup>    | Units    | Conditions                                                      |

|----------------------|---------------------------------------------------------------|-----------------------|--------------------|-----------------------|----------|-----------------------------------------------------------------|

| V <sub>IL</sub>      | Input Low Voltage                                             |                       |                    | V <sub>CC</sub> x 0.2 | V        |                                                                 |

| V <sub>IH</sub>      | Input High Voltage                                            | V <sub>CC</sub> x 0,8 |                    |                       | V        |                                                                 |

| V <sub>OL</sub>      | Output Low Voltage                                            |                       |                    | 0.4                   | V        | $I_{OL} = 10  \mu A$                                            |

| V <sub>OL1</sub>     | RAC, ĪNT Output Low Voltage                                   |                       |                    | 0.4                   | V        | $I_{OL} = 1 \text{ mA}$                                         |

| V <sub>OH</sub>      | Output High Voltage                                           | V <sub>CC</sub> - 0.4 |                    |                       | ٧        | $I_{OH} = -10  \mu A$                                           |

| lcc                  | V <sub>CC</sub> Current (Operating)<br>— Playback<br>— Record |                       | 15<br>25           | 30<br>40              | mA<br>mA | $R_{\text{EXT}} = \infty^{(3)}$ $R_{\text{EXT}} = \infty^{(3)}$ |

| I <sub>SB</sub>      | V <sub>CC</sub> Current (Standby)                             |                       | 1                  | 10                    | μΑ       | (3) (4)                                                         |

| I <sub>IL</sub>      | Input Leakage Current                                         |                       |                    | ±1                    | μΑ       |                                                                 |

| I <sub>HZ</sub>      | MISO Tristate Current                                         |                       | 1                  | 10                    | μΑ       |                                                                 |

| R <sub>EXT</sub>     | Output Load Impedance                                         | 5                     |                    |                       | KΩ       |                                                                 |

| R <sub>ANA IN+</sub> | ANA IN+ Input Resistance                                      | 2.2                   | 3,0                | 3,8                   | KΩ       |                                                                 |

| R <sub>ANA IN</sub>  | ANA IN- Input Resistance                                      | 40                    | 56                 | 71                    | KΩ       |                                                                 |

| A <sub>ARP</sub>     | ANA IN+ or ANA IN- to AUDOUT Gain                             |                       | 25                 |                       | dB       | (5)                                                             |

- **1.** Typical values:  $T_A = 25^{\circ}C$  and 3.0 V.

- 2. All min/max limits are guaranteed by ISD via electrical testing or characterization. Not all specifications are 100 percent tested.

- **3.**  $V_{CCA}$  and  $V_{CCD}$  connected together.

- **4.**  $\overline{SS} = V_{CCA} = V_{CCD}$ , XCLK = MOSI =  $V_{SSA} = V_{SSD}$  and all other pins floating.

- 5. Measured with AutoMute feature disabled.

Table 11: AC Parameters (Die)

| Symbol                                     | Characte                                        | ristic                                                   | Min <sup>(2)</sup> | Typ <sup>(1)</sup>               | Max <sup>(2)</sup> | Units                        | Conditions                                                                                                           |

|--------------------------------------------|-------------------------------------------------|----------------------------------------------------------|--------------------|----------------------------------|--------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------|

| F <sub>S</sub>                             | Sampling<br>Frequency                           | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 8.0<br>6.4<br>5.3<br>4.0         |                    | KHz<br>KHz<br>KHz<br>KHz     | (5)<br>(5)<br>(5)<br>(5)                                                                                             |

| F <sub>CF</sub>                            | Filter Pass Band                                | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 3.4<br>2.7<br>2.3<br>1.7         |                    | KHz<br>KHz<br>KHz<br>KHz     | 3dB Roll-Off Point (3) (6)<br>3dB Roll-Off Point (3) (6)<br>3dB Roll-Off Point (3) (6)<br>3dB Roll-Off Point (3) (6) |

| T <sub>REC</sub>                           | Record Duration                                 | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 8<br>10<br>12<br>16              |                    | min<br>min<br>min<br>min     | (5)<br>(5)<br>(5)<br>(5)                                                                                             |

| T <sub>PLAY</sub>                          | Playback Duration                               | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 8<br>10<br>12<br>16              |                    | min<br>min<br>min<br>min     | (5)<br>(5)<br>(5)<br>(5)                                                                                             |

| T <sub>PUD</sub>                           | Power-Up Delay                                  | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 25<br>31.25<br>37.5<br>50        |                    | msec<br>msec<br>msec<br>msec |                                                                                                                      |

| T <sub>STOP</sub> Or<br>T <sub>PAUSE</sub> | Stop or Pause in<br>Record or Play              | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 50<br>62.5<br>75<br>100          |                    | msec<br>msec<br>msec<br>msec |                                                                                                                      |

| T <sub>RAC</sub>                           | RAC Clock Period                                | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 200<br>250<br>300<br>400         |                    | msec<br>msec<br>msec<br>msec | (9)<br>(9)<br>(9)<br>(9)                                                                                             |

| T <sub>RACLO</sub>                         | RAC Clock Low<br>Time                           | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 25<br>31.25<br>37.5<br>50        |                    | msec<br>msec<br>msec<br>msec |                                                                                                                      |

| T <sub>RACM</sub>                          | RAC Clock Period<br>in Message<br>Cueing Mode   | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 125<br>156.3<br>187.5<br>250     |                    | usec<br>usec<br>usec         |                                                                                                                      |

| T <sub>RACML</sub>                         | RAC Clock Low<br>Time in Message<br>Cueing Mode | ISD4004-08M<br>ISD4004-10M<br>ISD4004-12M<br>ISD4004-16M |                    | 15.63<br>19.53<br>23.44<br>31.25 |                    | usec<br>usec<br>usec         |                                                                                                                      |

欢迎索取免费详细资料、设计选型指南和光盘、样品;产品繁多未能尽录,欢迎来电查询。

中国传感器科技信息网:HTTP://WWW.SENSOR-IC.COM/

工控安防网:HTTP://WWW.PC-PS.NET/

消费电子专用电路网:HTTP://WWW.SUNSTARE.COM/

E-MAIL: xjr5@163.com szss20@163.com

MSN: suns8888@hotmail.com

QQ: 195847376

地址: 深圳市福田区福华路福庆街鸿图大厦 1602 室 电话: 0755-83376549 83376489 83387030 83387016

传真:0755-83376182 83338339 邮编:518033 手机:(0)13902971329

深圳展销部:深圳华强北路赛格电子市场 2583 号 TEL/FAX:

0755-83665529 25059422

北京分公司:北京海淀区知春路 132 号中发电子大厦 3097 号

TEL: 010-81159046 82615020 13501189838 FAX: 010-82613476 上海分公司:上海市北京东路 668 号上海賽格电子市场 2B35 号

TEL: 021-28311762 56703037 13701955389 FAX: 021-56703037 西安分公司:西安高新开发区 20 所(中国电子科技集团导航技术研究所)

西安劳动南路 88 号电子商城二楼 D23 号

TEL: 029-81022619 13072977981 FAX:029-88789382

成都:TEL:(0)13717066236

技术支持:0755-83394033 13501568376