# *CC2400* 2.4 GHz Low-Power RF Transceiver

# Applications

- 2.4 GHz MHz ISM/SRD band systems

- Game controllers

- Sports and leisure equipment

# **Product Description**

The **CC2400** is a true single-chip 2.4 GHz RF transceiver designed for low-power and low-voltage wireless applications. The RF transceiver is integrated with a baseband modem supporting data rates up to 1 Mbps.

The **CC2400** is a low-cost, highly integrated solution enabling robust wireless communication in the 2.4 - 2.4835 GHz unlicensed ISM band. It is intended for systems compliant with world-wide regulations covered by EN 300 440 (Europe), CFR47 Part 15 (US) and ARIB STD-T66 (Japan).

Targeting a wide range of applications at 2.4 GHz, the **CC2400** supports over-the-air data rates of 10 kbps, 250 kbps and 1 Mbps without requiring any modifications to the hardware.

The *CC2400* provides extensive hardware support for packet handling, data buffering, burst transmissions, data coding

# **Key Features**

- True single-chip 2.4 GHz RF transceiver with baseband modem

- 10 kbps, 250 kbps and 1 Mbps overthe-air data rates

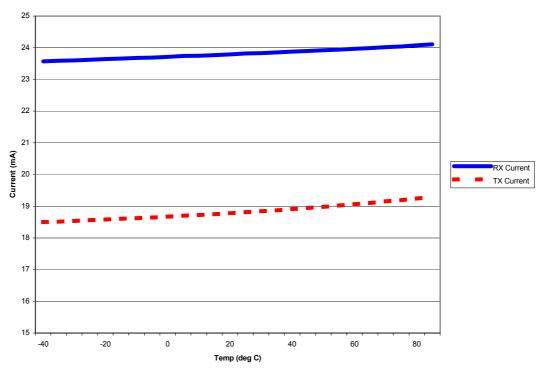

- Low current consumption (RX: 24 mA)

- Low core supply voltage (1.8 V)

- Programmable output power

- No external RF switch / filter needed

- I/Q low-IF receiver

- I/Q direct up-conversion transmitter

- Few external components

- FIFO allows bursting of data

- Wireless audio

- PC peripherals

- Advanced toys

and error detection reducing the workload on the host microcontroller.

The main operating parameters of *CC2400* can be programmed via an SPI-bus. In a typical system *CC2400* will be used together with a microcontroller and a few external, passive components.

*CC2400* is based on Chipcon's SmartRF<sup>®</sup>-03 technology in 0.18  $\mu$ m CMOS.

- Packet handling hardware

- Data buffering

- Digital RSSI output

- Small size (QFN 48 package), 7x7 mm

- Reference design complies with EN 300 328, EN 300 440, FCC CFR47 part 15 and ARIB STD-T66

- Powerful and flexible development tools available

- Easy-to-use software for generating the **CC2400** configuration data

This document contains information on a pre-production product. Specifications and information herein are subject to change without notice.

| Table                                        | e of contents                                                                                                                                                                                                                                     |                                                    |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|                                              | BBREVIATIONS                                                                                                                                                                                                                                      |                                                    |

|                                              | EATURES                                                                                                                                                                                                                                           |                                                    |

|                                              | BSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                           |                                                    |

|                                              | PERATING CONDITIONS                                                                                                                                                                                                                               |                                                    |

|                                              | LECTRICAL SPECIFICATIONS                                                                                                                                                                                                                          |                                                    |

|                                              | ENERAL CHARACTERISTICS                                                                                                                                                                                                                            |                                                    |

|                                              | F TRANSMIT SECTION                                                                                                                                                                                                                                |                                                    |

|                                              | F RECEIVE SECTION                                                                                                                                                                                                                                 |                                                    |

|                                              | FC SECTION                                                                                                                                                                                                                                        | 10                                                 |

| 10                                           | RSSI / CARRIER SENSE SECTION                                                                                                                                                                                                                      |                                                    |

| 11                                           | IF SECTION                                                                                                                                                                                                                                        |                                                    |

| 12                                           | FREQUENCY SYNTHESIZER SECTION                                                                                                                                                                                                                     |                                                    |

| 13                                           | DIGITAL INPUTS/OUTPUTS                                                                                                                                                                                                                            |                                                    |

| 14                                           | PIN ASSIGNMENT                                                                                                                                                                                                                                    |                                                    |

| 15                                           | CIRCUIT DESCRIPTION                                                                                                                                                                                                                               |                                                    |

| 16                                           | APPLICATION CIRCUIT                                                                                                                                                                                                                               |                                                    |

| 16.1                                         |                                                                                                                                                                                                                                                   |                                                    |

| 16.2                                         |                                                                                                                                                                                                                                                   |                                                    |

| 16.3                                         |                                                                                                                                                                                                                                                   |                                                    |

| 16.4                                         | 2.0                                                                                                                                                                                                                                               |                                                    |

| 16.5                                         |                                                                                                                                                                                                                                                   |                                                    |

| 16.6                                         |                                                                                                                                                                                                                                                   |                                                    |

| 17                                           | CONFIGURATION OVERVIEW                                                                                                                                                                                                                            |                                                    |

| 18<br>19                                     | CONFIGURATION SOFTWARE                                                                                                                                                                                                                            | 20                                                 |

| 20                                           | OVERVIEW OF CONFIGURATIONS AND HARDWARE SUPPORT                                                                                                                                                                                                   |                                                    |

| 20<br>21                                     | MICROCONTROLLER INTERFACE AND PIN CONFIGURATION                                                                                                                                                                                                   |                                                    |

| 21.1                                         |                                                                                                                                                                                                                                                   | -                                                  |

| 21.1                                         |                                                                                                                                                                                                                                                   |                                                    |

| 21.2                                         |                                                                                                                                                                                                                                                   |                                                    |

| 22                                           | DATA BUFFERING                                                                                                                                                                                                                                    |                                                    |

| 22.1                                         |                                                                                                                                                                                                                                                   |                                                    |

| 22.2                                         |                                                                                                                                                                                                                                                   |                                                    |

| 23                                           | PACKET HANDLING HARDWARE SUPPORT                                                                                                                                                                                                                  |                                                    |

| 23.1                                         |                                                                                                                                                                                                                                                   |                                                    |

| 23.2                                         | ERROR DETECTION                                                                                                                                                                                                                                   | 29                                                 |

| 23.3                                         | HARDWARE INTERFACE                                                                                                                                                                                                                                | 31                                                 |

| 24                                           | DATA / LINE ENCODING                                                                                                                                                                                                                              | 31                                                 |

| 24.1                                         | DATA ENCODING IN BUFFERED MODE                                                                                                                                                                                                                    | 31                                                 |

| 24.2                                         |                                                                                                                                                                                                                                                   |                                                    |

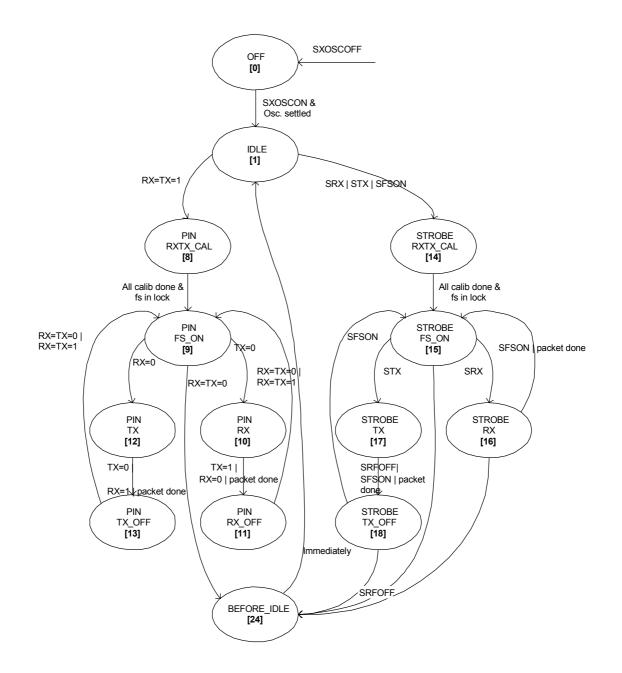

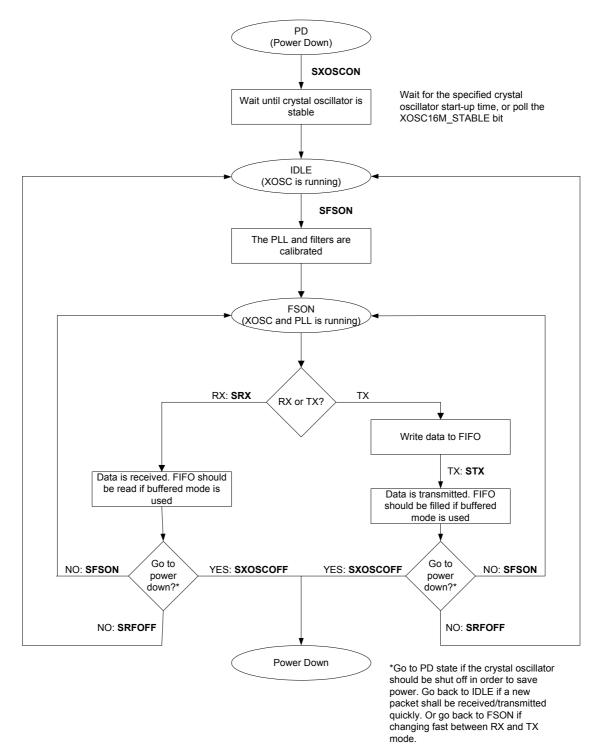

| 25                                           | RADIO CONTROL STATE MACHINE                                                                                                                                                                                                                       | 34                                                 |

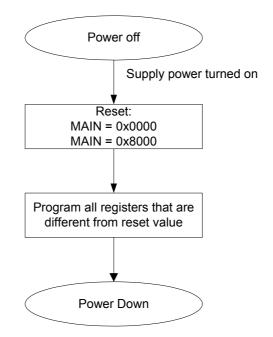

| 26                                           | POWER MANAGEMENT FLOW CHART                                                                                                                                                                                                                       |                                                    |

| 27                                           | FSK MODULATION FORMATS                                                                                                                                                                                                                            |                                                    |

| 28                                           | BUILT-IN TEST PATTERN GENERATOR                                                                                                                                                                                                                   |                                                    |

| 29                                           |                                                                                                                                                                                                                                                   |                                                    |

| 30                                           | RECEIVER CHANNEL BANDWIDTH                                                                                                                                                                                                                        |                                                    |

|                                              | DATA RATE PROGRAMMING                                                                                                                                                                                                                             | 40                                                 |

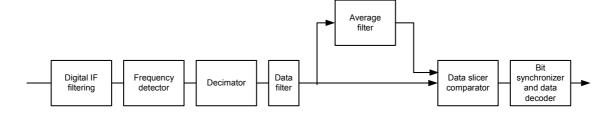

| 31                                           | DATA RATE PROGRAMMING<br>DEMODULATOR, BIT SYNCHRONIZER AND DATA DECISION                                                                                                                                                                          | 40<br>41                                           |

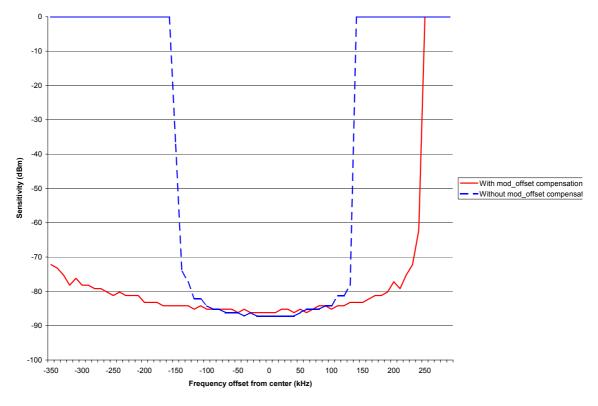

| 31<br>32                                     | DATA RATE PROGRAMMING<br>DEMODULATOR, BIT SYNCHRONIZER AND DATA DECISION<br>AUTOMATIC FREQUENCY CONTROL                                                                                                                                           | 40<br>41<br>42                                     |

| 31<br>32<br>33                               | DATA RATE PROGRAMMING<br>DEMODULATOR, BIT SYNCHRONIZER AND DATA DECISION<br>AUTOMATIC FREQUENCY CONTROL<br>LINEAR IF AND AGC SETTINGS                                                                                                             | 40<br>41<br>42<br>43                               |

| 31<br>32<br>33<br>34                         | DATA RATE PROGRAMMING<br>DEMODULATOR, BIT SYNCHRONIZER AND DATA DECISION<br>AUTOMATIC FREQUENCY CONTROL<br>LINEAR IF AND AGC SETTINGS<br>RSSI                                                                                                     | 40<br>41<br>42<br>43<br>44                         |

| 31<br>32<br>33<br>34<br>35                   | DATA RATE PROGRAMMING<br>DEMODULATOR, BIT SYNCHRONIZER AND DATA DECISION<br>AUTOMATIC FREQUENCY CONTROL<br>LINEAR IF AND AGC SETTINGS<br>RSSI<br>CARRIER SENSE                                                                                    | 40<br>41<br>42<br>43<br>44<br>45                   |

| 31<br>32<br>33<br>34<br>35<br>36             | DATA RATE PROGRAMMING<br>DEMODULATOR, BIT SYNCHRONIZER AND DATA DECISION<br>AUTOMATIC FREQUENCY CONTROL<br>LINEAR IF AND AGC SETTINGS<br>RSSI<br>CARRIER SENSE<br>INTERFACING AN EXTERNAL LNA OR PA                                               | 40<br>41<br>42<br>43<br>44<br>45<br>45             |

| 31<br>32<br>33<br>34<br>35<br>36<br>37       | DATA RATE PROGRAMMING<br>DEMODULATOR, BIT SYNCHRONIZER AND DATA DECISION<br>AUTOMATIC FREQUENCY CONTROL<br>LINEAR IF AND AGC SETTINGS<br>RSSI<br>CARRIER SENSE<br>INTERFACING AN EXTERNAL LNA OR PA<br>GENERAL PURPOSE / TEST OUTPUT CONTROL PINS | 40<br>41<br>42<br>43<br>44<br>45<br>45<br>45       |

| 31<br>32<br>33<br>34<br>35<br>36<br>37<br>38 | DATA RATE PROGRAMMING<br>DEMODULATOR, BIT SYNCHRONIZER AND DATA DECISION<br>AUTOMATIC FREQUENCY CONTROL<br>LINEAR IF AND AGC SETTINGS<br>RSSI<br>CARRIER SENSE<br>INTERFACING AN EXTERNAL LNA OR PA                                               | 40<br>41<br>42<br>43<br>44<br>45<br>45<br>45<br>45 |

| 38.2 |                                               |    |

|------|-----------------------------------------------|----|

| 39   | ALTERNATE TX IF SETTING                       |    |

| 40   | VCO                                           | 48 |

| 41   | VCO SELF-CALIBRATION                          | 48 |

| 42   | OUTPUT POWER PROGRAMMING                      | 48 |

| 43   | CRYSTAL OSCILLATOR                            | 49 |

| 44   | INPUT / OUTPUT MATCHING                       | 50 |

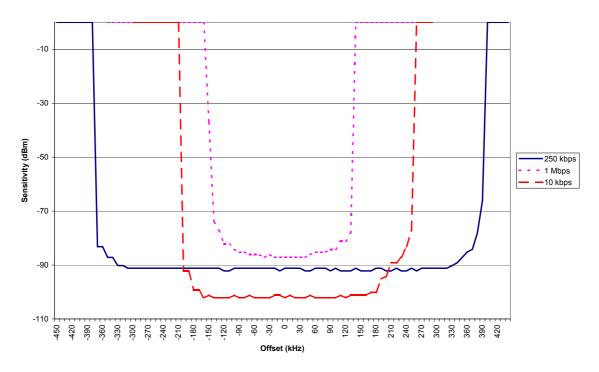

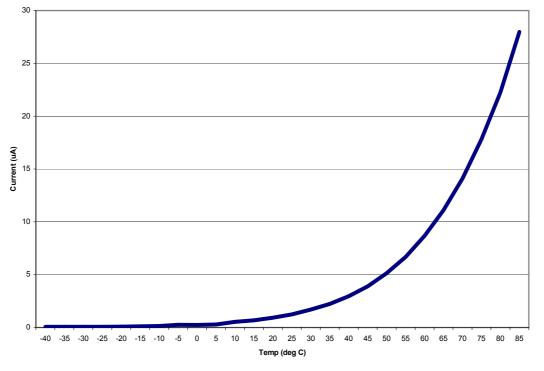

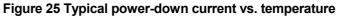

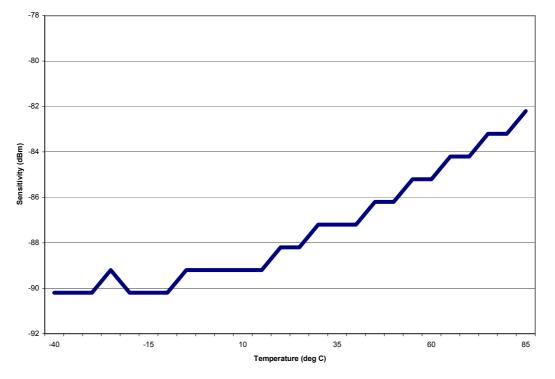

| 45   | TYPICAL PERFORMANCE GRAPHS                    | 50 |

| 46   | SYSTEM CONSIDERATIONS AND GUIDELINES          | 53 |

| 46.1 | SRD REGULATIONS                               | 53 |

| 46.2 | 2 FREQUENCY HOPPING AND MULTI-CHANNEL SYSTEMS | 53 |

| 46.3 | B DATA BURST TRANSMISSIONS                    | 53 |

| 46.4 | CONTINUOUS TRANSMISSIONS                      | 53 |

| 46.5 | 5 CRYSTAL DRIFT COMPENSATION                  | 53 |

| 46.6 | SPECTRUM EFFICIENT MODULATION                 | 54 |

| 46.7 | ZOW LATENCY SYSTEMS                           | 54 |

| 46.8 | B LOW COST SYSTEMS                            | 54 |

| 46.9 | BATTERY OPERATED SYSTEMS                      | 54 |

| 46.1 |                                               |    |

| 47   | PCB LAYOUT RECOMMENDATIONS                    | 56 |

| 48   | ANTENNA CONSIDERATIONS                        |    |

| 49   | CONFIGURATION REGISTERS                       | 58 |

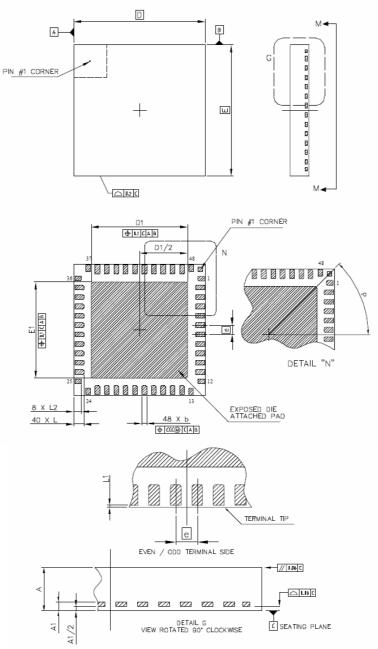

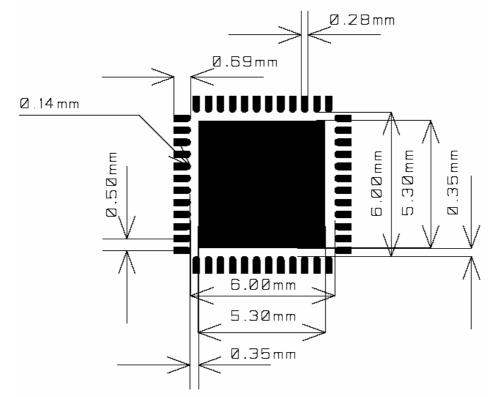

| 50   | PACKAGE DESCRIPTION (QFN48)                   | 76 |

| 51   | RECOMMENDED LAYOUT FOR PACKAGE (/QFN48)       | 77 |

| 52   | PACKAGE THERMAL PROPERTIES                    | 77 |

| 53   | SOLDERING INFORMATION                         | 77 |

| 54   | IC MARKING                                    | 78 |

| 55   | PLASTIC TUBE SPECIFICATION                    | 80 |

| 56   | CARRIER TAPE AND REEL SPECIFICATION           | 80 |

| 57   | ORDERING INFORMATION                          | 80 |

| 58   | GENERAL INFORMATION                           | 81 |

| 58.1 | DOCUMENT HISTORY                              | 81 |

| 58.2 | 2 PRODUCT STATUS DEFINITIONS                  | 82 |

| 58.3 | B DISCLAIMER                                  | 82 |

| 58.4 | TRADEMARKS                                    | 82 |

| 58.5 | 5 LIFE SUPPORT POLICY                         | 82 |

| 59   | ADDRESS INFORMATION                           | 83 |

# 1 Abbreviations

| ACP       | Adjacent Channel Power                              |

|-----------|-----------------------------------------------------|

| ACR       | Adjacent Channel Rejection                          |

| ADC       | Analog-to-Digital Converter                         |

| AFC       |                                                     |

|           | Automatic Frequency Correction                      |

| AGC       | Automatic Gain Control                              |

| BER       | Bit Error Rate                                      |

| BOM       | Bill Of Materials                                   |

| bps       | bits per second                                     |

| BT        | Bandwidth-Time product (for GFSK)                   |

| CRC       | Cyclic Redundancy Check                             |

| CSMA      | Carrier Sense Multiple Access                       |

| CSMA / CA | Carrier Sense Multiple Access / Collision Avoidance |

| DAC       | Digital-to-Analog Converter                         |

| ESR       | Equivalent Series Resistance                        |

| FH        | Frequency Hopping                                   |

| FHSS      | Frequency Hopping Spread Spectrum                   |

| FIFO      | First In First Out (queue)                          |

| FS        | Frequency Synthesizer                               |

| FSK       | Frequency Shift Keying                              |

| GFSK      | Gaussian Frequency Shift Keying                     |

| IF        | Intermediate Frequency                              |

| ISM       | Industrial Scientific Medical                       |

| kbps      | kilo bits per second                                |

| LNA       | Low Noise Amplifier                                 |

| Mbps      | Mega bits per second                                |

| MCU       | Micro Controller Unit                               |

| NRZ       | Non Return to Zero                                  |

| PA        | Power Amplifier                                     |

| PD        | Phase Detector                                      |

| PCB       |                                                     |

|           | Printed Circuit Board                               |

| PN9       | Pseudo-random Bit Sequence (9-bit)                  |

| PLL       | Phase Locked Loop                                   |

| PRN       | Pseudo Random Number                                |

| PRNG      | Pseudo Random Number Generator                      |

| RF        | Radio Frequency                                     |

| RSSI      | Received Signal Strength Indicator                  |

| RX        | Receive (mode)                                      |

| SPI       | Serial Peripheral Interface                         |

| SRD       | Short Range Device                                  |

| TBD       | To Be Decided/Defined                               |

| TDMA      | Time Division Multiple Access                       |

| ТХ        | Transmit (mode)                                     |

| VCO       | Voltage Controlled Oscillator                       |

| VGA       | Variable Gain Amplifier                             |

|           |                                                     |

### 2 Features

- 2400 2483 MHz RF transceiver

- GFSK and FSK modulation

- Very low current consumption (RX: 24 mA)

- Over-the-air data rates of 10 kbps, 250 kbps and 1 Mbps

- High sensitivity (-87 dBm @ 1Mbps, BER=10<sup>-3</sup>)

- Agile frequency synthesizer (40 us settling time)

- On-chip VCO, LNA and PA

- Low core supply voltage (1.6-2.0 V)

- Flexible I/O supply voltage (1.6–3.6 V) to match the signal levels of the interfacing microcontroller

- Programmable output power

- I/Q low-IF receiver

- I/Q direct up-conversion transmitter

- Few external components

- Only reference crystal and a few passives needed

- No external filters needed

- Programmable baseband modem

- 4-wire SPI interface

- Serial clock up to 20 MHz

- Digital RSSI output

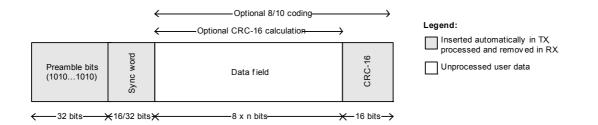

- Packet handling hardware support

- Preamble generator with programmable length

- Programmable synchronization word insertion/detection

- CRC computation over the data field

- 8B/10B line coding option

- Data buffering

- 32 byte FIFO

- Provides for flexible communication with the host controller.

- Burst transmission reduces the average power consumption.

- Powerful and flexible development tools available

- Fully equipped development kit

- Demonstration board reference design with microcontroller code

- Easy-to-use SmartRF Studio software for generating the *CC2400* configuration data

- Small size (QFN 48 package) 7 x 7 mm

- Reference design complies with EN 300 328, EN 300 440, FCC CFR47 part 15 and ARIB STD-T66

# 3 Absolute Maximum Ratings

| Parameter                                       | Min. | Max.                  | Units | Condition |

|-------------------------------------------------|------|-----------------------|-------|-----------|

| Supply voltage, chip core,<br>AVDD/DVDD1.8=VDD  | -0.3 | 2.0                   | V     |           |

| Supply voltage (DVDD3.3=VDDIO), digital I/O     | -0.3 | 3.6                   | V     |           |

| Voltage on any pin, core                        | -0.3 | VDD+0.3,<br>max 2.0   | V     |           |

| Voltage on any pin, digital I/O (pin no. 27-35) | -0.3 | VDDIO+0.3,<br>max 3.6 | V     |           |

| Input RF level                                  |      | 10                    | dBm   |           |

| Storage temperature range                       | -50  | 150                   | °C    |           |

| Reflow solder temperature                       |      | 260                   | °C    | T = 10 s  |

#### NOTE:

The supply voltage to the chip core (AVDD/DVDD1.8) should not be switched off when the digital IO (DVDD3.3) supply voltage is still applied to the chip. If this is done, a large current will flow inside the **CC2400** and the chip may be damaged as a result.

the limiting values may cause permanent

damage to the device.

If the core supply needs to be switched off to lower the power consumption, please see page 17 for a suggested solution.

The absolute maximum ratings given above should under no circumstances be violated. Stress exceeding one or more of

4

**Caution!** ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

**Operating Conditions**

| Parameter                                           | Min. | Тур.          | Max. | Unit | Condition                                                                       |

|-----------------------------------------------------|------|---------------|------|------|---------------------------------------------------------------------------------|

| Supply voltage, chip core,<br>AVDD/DVDD1.8          | 1.6  |               | 2.0  | V    |                                                                                 |

| Supply voltage (DVDD3.3), digital<br>I/O, VDDIO     | 1.6  |               | 3.6  | V    | The digital I/O voltage (DVDD3.3<br>pin) must match the interfacing<br>circuit. |

| Recommended supply voltage, chip core, AVDD/DVDD1.8 |      | 1.8V          |      |      |                                                                                 |

| Recommended supply voltage (DVDD3.3), digital I/O   |      | 1.8V/<br>3.3V |      |      |                                                                                 |

| Operating ambient temperature<br>range              | -40  |               | 85   | °C   |                                                                                 |

# **5** Electrical Specifications

| Parameter                                             | Min. | Тур. | Max. | Unit | Condition / Note                                                     |

|-------------------------------------------------------|------|------|------|------|----------------------------------------------------------------------|

| Current Consumption,<br>Power Down mode (OFF)         |      | 1.5  | 5    | μA   | Oscillator core off                                                  |

| Current Consumption,<br>Idle mode (IDLE)              |      | 1.2  |      | mA   |                                                                      |

| Current Consumption,<br>Frequency synthesizer (FS_ON) |      | 6.3  |      | mA   |                                                                      |

| Current Consumption,<br>Receive mode                  |      | 24   |      | mA   |                                                                      |

| Current Consumption,<br>Transmit mode:                |      |      |      |      |                                                                      |

| P=−25 dBm                                             |      | 11   |      | mA   | The output power is delivered differentially to a $50\Omega$ single- |

| P=−5 dBm                                              |      | 15   |      | mA   | ended load through a balun, see<br>also p. 50.                       |

| P=0 dBm                                               |      | 19   |      | mA   | uiso p. 50.                                                          |

|                                                       |      |      |      |      |                                                                      |

|                                                       |      |      |      |      |                                                                      |

| Current Consumption, crystal<br>oscillator core       |      | 38   |      | μA   | 16 MHz, 16 pF load crystal                                           |

#### **Table 1 Electrical specifications**

# **6** General Characteristics

Tc = 25°C, AVDD/DVDD1.8 = 1.8 V, DVDD3.3 = 3.3V (digital I/O) if nothing else stated. Measured on Chipcon's CC2400EM reference design.

| Parameter          | Min. | Тур.           | Max. | Unit                 | Condition / Note                                        |

|--------------------|------|----------------|------|----------------------|---------------------------------------------------------|

| RF Frequency Range | 2400 |                | 2483 | MHz                  | Programmable in 1 MHz channel steps.                    |

| Data rate          |      | 10<br>250<br>1 |      | kbps<br>kbps<br>Mbps | Data rate is<br>programmable/selectable, see<br>page 40 |

**Table 2 General characteristics**

# 7 **RF Transmit section**

Tc = 25°C, AVDD/DVDD1.8 = 1.8 V, DVDD3.3 = 3.3V (digital I/O) if nothing else stated. Measured on Chipcon's CC2400EM reference design.

| Parameter                                                                             | Min. | Тур.                     | Max.                     | Unit                     | Condition / Note                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------|------|--------------------------|--------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Binary FSK frequency deviation                                                        | 0    | 250                      | 500                      | ±kHz                     | The frequency corresponding to<br>the digital "0" is denoted $f_o$ , while<br>$f_1$ corresponds to a digital "1".<br>The frequency deviation is given<br>by $f_c=\pm(f_1-f_0)/2$ . The RF carrier<br>frequency, $f_c$ , is then given by<br>$f_c=(f_0+f_1)/2$ . |

| Nominal output power                                                                  |      | 0                        |                          | dBm                      | Default settings.<br>Power delivered to a 50 $\Omega$ single-<br>ended load through a balun. The<br>output power is programmable in<br>8 steps.                                                                                                                 |

| Programmable output power range                                                       |      | 25                       |                          | dB                       |                                                                                                                                                                                                                                                                 |

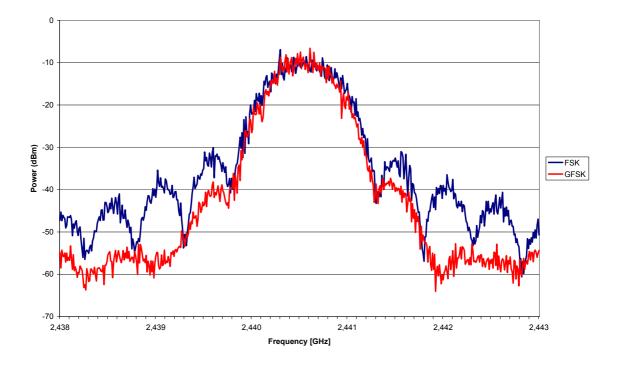

| 20 dB bandwidth<br>FSK<br>GFSK                                                        |      | 1.2<br>1.0               |                          | MHz<br>MHz               | Maximum output power.<br>Modulation is 1 Mbps, NRZ data,<br>± 250 kHz frequency deviation.                                                                                                                                                                      |

| Adjacent Channel Power (ACP)<br>FSK<br>GFSK                                           |      | -30<br>-43               |                          | dBc<br>dBc               | Maximum output power.<br>Modulation is 1 Mbps, NRZ data,<br>± 250 kHz frequency deviation.<br>Measured at 2 MHz offset.                                                                                                                                         |

| Harmonics<br>2 <sup>nd</sup> order harmonic<br>3 <sup>rd</sup> order harmonic         |      | -41<br>-54               |                          | dBm<br>dBm               | At max output power delivered to $50 \Omega$ single-ended load through a balun. Carrier modulated with pseudo-random data. See p.50.                                                                                                                            |

| Spurious emission<br>30 - 1000 MHz<br>1– 12.75 GHz<br>1.8 – 1.9 GHz<br>5.15 – 5.3 GHz |      | -65<br>-41<br>-69<br>-65 | -36<br>-30<br>-47<br>-47 | dBm<br>dBm<br>dBm<br>dBm | Maximum output power.<br>Modulation is 1 Mbps FSK, NRZ<br>data, ±250 kHz frequency<br>deviation.<br>Complying with EN 300 440,<br>CFR47 Part 15 and ARIB STD-<br>T66                                                                                            |

| Optimum load impedance                                                                |      | 110<br>+ j130            |                          | Ω                        | Differential impedance as seen<br>from the RF-port (RF_P and<br>RF_N) towards the antenna. For<br>matching details see "Input/<br>output matching" page 50 as well<br>as the application circuit<br>description on page 17.                                     |

**Table 3 Transmit characteristics**

# 8 **RF Receive section**

Tc = 25°C, AVDD/DVDD1.8 = 1.8 V, DVDD3.3 = 3.3V (digital I/O) if nothing else stated. Measured on Chipcon's CC2400EM reference design.

| CC2400EM reference design. Parameter                                                                                                    | Min. | Тур.                                   | Max. | Unit                                   | Condition / Note                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------|------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receiver Sensitivity at BER = 10 <sup>-3</sup><br>1 Mbps, 1 MHz channel BW<br>250 kbps, 1 MHz channel BW<br>10 kbps, 500 kHz channel BW |      | -87<br>-91<br>-101                     |      | dBm<br>dBm<br>dBm                      | Measured in a 50 Ohm single-<br>ended load through a balun. FSK,<br>NRZ mode used.<br>±250 kHz frequency deviation<br>±250 kHz frequency deviation<br>±125 kHz frequency deviation                                                                                                                                                                              |

| Saturation (maximum input level)                                                                                                        |      | 3                                      |      | dBm                                    | Maximum gain in LNA.<br>NRZ coded data, BER = $10^{-3}$                                                                                                                                                                                                                                                                                                         |

| Co-channel rejection                                                                                                                    |      | -10                                    |      | dB                                     | 1 Mbps wanted signal 10 dB<br>above the sensitivity level,<br>interferer modulated like signal<br>(pseudo-random FSK, $\pm$ 250 kHz<br>deviation), interferer at operating<br>frequency, BER = 10 <sup>-3</sup>                                                                                                                                                 |

| Adjacent channel rejection (ACR)<br>1 Mbps<br>250 kbps                                                                                  |      | 0<br>12                                |      | dB<br>dB                               | FSK wanted signal 10 dB above<br>the sensitivity level, 1 MHz<br>channel spacing, interferer<br>modulated like signal (pseudo-<br>random FSK, $\pm$ 250 kHz<br>deviation) at adjacent channel,<br>BER = 10 <sup>-3</sup>                                                                                                                                        |

| Image channel rejection<br>1 Mbps<br>250 kbps                                                                                           |      | 21<br>39                               |      | dB<br>dB                               | FSK wanted signal 10 dB above<br>the sensitivity level, interferer<br>modulated like signal (pseudo-<br>random FSK, $\pm$ 250 kHz<br>deviation) at image frequency,<br>BER = 10 <sup>-3</sup> . The image channel<br>is centered 2MHz below the<br>center frequency of the desired<br>channel.                                                                  |

| Selectivity (C/I)<br>(In-band channel rejection)<br>+ 2MHz<br>± 3MHz<br>± 4MHz<br>± 5MHz<br>± 10MHz<br>± 20 MHz<br>± 50MHz              |      | 20<br>41<br>50<br>52<br>55<br>56<br>59 |      | dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB | 1Mbps FSK wanted signal at<br>2441 MHz, 3 dB above the<br>sensitivity level (except + 2 MHz,<br>which is 10 dB above the<br>sensitivity limit), jammer<br>modulated like signal (pseudo-<br>random, $\pm$ 250 kHz deviation) at<br>$\pm$ 2-39 MHz in 1 MHz steps<br>offset, BER = 10 <sup>-3</sup> . Adjacent<br>channels and image channel are<br>excluded.    |

| + 2 MHz<br>± 3 MHz<br>± 4 MHz<br>± 5 MHz<br>± 10 MHz<br>± 20 MHz<br>± 50 MHz                                                            |      | 48<br>50<br>55<br>56<br>59<br>60<br>64 |      | dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB | 250 kbps FSK wanted signal at<br>2441 MHz, 3 dB above the<br>sensitivity level (except + 2 MHz,<br>which is 10 dB above the<br>sensitivity limit), jammer<br>modulated like signal (pseudo-<br>random, $\pm$ 250 kHz deviation) at<br>$\pm$ 2-39 MHz in 1 MHz steps<br>offset, BER = 10 <sup>-3</sup> . Adjacent<br>channels and image channel are<br>excluded. |

| Parameter                                                                                                                                            | Min. | Тур.                 | Max.       | Unit                 | Condition / Note                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Blocking / Desensitization*<br>(*out-of-band spurious response<br>rejection)<br>0.3 – 2.0 GHz<br>2.0 – 2.399 GHz<br>2.498 – 3.0 GHz<br>3 – 12.75 GHz |      | 71<br>50<br>49<br>76 |            | dB<br>dB<br>dB<br>dB | 1 Mbps FSK wanted signal 3 dB<br>above the sensitivity level, sine-<br>wave interfering signal, BER =<br>$10^{-3}$ .                                                                                                                                                                                                                                    |

| Input IIP3<br>Out of band<br>In band                                                                                                                 |      | -5<br>-17            |            | dBm<br>dBm           | Measured directly by applying two<br>tones and measuring the<br>resulting difference tone<br>amplitude.                                                                                                                                                                                                                                                 |

| Image frequency suppression                                                                                                                          |      | 56                   |            | dB                   | Ratio between sensitivity for a signal at the image frequency and the sensitivity in the wanted channel with an inverted signal. The image frequency is centered -2 MHz from the center of the wanted channel. The signal source is 1Mbps, NRZ coded data, ±250 kHz frequency deviation, signal level for BER = $10^{-3}$                               |

| Spurious reception                                                                                                                                   |      | 80                   |            | dB                   | Ratio between the sensitivity for<br>an unwanted frequency and the<br>sensitivity in the wanted channel.<br>The signal source is a 1 Mbps,<br>NRZ coded data, $\pm 250$ kHz<br>frequency deviation, swept over<br>all frequencies 2400 – 2483.5<br>MHz. Signal level for BER = 10 <sup>-3</sup><br>Adjacent channels and image<br>channel are excluded. |

| Spurious emission<br>< 1 GHz<br>1 – 12.75 GHz                                                                                                        |      | -70<br>-56           | -57<br>-47 | dBm<br>dBm           | Complying with EN 300 440,<br>CFR47 Part 15 and ARIB STD-<br>T66                                                                                                                                                                                                                                                                                        |

#### Table 4 RF Receive characteristics

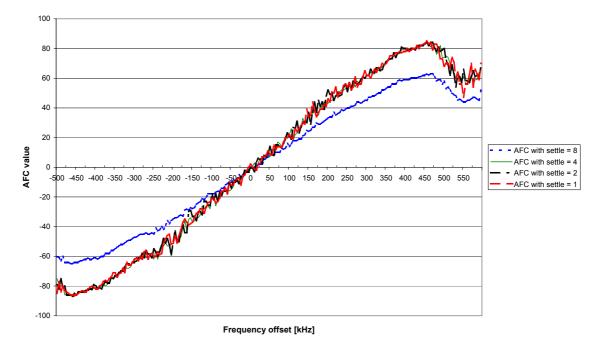

# 9 AFC section

| Parameter    | Min. | Тур.  | Max. | Unit | Condition / Note                                   |

|--------------|------|-------|------|------|----------------------------------------------------|

|              |      |       |      |      | For 1Mbps and 1 MHz channel width, AFC_SETTLING=4. |

| AFC range    |      | ± 500 |      | kHz  | Measured using an unmodulated carrier.             |

| AFC accuracy |      | 5     |      | kHz  |                                                    |

#### Table 5 AFC characteristics

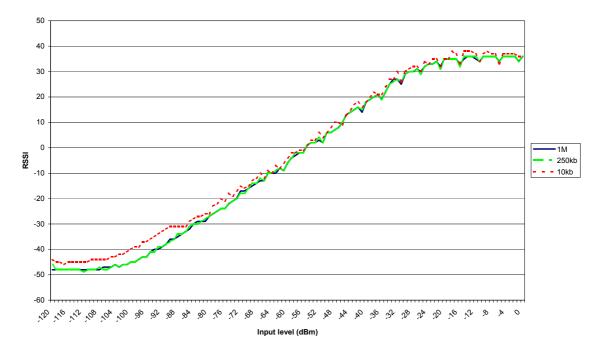

# 10 RSSI / Carrier Sense section

| Parameter                        | Min. | Тур. | Max. | Unit | Condition / Note                                     |

|----------------------------------|------|------|------|------|------------------------------------------------------|

|                                  |      |      |      |      | For 1Mbps and 1 MHz channel width.                   |

| RSSI range / Carrier sense range |      | 80   |      | dB   | (The range is from –100 dBm to<br>–20 dBm typically) |

| RSSI settling time               |      | 20   |      | μs   |                                                      |

| RSSI accuracy                    |      | ± 4  |      | dB   | See page 44 for details                              |

#### Table 6 RSSI / Carrier sense characteristics

# 11 IF section

| Parameter                        | Min. | Тур. | Max. | Unit | Condition / Note                                                                                                                  |

|----------------------------------|------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------|

| Intermediate frequency (IF)      |      | 1    |      | MHz  |                                                                                                                                   |

| Digital channel filter bandwidth | 125  |      | 1000 | kHz  | The digital channel filter 6dB-<br>bandwidth is programmable in<br>steps: 125, 250, 500 and 1000<br>kHz. See page 39 for details. |

### Table 7 IF characteristics

# **12 Frequency Synthesizer section**

| Parameter                                 | Min. | Тур.                 | Max. | Unit                       | Condition / Note                                                                                                                                                                                                      |

|-------------------------------------------|------|----------------------|------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Crystal oscillator frequency              |      | 16                   |      | MHz                        | See page 49 for details.                                                                                                                                                                                              |

| Crystal frequency accuracy<br>requirement |      |                      | 20   | ±ppm                       | The total crystal frequency<br>accuracy, i.e. initial tolerance plus<br>aging and temperature<br>dependency, will determine the<br>frequency accuracy of the<br>transmitted signal. 1 Mbps FSK,<br>250 kHz deviation. |

| Crystal operation                         |      | Parallel             |      |                            | C4 and C5 are loading capacitors, see page 49                                                                                                                                                                         |

| Crystal load capacitance                  | 12   | 16                   | 20   | pF                         | 16 pF recommended                                                                                                                                                                                                     |

| Crystal ESR                               |      |                      | 60   | Ω                          |                                                                                                                                                                                                                       |

| Crystal oscillator start-up time          |      | 1.13                 |      | ms                         | 16 pF load<br>Note: This time can be reduced to<br>15 µs by enabling the XOSC core<br>in power-down using the<br>MANAND register.                                                                                     |

| Phase noise                               |      | -108<br>-114<br>-114 |      | dBc/Hz<br>dBc/Hz<br>dBc/Hz | Unmodulated carrier<br>At ±1 MHz offset from carrier<br>At ±2 MHz offset from carrier<br>At ±5 MHz offset from carrier                                                                                                |

| PLL loop bandwidth                        |      | 50                   |      | kHz                        |                                                                                                                                                                                                                       |

| Parameter                                              | Min. | Тур. | Max. | Unit | Condition / Note                                                                                                                          |

|--------------------------------------------------------|------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| PLL lock time (RX / TX turn-on time)                   |      | 40   |      | μs   | Until within ± 10 kHz<br>Step size is 1MHz, no calibration.<br>Note: Calibration should be<br>performed for frequency changes<br>> 8 MHz. |

| PLL turn-on time from IDLE mode, crystal oscillator on |      | 100  |      | μS   | Crystal oscillator running.<br>Calibration time included.                                                                                 |

Table 8 Frequency synthesizer characteristics

# **13 Digital Inputs/Outputs**

| Parameter                                                    | Min.         | Тур. | Max.         | Unit | Condition / Note                                                                           |

|--------------------------------------------------------------|--------------|------|--------------|------|--------------------------------------------------------------------------------------------|

| Logic "0" input voltage                                      | 0            |      | 0.3*<br>DVDD | v    | Signal levels are referred to the voltage level at the pin DVDD3.3.                        |

| Logic "1" input voltage                                      | 0.7*<br>DVDD |      | DVDD         | V    |                                                                                            |

| Logic "0" output voltage                                     | 0            |      | 0.4          | V    | Output current -8 mA,<br>3.3 V supply voltage                                              |

| Logic "1" output voltage                                     | 2.5          |      | DVDD         | V    | Output current 8 mA,<br>3.3 V supply voltage                                               |

| Logic "0" input current                                      | NA           |      | -1           | μA   | Input signal equals GND                                                                    |

| Logic "1" input current                                      | NA           |      | 1            | μA   | Input signal equals DVDD                                                                   |

| DIO setup time                                               | 20           |      |              | ns   | TX un-buffered mode, minimum<br>time DIO must be ready before<br>the positive edge of DCLK |

| DIO hold time                                                | 10           |      |              | ns   | TX un-buffered mode, minimum<br>time DIO must be held after the<br>positive edge of DCLK   |

| Serial interface (SCLK, SI, SO and CSn) timing specification |              |      |              |      | See Table 12 page 22                                                                       |

Table 9 Digital input/output characteristics

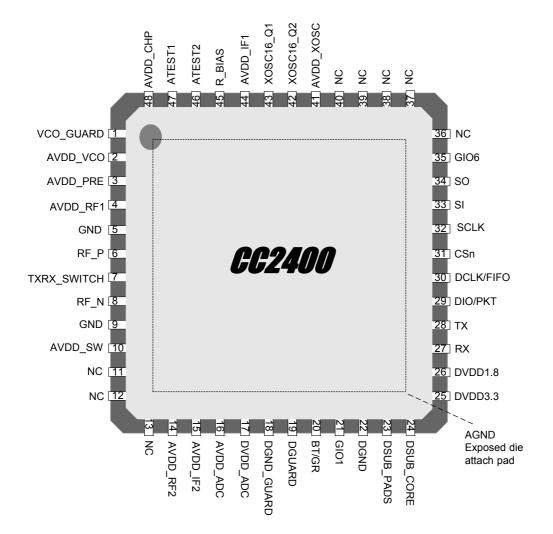

# 14 Pin Assignment

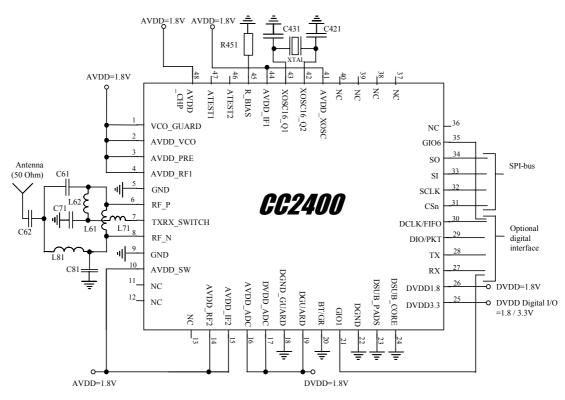

Figure 1 *CC2400* Top View

| Pin no. | Pin name    | Pin type        | Description                                                                                                    |

|---------|-------------|-----------------|----------------------------------------------------------------------------------------------------------------|

| -       | AGND        | Ground (analog) | Exposed die attach pad. <b>Must</b> be connected to solid ground plane                                         |

| 1       | VCO_GUARD   | Power (Analog)  | Connection of guard ring for VCO shielding                                                                     |

| 2       | AVDD_VCO    | Power (Analog)  | Power supply for VCO                                                                                           |

| 3       | AVDD_PRE    | Power (Analog)  | Power supply for Prescaler                                                                                     |

| 4       | AVDD_RF1    | Power (Analog)  | Power supply for RF front-end                                                                                  |

| 5       | GND         | Ground (Analog) | Grounded pin for RF shielding                                                                                  |

| 6       | RF_P        | RF I/O          | Positive RF input/output signal to LNA/from PA in receive/transmit mode                                        |

| 7       | TXRX_SWITCH | Power (Analog)  | Common supply connection for RF front-end. Must be<br>connected to RF_P and RF_N externally through a DC path. |

| 8       | RF_N        | RF I/O          | Negative RF input/output signal to LNA/from PA in receive/transmit mode                                        |

| 9       | GND         | Ground (Analog) | Grounded pin for RF shielding                                                                                  |

| 10      | AVDD_SW     | Power (Analog)  | Power supply connection                                                                                        |

| Pin no. | Pin name   | Pin type         | Description                                                                                                                                         |

|---------|------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 11      | NC         |                  | No Connect                                                                                                                                          |

| 12      | NC         |                  | No Connect                                                                                                                                          |

| 13      | NC         |                  | No Connect                                                                                                                                          |

| 14      | AVDD_RF2   | Power (Analog)   | Power supply for receive and transmit mixers                                                                                                        |

| 15      | AVDD_IF2   | Power (Analog)   | Power supply for transmit IF chain                                                                                                                  |

| 16      | AVDD_ADC   | Power (Analog)   | Power supply connection of ADCs and DACs                                                                                                            |

| 17      | DVDD_ADC   | Power (Digital)  | Power supply for digital part of receive ADCs                                                                                                       |

| 18      | DGND_GUARD | Ground (Digital) | Ground connection for digital noise isolation                                                                                                       |

| 19      | DGUARD     | Power (Digital)  | Power supply connection for digital noise isolation                                                                                                 |

| 20      | BT/GR      | Digital Input    | Selection of Built-in-Test or Generic Radio (normal operation).<br>Connect to ground for normal operation (NOTE: For Chipcon<br>internal use only.) |

| 21      | GIO1       | Digital I/O      | General digital I/O pin. Configure as output when not used.<br>See Table 18                                                                         |

| 22      | DGND       | Ground (Digital) | Ground connection for digital modules                                                                                                               |

| 23      | DSUB_PADS  | Ground (Digital) | Substrate connection for digital I/O's                                                                                                              |

| 24      | DSUB_CORE  | Ground (Digital) | Substrate connection for digital modules                                                                                                            |

| 25      | DVDD3.3    | Power (Digital)  | Power supply for digital I/O's                                                                                                                      |

| 26      | DVDD1.8    | Power (Digital)  | Power supply for digital modules                                                                                                                    |

| 27      | RX         | Digital Input    | Strobe signal for RX mode. Connect to ground when not used.                                                                                         |

| 28      | ТХ         | Digital I/O      | Strobe signal for TX mode. Connect to ground when not used.                                                                                         |

| 29      | DIO/PKT    | Digital I/O      | Data input/output in un-buffered mode or packet handling control signal. Configure as output when not used.                                         |

| 30      | DCLK/FIFO  | Digital Output   | Data clock output signal in un-buffered mode or FIFO control signal. Leave open when not used.                                                      |

| 31      | CSn        | Digital Input    | SPI: Chip Select                                                                                                                                    |

| 32      | SCLK       | Digital Input    | SPI: Serial data clock                                                                                                                              |

| 33      | SI         | Digital Input    | SPI: Slave Input                                                                                                                                    |

| 34      | SO         | Digital Output   | SPI: Slave Output                                                                                                                                   |

| 35      | GIO6       | Digital Output   | General digital output pin. See Table 18                                                                                                            |

| 36      | NC         |                  | No Connect                                                                                                                                          |

| 37      | NC         |                  | No Connect                                                                                                                                          |

| 38      | NC         |                  | No Connect                                                                                                                                          |

| 39      | NC         |                  | No Connect                                                                                                                                          |

| 40      | NC         |                  | No Connect                                                                                                                                          |

| 41      | AVDD_XOSC  | Power (Analog)   | Power supply for 16 MHz crystal oscillator                                                                                                          |

| 42      | XOSC16_Q2  | Analog output    | 16 MHz crystal oscillator                                                                                                                           |

| 43      | XOSC16_Q1  | Analog input     | 16 MHz crystal oscillator or external clock input                                                                                                   |

| 44      | AVDD_IF1   | Power (Analog)   | Power supply connection of receive IF chain                                                                                                         |

| 45      | R_BIAS     | Analog Output    | Connection for external precision bias resistor                                                                                                     |

| 46      | ATEST2     | Analog I/O       | Analog test I/O for prototype and production testing. Leave not connected when not used.                                                            |

| 47      | ATEST1     | Analog I/O       | Analog test I/O for prototype and production testing. Leave not connected when not used.                                                            |

| 48      | AVDD_CHP   | Power (Analog)   | Power supply for phase detector and charge pump                                                                                                     |

#### NOTES:

The exposed die attach pad **must** be connected to a solid ground plane as this is the main ground connection for the chip.

The digital inputs SCLK, SI and CSn are high-impedance inputs (no internal pull-up) and should have external pullups if not driven. RX and TX should have external pull-down if not driven (to prevent the state machine from being trigged). SO is high-impedance when CSn is high. External pull-up should be used at SO to prevent floating input at the microcontroller.

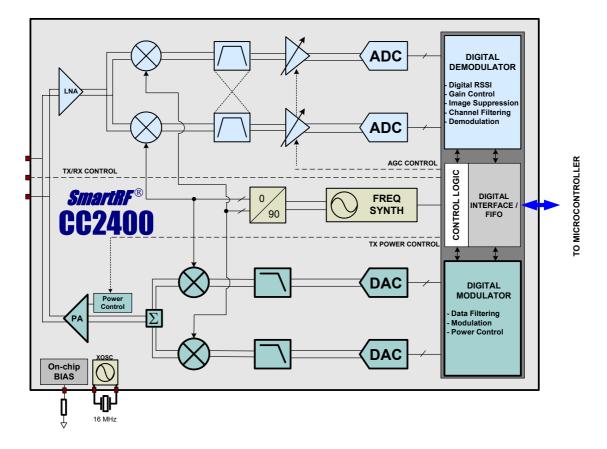

# **15 Circuit Description**

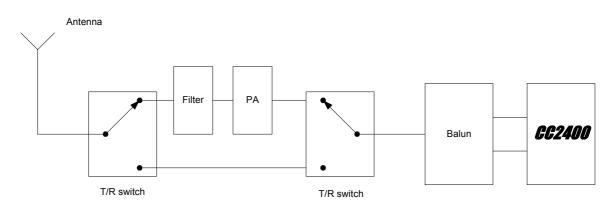

Figure 2. CC2400 simplified block diagram

A simplified block diagram of *CC2400* is shown in Figure 2.

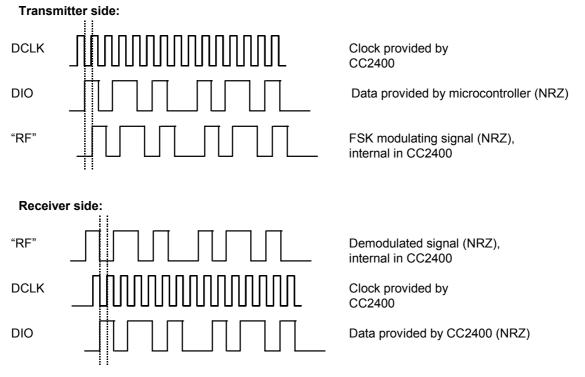

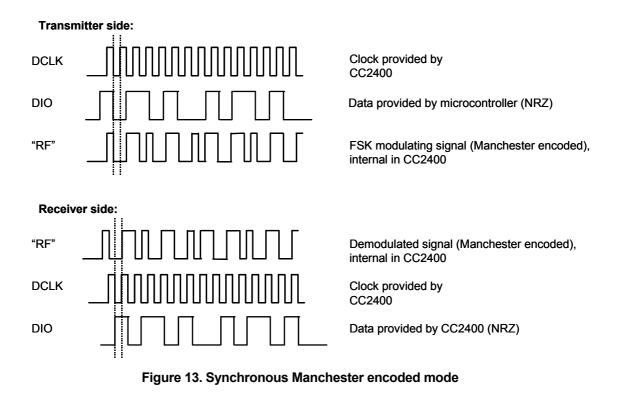

**CC2400** features a low-IF receiver. The received RF signal is amplified by the low-noise amplifier (LNA) and down-converted in quadrature (I and Q) to the intermediate frequency (IF). At IF (1 MHz), the I/Q signal is filtered and amplified, and then digitized by the ADCs. Automatic gain control, final channel filtering, demodulation and bit synchronization is performed digitally.

**CC2400** outputs (in un-buffered mode only) the digital demodulated data on the DIO pin. A synchronized data clock is then available at the DCLK pin. In buffered mode the demodulated data is sent to a FIFO and is accessible through the SPI interface. RSSI is available in digital format and can be read via the serial interface. The RSSI also features a programmable carrier sense indicator with output on either GIO1 or GIO6.

In transmit mode the baseband signal is directly up-converted quadrature (I and Q) and then fed to the power amplifier (PA).

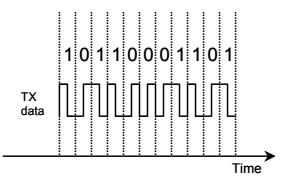

The TX IF signal is frequency shift keyed (FSK). Optionally Gaussian filtering can be used enabling GFSK. The BT of the Gaussian filter is 0.5 for a datarate of 1 Mbps.

The internal T/R switch circuitry simplifies the antenna interface and matching. The antenna connection is differential. The biasing of the PA and LNA is done by connecting TXRX\_SWITCH to RF\_P and RF\_N through an external DC path.

The frequency synthesizer includes a completely on-chip LC VCO and a 90 degrees phase splitter for generating the

LO\_I and LO\_Q signals to the downconversion mixers in receive mode and up-conversion mixers in transmit mode. The VCO operates in the frequency range 4800 – 4966 MHz, and the frequency is divided by two when split in I and Q.

A crystal must be connected to XOSC16\_Q1 and XOSC16\_Q2 and generates the reference frequency for the

synthesizer. A PLL lock signal is available via the GIO pins.

The digital baseband includes support for packet handling and data buffering.

The 4-wire SPI serial interface is used for configuration (and data interface in buffered mode). A few digital I/O lines can be configured for use with packet handling strobe and interrupt signals.

# **16 Application Circuit**

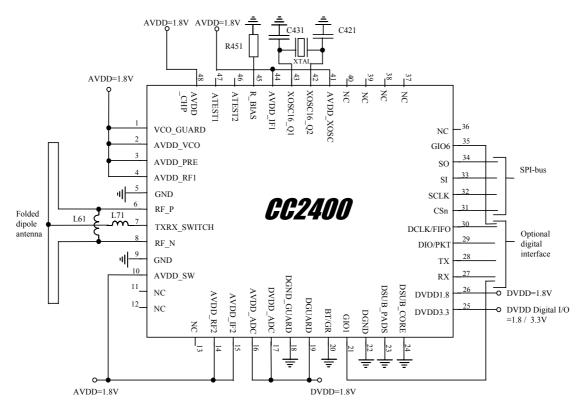

Few external components are required for the operation of *CC2400*. A typical application circuit is shown in Figure 3. A description of the external components referring to Figure 3 are described in Table 10. The bill of materials (BOM) is given in Table 11.

Good PCB layout is vital for proper operation, please see the section on PCB Layout Recommendations on page 56 for more details.

#### 16.1 Input / output matching

The RF input/output is high impedance and differential. The optimum differential load for the RF port is listed on page 8.

When using an unbalanced antenna like a monopole, a balun should be used in order to get optimum performance. The balun can be implemented using low-cost discrete inductors and capacitors. The balun consists of C61, C62, C71, C81, L61, L62 and L72, and will match the RF input/output to 50  $\Omega$ , see Figure 3. L61 and L62 also provide DC biasing of the LNA/PA input/output. L71 is used to isolate the TXRX\_SWITCH pin. An internal T/R switch circuit is used to switch between the LNA and the PA. See "Input/output matching" on page 50 for more details.

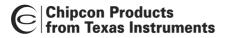

If a balanced antenna, like a folded dipole, is used, the balun can be omitted. If the antenna also provides a DC path from the TXRX\_SWITCH pin to the RF pins, inductors are not needed for DC biasing. The L71 isolation inductor should still be used to avoid antenna reflections. Figure 4 shows a typical application circuit with differential antenna. The dipole has a virtual ground point, hence bias is provided without degradation in antenna performance. Please note that a differential antenna is generally larger than an equivalent single-ended antenna.

#### 16.2 Bias resistor

The bias resistor R451 is used to set an accurate bias current for the chip.

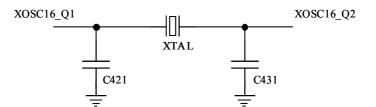

#### 16.3 Crystal

An external crystal with input and output loading capacitors (C421 and C431) is used for the crystal oscillator. See page 49 for details.

#### 16.4 Digital I/O

The supply voltage for the digital I/O must match the interfacing microcontroller. The digital I/Os of **CC2400** can interface microcontrollers with supply voltages in the range 1.6 - 3.6 V.

# 16.5 Power supply decoupling and filtering

Proper power supply decoupling must be used for optimum performance. The placement and size of the decoupling capacitors and the power supply filtering are very important to achieve the best performance in an application. Chipcon provides a compact reference design that should be followed very closely.

#### **16.6** Power supply switching

As described in a note in the Absolute Maximum Ratings section, the voltage supply to the chip core should not be switched off separately from the I/O supply voltage.

If it is necessary to switch the core power supply off, for instance to save the power dissipated in the 1.8V regulator, the I/O supply should be turned off as well. This can be done quite easily by running the I/O supply from a microcontroller I/O pin. Current drawn on the I/O supply is just a few milliamps, so an ordinary I/O pin should have no problems in sourcing this current. Power sequencing should be performed so that both supplies are turned on and off simultaneously.

| Ref  | Description                                        |

|------|----------------------------------------------------|

| C71  | Front-end bias decoupling and match, see page 50   |

| C61  | Discrete balun and match, see page 50              |

| C81  | Discrete balun and match, see page 50              |

| C62  | DC block to antenna and match                      |

| C421 | 16MHz crystal load capacitor, see page 49          |

| C431 | 16MHz crystal load capacitor, see page 49          |

| L61  | DC bias and match, see page 50                     |

| L62  | DC bias and match, see page 50                     |

| L71  | RF blocking inductor, see page 50                  |

| L81  | Discrete balun and match, see page 50              |

| R451 | Precision resistor for current reference generator |

| XTAL | 16MHz crystal, see page 49                         |

Table 10. Overview and description of external components for an unbalanced antenna (balun implemented with low cost discrete components)

Figure 3 Typical application circuit with discrete balun for interfacing single-ended antenna

Figure 4 Typical application circuit with differential antenna (folded dipole)

| Item | Single ended output, discrete balun     | Differential antenna                   |

|------|-----------------------------------------|----------------------------------------|

| C62  | 5.6 pF, +/- 0.25pF, NP0, 0402           | Not used                               |

| C61  | 0.5 pF, +/- 0.25pF, NP0, 0402           | Not used                               |

| C81  | 0.5 pF, +/- 0.25pF, NP0, 0402           | Not used                               |

| C71  | 100 nF, 10%, X5R, 0402                  | 100 nF, 10%, X5R, 0402                 |

| C421 | 18 pF, 5%, NP0, 0402                    | 18 pF, 5%, NP0, 0402                   |

| C431 | 18 pF, 5%, NP0, 0402                    | 18 pF, 5%, NP0, 0402                   |

| L61  | 7.5 nH, 5%, Monolithic/multilayer, 0402 | 27 nH, 5%, Monolithic/multilayer, 0402 |

| L62  | 5.6 nH, 5%, Monolithic/multilayer, 0402 | Not used                               |

| L71  | 27 nH, 5%, Monolithic/multilayer, 0402  | 27 nH, 5%, Monolithic/multilayer, 0402 |

| L81  | 7.5 nH, 5%, Monolithic/multilayer, 0402 | Not used                               |

| R451 | 43 kΩ, 1%, 0402                         | 43 kΩ, 1%, 0402                        |

| XTAL | 16 MHz crystal, 16 pF load (CL)         | 16 MHz crystal, 16 pF load (CL)        |

NOTE: Decoupling components are not included.

Table 11. Bill of materials for the application circuits

CC24NN

\_\_\_\_

### **17 Configuration Overview**

**CC2400** can be configured to achieve optimum performance for different applications. Through the programmable configuration registers the following key parameters can be programmed:

- Receive / transmit mode

- RF frequency

- RF output power

- FSK frequency deviation

- Power-down / power-up mode

#### **18 Configuration Software**

Chipcon provides users of **CC2400** with a software program, SmartRF<sup>®</sup> Studio (Windows interface) that generates all necessary **CC2400** configuration data, based on the user's selections of various parameters. These hexadecimal numbers will then be the necessary input to the

- Crystal oscillator power-up / power down

- Data rate and line coding (NRZ, 8B/10B coding)

- Synthesizer lock indicator mode

- Digital RSSI

- FSK / GFSK modulation

- Data buffering

- Packet handling hardware support

microcontroller for the configuration of **CC2400**.

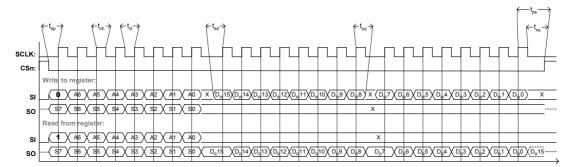

Figure 5 shows the user interface of the *CC2400* configuration software.

| File Settings Help                               |                                                                                                                                                         |          |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------|