**PRELIMINARY**

**DS18B20**

# Programmable Resolution 1-Wire Digital Thermometer

#### **FEATURES**

- Unique 1-Wire<sup>TM</sup> interface requires only one port pin for communication

- Multidrop capability simplifies distributed temperature sensing applications

- Requires no external components

- Can be powered from data line. Power supply range is 3.0V to 5.5V

- Zero standby power required

- Measures temperatures from -55°C to +125°C. Fahrenheit equivalent is -67°F to +257°F

- $\pm 0.5$ °C accuracy from -10°C to +85°C

- Thermometer resolution is programmable from 9 to 12 bits

- Converts 12-bit temperature to digital word in 750 ms (max.)

- User-definable, nonvolatile temperature alarm settings

- Alarm search command identifies and addresses devices whose temperature is outside of programmed limits (temperature alarm condition)

- Applications include thermostatic controls, industrial systems, consumer products, thermometers, or any thermally sensitive system

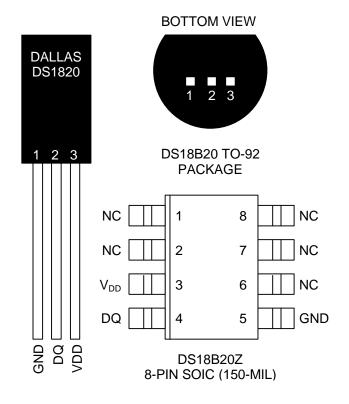

#### PIN ASSIGNMENT

#### PIN DESCRIPTION

GND - Ground

DQ - Data In/Out

V<sub>DD</sub> - Power Supply Voltage

NC - No Connect

#### DESCRIPTION

The DS18B20 Digital Thermometer provides 9 to 12-bit (configurable) temperature readings which indicate the temperature of the device.

Information is sent to/from the DS18B20 over a 1-Wire interface, so that only one wire (and ground) needs to be connected from a central microprocessor to a DS18B20. Power for reading, writing, and performing temperature conversions can be derived from the data line itself with no need for an external power source.

Because each DS18B20 contains a unique silicon serial number, multiple DS18B20s can exist on the same 1-Wire bus. This allows for placing temperature sensors in many different places. Applications where this feature is useful include HVAC environmental controls, sensing temperatures inside buildings, equipment or machinery, and process monitoring and control.

#### **DETAILED PIN DESCRIPTION** Table 1

| PIN       | PIN         |             |                                                                                         |

|-----------|-------------|-------------|-----------------------------------------------------------------------------------------|

| 8PIN SOIC | <b>TO92</b> | SYMBOL      | DESCRIPTION                                                                             |

| 5         | 1           | GND         | Ground.                                                                                 |

| 4         | 2           | DQ          | <b>Data Input/Output pin.</b> For 1-Wire operation: Open drain.                         |

|           |             |             | (See "Parasite Power" section.)                                                         |

| 3         | 3           | $V_{ m DD}$ | <b>Optional V</b> <sub>DD</sub> <b>pin.</b> See "Parasite Power" section for details of |

|           |             |             | connection.                                                                             |

DS18B20Z (8-pin SOIC): All pins not specified in this table are not to be connected.

#### **OVERVIEW**

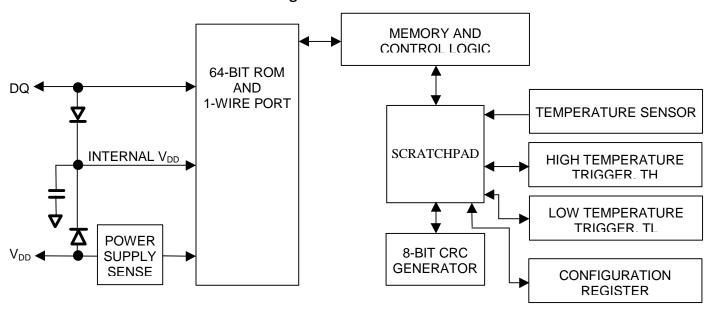

The block diagram of Figure 1 shows the major components of the DS18B20. The DS18B20 has four main data components: 1) 64-bit lasered ROM, 2) temperature sensor, 3) nonvolatile temperature alarm triggers TH and TL, and a configuration register. The device derives its power from the 1-Wire communication line by storing energy on an internal capacitor during periods of time when the signal line is high and continues to operate off this power source during the low times of the 1-Wire line until it returns high to replenish the parasite (capacitor) supply. As an alternative, the DS18B20 may also be powered from an external 3V - 5.5V supply.

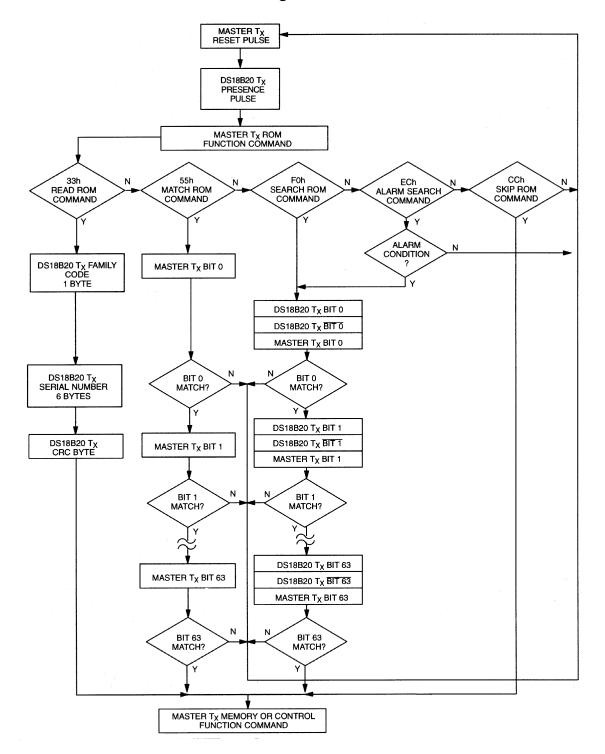

Communication to the DS18B20 is via a 1-Wire port. With the 1-Wire port, the memory and control functions will not be available before the ROM function protocol has been established. The master must first provide one of five ROM function commands: 1) Read ROM, 2) Match ROM, 3) Search ROM, 4) Skip ROM, or 5) Alarm Search. These commands operate on the 64-bit lasered ROM portion of each device and can single out a specific device if many are present on the 1-Wire line as well as indicate to the bus master how many and what types of devices are present. After a ROM function sequence has been successfully executed, the memory and control functions are accessible and the master may then provide any one of the six memory and control function commands.

One control function command instructs the DS18B20 to perform a temperature measurement. The result of this measurement will be placed in the DS18B20's scratch-pad memory, and may be read by issuing a memory function command which reads the contents of the scratchpad memory. The temperature alarm triggers TH and TL consist of 1 byte EEPROM each. If the alarm search command is not applied to the DS18B20, these registers may be used as general purpose user memory. The scratchpad also contains a configuration byte to set the desired resolution of the temperature to digital conversion. Writing TH.TL, and the configuration byte is done using a memory function command. Read access to these registers is through the scratchpad. All data is read and written least significant bit first.

#### **DS18B20 BLOCK DIAGRAM** Figure 1

#### **PARASITE POWER**

The block diagram (Figure 1) shows the parasite-powered circuitry. This circuitry "steals" power whenever the I/O or  $V_{DD}$  pins are high. I/O will provide sufficient power as long as the specified timing and voltage requirements are met (see the section titled "1-Wire Bus System"). The advantages of parasite power are twofold: 1) by parasiting off this pin, no local power source is needed for remote sensing of temperature, and 2) the ROM may be read in absence of normal power.

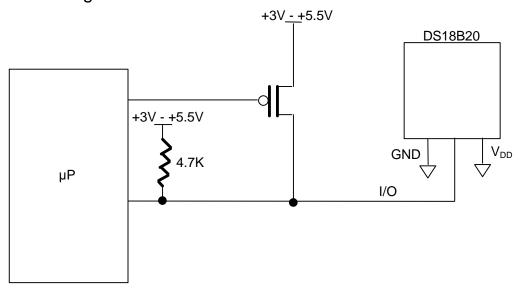

In order for the DS18B20 to be able to perform accurate temperature conversions, sufficient power must be provided over the I/O line when a temperature conversion is taking place. Since the operating current of the DS18B20 is up to 1.5 mA, the I/O line will not have sufficient drive due to the 5k pullup resistor. This problem is particularly acute if several DS18B20s are on the same I/O and attempting to convert simultaneously.

There are two ways to assure that the DS18B20 has sufficient supply current during its active conversion cycle. The first is to provide a strong pullup on the I/O line whenever temperature conversions or copies to the  $E^2$  memory are taking place. This may be accomplished by using a MOSFET to pull the I/O line directly to the power supply as shown in Figure 2. The I/O line must be switched over to the strong pullup within 10  $\mu$ s maximum after issuing any protocol that involves copying to the  $E^2$  memory or initiates temperature conversions. When using the parasite power mode, the  $V_{DD}$  pin must be tied to ground.

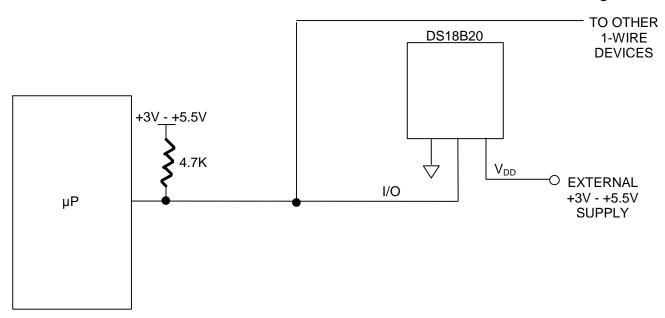

Another method of supplying current to the DS18B20 is through the use of an external power supply tied to the  $V_{DD}$  pin, as shown in Figure 3. The advantage to this is that the strong pullup is not required on the I/O line, and the bus master need not be tied up holding that line high during temperature conversions. This allows other data traffic on the 1-Wire bus during the conversion time. In addition, any number of DS18B20s may be placed on the 1-Wire bus, and if they all use external power, they may all simultaneously perform temperature conversions by issuing the Skip ROM command and then issuing the Convert T command. Note that as long as the external power supply is active, the GND pin may not be floating.

The use of parasite power is not recommended above 100°C, since it may not be able to sustain communications given the higher leakage currents the DS18B20 exhibits at these temperatures. For

applications in which such temperatures are likely, it is strongly recommended that  $V_{DD}$  be applied to the DS18B20.

For situations where the bus master does not know whether the DS18B20s on the bus are parasite powered or supplied with external  $V_{\rm DD}$ , a provision is made in the DS18B20 to signal the power supply scheme used. The bus master can determine if any DS18B20s are on the bus which require the strong pullup by sending a Skip ROM protocol, then issuing the read power supply command. After this command is issued, the master then issues read time slots. The DS18B20 will send back "0" on the 1-Wire bus if it is parasite powered; it will send back a "1" if it is powered from the  $V_{\rm DD}$  pin. If the master receives a "0," it knows that it must supply the strong pullup on the I/O line during temperature conversions. See "Memory Command Functions" section for more detail on this command protocol.

## STRONG PULLUP FOR SUPPLYING DS18B20 DURING TEMPERATURE CONVERSION Figure 2

## USING V<sub>DD</sub> TO SUPPLY TEMPERATURE CONVERSION CURRENT Figure 3

#### **OPERATION - MEASURING TEMPERATURE**

The core functionality of the DS18B20 is its direct-to-digital temperature sensor. The resolution of the DS18B20 is configurable (9, 10, 11, or 12 bits), with 12-bit readings the factory default state. This equates to a temperature resolution of 0.5°C, 0.25°C, 0.125°C, or 0.0625°C. Following the issuance of the Convert T [44h] command, a temperature conversion is performed and the thermal data is stored in the scratchpad memory in a 16-bit, sign-extended two's complement format. The temperature information can be retrieved over the 1-Wire<sup>TM</sup> interface by issuing a Read Scratchpad [BEh] command once the conversion has been performed. The data is transferred over the 1-Wire<sup>TM</sup> bus, LSB first. The MSB of the temperature register contains the "sign" (S) bit, denoting whether the temperature is positive or negative.

Table 2 describes the exact relationship of output data to measured temperature. The table assumes 12-bit resolution. If the DS18B20 is configured for a lower resolution, insignificant bits will contain zeros. For Fahrenheit usage, a lookup table or conversion routine must be used.

## Temperature/Data Relationships Table 2

| $2^3$ | $2^2$ | 2 <sup>1</sup> | $2^0$ | 2-1 | 2-2            | 2-3            | 2-4   | LSB |

|-------|-------|----------------|-------|-----|----------------|----------------|-------|-----|

| MSb   |       |                | (ur   |     | LSb            |                |       |     |

| S     | S     | S              | S     | S   | 2 <sup>6</sup> | 2 <sup>5</sup> | $2^4$ | MSB |

| TEMPERATURE | DIGITAL OUTPUT<br>(Binary) | DIGITAL<br>OUTPUT<br>(Hex) |

|-------------|----------------------------|----------------------------|

| +125°C      | 0000 0111 1101 0000        | 07D0h                      |

| +25.0625°C  | 0000 0001 1001 0001        | 0191h                      |

| +10.125°C   | 0000 0000 1010 0010        | 00A2h                      |

| +0.5°C      | 0000 0000 0000 1000        | 0008h                      |

| 0°C         | 0000 0000 0000 0000        | 0000h                      |

| -0.5°C      | 1111 1111 1111 1000        | FFF8h                      |

| -10.125°C   | 1111 1111 0101 1110        | FF5Eh                      |

| -25.0625°C  | 1111 1110 0110 1111        | FF6Fh                      |

| -55°C       | 1111 1100 1001 0000        | FC90h                      |

#### **OPERATION - ALARM SIGNALING**

After the DS18B20 has performed a temperature conversion, the temperature value is compared to the trigger values stored in TH and TL. Since these registers are 8-bit only, bits 9-12 are ignored for comparison. The most significant bit of TH or TL directly corresponds to the sign bit of the 16-bit temperature register. If the result of a temperature measurement is higher than TH or lower than TL, an alarm flag inside the device is set. This flag is updated with every temperature measurement. As long as the alarm flag is set, the DS18B20 will respond to the alarm search command. This allows many DS18B20s to be connected in parallel doing simultaneous temperature measurements. If somewhere the temperature exceeds the limits, the alarming device(s) can be identified and read immediately without having to read non-alarming devices.

#### 64-BIT LASERED ROM

Each DS18B20 contains a unique ROM code that is 64-bits long. The first 8 bits are a 1-Wire family code (DS18B20 code is 28h). The next 48 bits are a unique serial number. The last 8 bits are a CRC of the first 56 bits. (See Figure 5.) The 64-bit ROM and ROM Function Control section allow the DS18B20 to operate as a 1-Wire device and follow the 1-Wire protocol detailed in the section "1-Wire Bus System." The functions required to control sections of the DS18B20 are not accessible until the ROM function protocol has been satisfied. This protocol is described in the ROM function protocol flowchart (Figure 6). The 1-Wire bus master must first provide one of five ROM function commands: 1) Read ROM, 2) Match ROM, 3) Search ROM, 4) Skip ROM, or 5) Alarm Search. After a ROM functions sequence has been successfully executed, the functions specific to the DS18B20 are accessible and the bus master may then provide and one of the six memory and control function commands.

#### CRC GENERATION

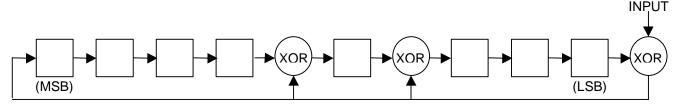

The DS18B20 has an 8-bit CRC stored in the most significant byte of the 64-bit ROM. The bus master can compute a CRC value from the first 56-bits of the 64-bit ROM and compare it to the value stored within the DS18B20 to determine if the ROM data has been received error-free by the bus master. The equivalent polynomial function of this CRC is:

$$CRC = X^8 + X^5 + X^4 + 1$$

The DS18B20 also generates an 8-bit CRC value using the same polynomial function shown above and provides this value to the bus master to validate the transfer of data bytes. In each case where a CRC is used for data transfer validation, the bus master must calculate a CRC value using the polynomial function given above and compare the calculated value to either the 8-bit CRC value stored in the 64-bit ROM portion of the DS18B20 (for ROM reads) or the 8-bit CRC value computed within the DS18B20 (which is read as a ninth byte when the scratchpad is read). The comparison of CRC values and decision to continue with an operation are determined entirely by the bus master. There is no circuitry inside the DS18B20 does not match the value generated by the bus master.

The 1-Wire CRC can be generated using a polynomial generator consisting of a shift register and XOR gates as shown in Figure 7. Additional information about the Dallas 1-Wire Cyclic Redundancy Check is available in Application Note 27 entitled "Understanding and Using Cyclic Redundancy Checks with Dallas Semiconductor Touch Memory Products."

The shift register bits are initialized to 0. Then starting with the least significant bit of the family code, 1 bit at a time is shifted in. After the eighth bit of the family code has been entered, then the serial number is entered. After the 48<sup>th</sup> bit of the serial number has been entered, the shift register contains the CRC value. Shifting in the 8 bits of CRC should return the shift register to all 0s.

## **64-BIT LASERED ROM** Figure 4

| 8-BIT CRC | 8-BIT CRC CODE |     | SERIAL NUMBER | 8-BIT FAMILY CODE (28h) |  |

|-----------|----------------|-----|---------------|-------------------------|--|

| MSB       | LSB            | MSB | LSB M         | MSB LSB                 |  |

## **ROM FUNCTIONS FLOW CHART** Figure 5

## 1-WIRE CRC CODE Figure 6

#### **MEMORY**

The DS18B20's memory is organized as shown in Figure 8. The memory consists of a scratchpad RAM and a nonvolatile, electrically erasable (E²) RAM, which stores the high and low temperature triggers TH and TL, and the configuration register. The scratchpad helps insure data integrity when communicating over the 1-Wire bus. Data is first written to the scratchpad using the Write Scratchpad [4Eh] command. It can then be verified by using the Read Scratchpad [BEh] command. After the data has been verified, a Copy Scratchpad [48h] command will transfer the data to the nonvolatile (E²) RAM. This process insures data integrity when modifying memory.

The scratchpad is organized as eight bytes of memory. The first two bytes contain the LSB and the MSB of the measured temperature information, respectively. The third and fourth bytes are volatile copies of TH and TL and are refreshed with every power-on reset. The fifth byte is a volatile copy of the configuration register and is refreshed with every power-on reset. The configuration register will be explained in more detail later in this section of the datasheet. The sixth, seventh, and eighth bytes are used for internal computations, and thus will not read out any predictable pattern.

It is imperative that one writes TH, TL, and config in succession; i.e. a write is not valid if one writes only to TH and TL, for example, and then issues a reset. If any of these bytes must be written, all three must be written before a reset is issued.

There is a ninth byte which may be read with a Read Scratchpad [BEh] command. This byte contains a cyclic redundancy check (CRC) byte which is the CRC over all of the eight previous bytes. This CRC is implemented in the fashion described in the section titled "CRC Generation".

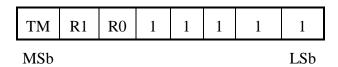

## **Configuration Register**

The fifth byte of the scratchpad memory is the configuration register.

It contains information which will be used by the device to determine the resolution of the temperature to digital conversion. The bits are organized as shown in Figure 7.

## **DS18B20 CONFIGURATION REGISTER** Figure 7

Bits 0-4 are don't cares on a write, but will always read out 1.

**TM:** Test Mode Bit. This EEPROM bit is used to set the DS18B20 in operating or a test mode. It will be set to 0 (operation state) at the Dallas factory, and should not be changed.

**R0, R1:** Thermometer resolution bits. Table 3 below defines the resolution of the digital thermometer, based on the settings of these two bits. There is a direct tradeoff between resolution and conversion time, as depicted in the AC Electrical Characteristics. The factory default of these EEPROM bits is R0=1 and R1=1 (12-bit conversions).

## **Thermometer Resolution Configuration** Table 3

| R1 | R0 | Thermometer<br>Resolution | Max Conversion<br>Time |

|----|----|---------------------------|------------------------|

| 0  | 0  | 9-bit                     | 93.75ms                |

| 0  | 1  | 10-bit                    | 187.5ms                |

| 1  | 0  | 11-bit                    | 375ms                  |

| 1  | 1  | 12-bit                    | 750ms                  |

## **DS18B20 MEMORY MAP** Figure 8

| SCRATCHPAD      | BYTE | $E^2$ RAM      |

|-----------------|------|----------------|

| TEMPERATURE LSB | 0    |                |

| TEMPERATURE MSB | 1    |                |

| TH/USER BYTE 1  | 2    | TH/USER BYTE 1 |

| TL/USER BYTE 2  | 3    | TL/USER BYTE 2 |

| CONFIG          | 4    | CONFIG         |

| RESERVED        | 5    |                |

| RESERVED        | 6    |                |

| RESERVED        | 7    |                |

|                 |      |                |

| CRC             | 8    |                |

#### 1-WIRE BUS SYSTEM

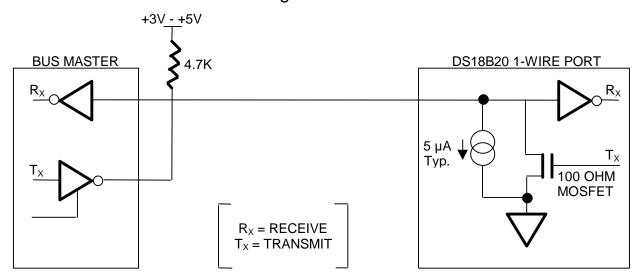

The 1-Wire bus is a system which has a single bus master and one or more slaves. The DS18B20 behaves as a slave. The discussion of this bus system is broken down into three topics: hardware configuration, transaction sequence, and 1-Wire signaling (signal types and timing).

#### HARDWARE CONFIGURATION

The 1-Wire bus has only a single line by definition; it is important that each device on the bus be able to drive it at the appropriate time. To facilitate this, each device attached to the 1-Wire bus must have open drain or 3-state outputs. The 1-Wire port of the DS18B20 (I/O pin) is open drain with an internal circuit equivalent to that shown in Figure 10. A multidrop bus consists of a 1-Wire bus with multiple slaves attached. The 1-Wire bus requires a pullup resistor of approximately  $5k\Omega$ .

#### **HARDWARE CONFIGURATION** Figure 9

The idle state for the 1-Wire bus is high. If for any reason a transaction needs to be suspended, the bus MUST be left in the idle state if the transaction is to resume. Infinite recovery time can occur between bits so long as the 1-Wire bus is in the inactive (high) state during the recovery period. If this does not occur and the bus is left low for more than 480 µs, all components on the bus will be reset.

#### TRANSACTION SEQUENCE

The protocol for accessing the DS18B20 via the 1-Wire port is as follows:

- Initialization

- ROM Function Command

- Memory Function Command

- Transaction/Data

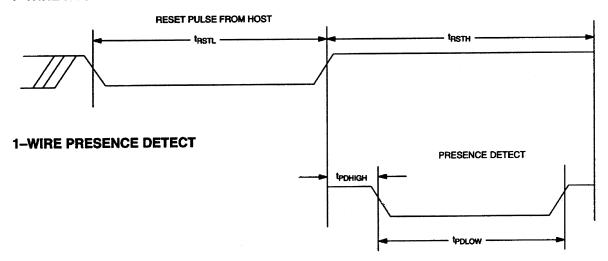

#### INITIALIZATION

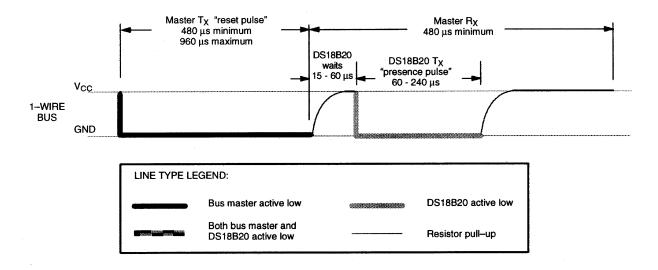

All transactions on the 1-Wire bus begin with an initialization sequence. The initialization sequence consists of a reset pulse transmitted by the bus master followed by presence pulse(s) transmitted by the slave(s).

The presence pulse lets the bus master know that the DS18B20 is on the bus and is ready to operate. For more details, see the "1-Wire Signaling" section.

#### ROM FUNCTION COMMANDS

Once the bus master has detected a presence, it can issue one of the five ROM function commands. All ROM function commands are 8 bits long. A list of these commands follows (refer to flowchart in Figure 6):

### Read ROM [33h]

This command allows the bus master to read the DS18B20's 8-bit family code, unique 48-bit serial number, and 8-bit CRC. This command can only be used if there is a single DS18B20 on the bus. If more than one slave is present on the bus, a data collision will occur when all slaves try to transmit at the same time (open drain will produce a wired AND result).

#### Match ROM [55h]

The match ROM command, followed by a 64-bit ROM sequence, allows the bus master to address a specific DS18B20 on a multidrop bus. Only the DS18B20 that exactly matches the 64-bit ROM sequence will respond to the following memory function command. All slaves that do not match the 64-bit ROM sequence will wait for a reset pulse. This command can be used with a single or multiple devices on the bus.

## Skip ROM [CCh]

This command can save time in a single drop bus system by allowing the bus master to access the memory functions without providing the 64-bit ROM code. If more than one slave is present on the bus and a Read command is issued following the Skip ROM command, data collision will occur on the bus as multiple slaves transmit simultaneously (open drain pulldowns will produce a wired AND result).

## Search ROM [F0h]

When a system is initially brought up, the bus master might not know the number of devices on the 1-Wire bus or their 64-bit ROM codes. The search ROM command allows the bus master to use a process of elimination to identify the 64-bit ROM codes of all slave devices on the bus.

## Alarm Search [ECh]

The flowchart of this command is identical to the Search ROM command. However, the DS18B20 will respond to this command only if an alarm condition has been encountered at the last temperature measurement. An alarm condition is defined as a temperature higher than TH or lower than TL. The alarm condition remains set as long as the DS18B20 is powered up, or until another temperature measurement reveals a non-alarming value. For alarming, the trigger values stored in EEPROM are taken into account. If an alarm condition exists and the TH or TL settings are changed, another temperature conversion should be done to validate any alarm conditions.

#### **Example of a ROM Search**

The ROM search process is the repetition of a simple three-step routine: read a bit, read the complement of the bit, then write the desired value of that bit. The bus master performs this simple, three-step routine on each bit of the ROM. After one complete pass, the bus master knows the contents of the ROM in one device. The remaining number of devices and their ROM codes may be identified by additional passes.

The following example of the ROM search process assumes four different devices are connected to the same 1-Wire bus. The ROM data of the four devices is as shown:

| ROM1 | 00110101 |

|------|----------|

| ROM2 | 10101010 |

| ROM3 | 11110101 |

| ROM4 | 00010001 |

The search process is as follows:

- 1. The bus master begins the initialization sequence by issuing a reset pulse. The slave devices respond by issuing simultaneous presence pulses.

- 2. The bus master will then issue the Search ROM command on the 1-Wire bus.

- 3. The bus master reads a bit from the 1-Wire bus. Each device will respond by placing the value of the first bit of their respective ROM data onto the 1-Wire bus. ROM1 and ROM4 will place a 0 onto the 1-Wire bus, i.e., pull it low. ROM2 and ROM3 will place a 1 onto the 1-Wire bus by allowing the line to stay high. The result is the logical AND of all devices on the line, therefore the bus master sees a 0. The bus master reads another bit. Since the Search ROM data command is being executed, all of the devices on the 1-Wire bus respond to this second read by placing the complement of the first bit of their respective ROM data onto the 1-Wire bus. ROM1 and ROM4 will place a 1 onto the 1-Wire, allowing the line to stay high. ROM2 and ROM3 will place a 0 onto the 1-Wire, thus it will be pulled low. The bus master again observes a 0 for the complement of the first ROM data bit. The bus master has determined that there are some devices on the 1-Wire bus that have a 0 in the first position and others that have a 1.

The data obtained from the two reads of the three-step routine have the following interpretations:

- 00 There are still devices attached which have conflicting bits in this position.

- O1 All devices still coupled have a 0-bit in this bit position.

- All devices still coupled have a 1-bit in this bit position.

- 11 There are no devices attached to the 1-Wire bus.

- 4. The bus master writes a 0. This deselects ROM2 and ROM3 for the remainder of this search pass, leaving only ROM1 and ROM4 connected to the 1-Wire bus.

- 5. The bus master performs two more reads and receives a 0-bit followed by a 1-bit. This indicates that all devices still coupled to the bus have 0s as their second ROM data bit.

- 6. The bus master then writes a 0 to keep both ROM1 and ROM4 coupled.

- 7. The bus master executes two reads and receives two 0-bits. This indicates that both 1-bits and 0-bits exist as the third bit of the ROM data of the attached devices.

- 8. The bus master writes a 0-bit. This deselects ROM1, leaving ROM4 as the only device still connected.

- 9. The bus master reads the remainder of the ROM bits for ROM4 and continues to access the part if desired. This completes the first pass and uniquely identifies one part on the 1-Wire bus.

- 10. The bus master starts a new ROM search sequence by repeating steps 1 through 7.

- 11. The bus master writes a 1-bit. This decouples ROM4, leaving only ROM1 still coupled.

- 12. The bus master reads the remainder of the ROM bits for ROM1 and communicates to the underlying logic if desired. This completes the second ROM search pass, in which another of the ROMs was found.

- 13. The bus master starts a new ROM search by repeating steps 1 through 3.

- 14. The bus master writes a 1-bit. This deselects ROM1 and ROM4 for the remainder of this search pass, leaving only ROM2 and ROM3 coupled to the system.

- 15. The bus master executes two Read time slots and receives two 0s.

- 16. The bus master writes a 0-bit. This decouples ROM3, and leaving only ROM2.

- 17. The bus master reads the remainder of the ROM bits for ROM2 and communicates to the underlying logic if desired. This completes the third ROM search pass, in which another of the ROMs was found.

- 18. The bus master starts a new ROM search by repeating steps 13 through 15.

- 19. The bus master writes a 1-bit. This decouples ROM2, leaving only ROM3.

- 20. The bus master reads the remainder of the ROM bits for ROM3 and communicates to the underlying logic if desired. This completes the fourth ROM search pass, in which another of the ROMs was found.

## Note the following:

The bus master learns the unique ID number (ROM data pattern) of one 1-Wire device on each ROM Search operation. The time required to derive the part's unique ROM code is:

$$960 \mu s + (8 + 3 \times 64) 61 \mu s = 13.16 \text{ ms}$$

The bus master is therefore capable of identifying 75 different 1-Wire devices per second.

#### I/O SIGNALING

The DS18B20 requires strict protocols to insure data integrity. The protocol consists of several types of signaling on one line: reset pulse, presence pulse, write 0, write 1, read 0, and read 1. All of these signals, with the exception of the presence pulse, are initiated by the bus master.

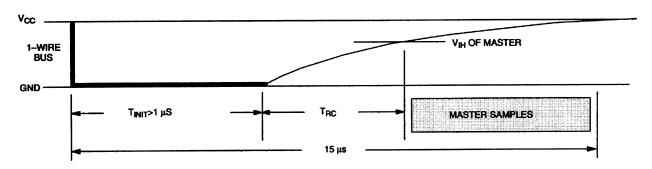

The initialization sequence required to begin any communication with the DS18B20 is shown in Figure 11. A reset pulse followed by a presence pulse indicates the DS18B20 is ready to send or receive data given the correct ROM command and memory function command.

The bus master transmits (TX) a reset pulse (a low signal for a minimum of  $480 \,\mu s$ ). The bus master then releases the line and goes into a receive mode (RX). The 1-Wire bus is pulled to a high state via the 5K pullup resistor. After detecting the rising edge on the I/O pin, the DS18B20 waits 15-60  $\mu s$  and then transmits the presence pulse (a low signal for 60- $240 \,\mu s$ ).

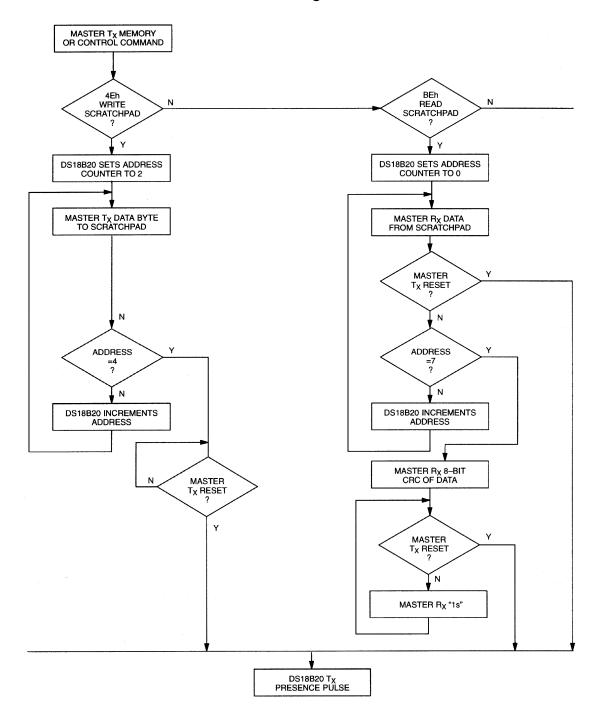

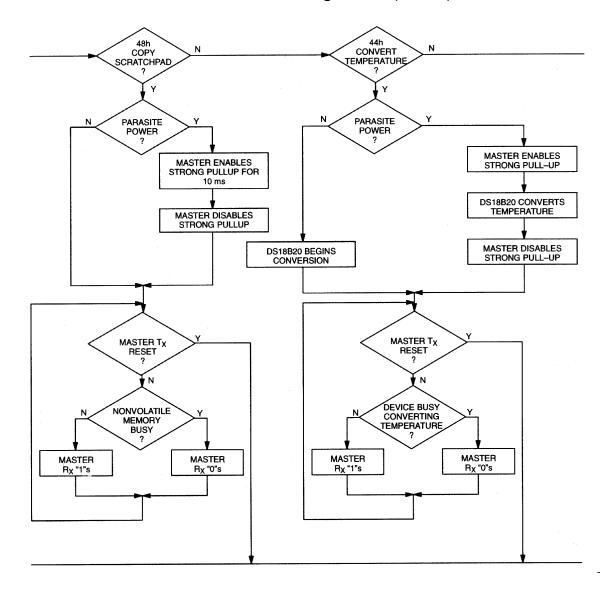

#### **MEMORY COMMAND FUNCTIONS**

The following command protocols are summarized in Table 2, and by the flowchart of Figure 11.

#### Write Scratchpad [4Eh]

This command writes to the scratchpad of the DS18B20, starting at the TH register. The next three bytes written will be saved in scratchpad memory at address locations 2 through 4. All three bytes must be written before a reset is issued.

#### Read Scratchpad [BEh]

This command reads the contents of the scratchpad. Reading will commence at byte 0, and will continue through the scratchpad until the 9<sup>th</sup> (byte 8, CRC) byte is read. If not all locations are to be read, the master may issue a reset to terminate reading at any time.

## Copy Scratchpad [48h]

This command copies the scratchpad into the  $E^2$  memory of the DS18B20, storing the temperature trigger bytes in nonvolatile memory. If the bus master issues read time slots following this command, the DS18B20 will output 0 on the bus as long as it is busy copying the scratchpad to  $E^2$ ; it will return a 1 when the copy process is complete. If parasite-powered, the bus master has to enable a strong pullup for at least 10 ms immediately after issuing this command.

## Convert T [44h]

This command begins a temperature conversion. No further data is required. The temperature conversion will be performed and then the DS18B20 will remain idle. If the bus master issues read time slots following this command, the DS18B20 will output 0 on the bus as long as it is busy making a temperature conversion; it will return a 1 when the temperature conversion is complete. If parasite-powered, the bus master has to enable a strong pullup for 500 ms immediately after issuing this command.

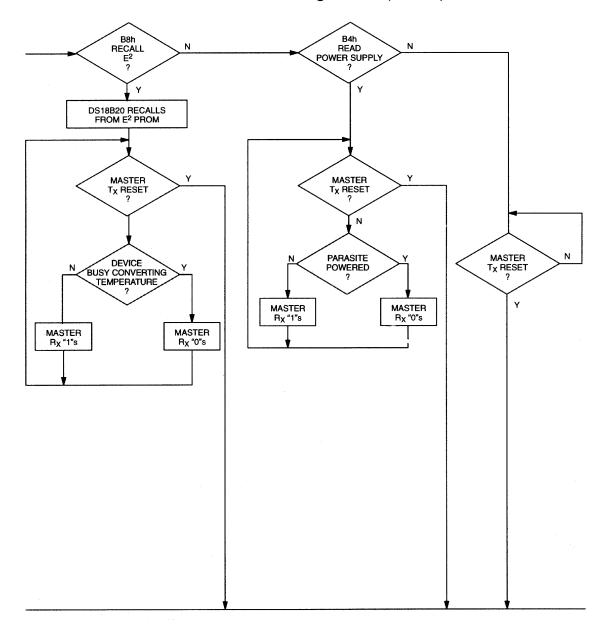

## Recall E2 [B8h]

This command recalls the temperature trigger values and configuration register stored in  $E^2$  to the scratchpad. This recall operation happens automatically upon power-up to the DS18B20 as well, so valid data is available in the scratchpad as soon as the device has power applied. With every read data time slot issued after this command has been sent, the device will output its temperature converter busy flag: 0=busy, 1=ready.

## Read Power Supply [B4h]

With every read data time slot issued after this command has been sent to the DS18B20, the device will signal its power mode: 0=parasite power, 1=external power supply provided.

## **MEMORY FUNCTIONS FLOW CHART** Figure 10

## **MEMORY FUNCTIONS FLOW CHART** Figure 10 (cont'd)

## MEMORY FUNCTIONS FLOW CHART Figure 10 (cont'd)

## **INITIALIZATION PROCEDURE "RESET AND PRESENCE PULSES"** Figure 11

## **DS18B20 COMMAND SET** Table 4

|                       |                                                                                                    |            | 1-WIRE BUS<br>AFTER ISSUING                                               |       |

|-----------------------|----------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------|-------|

| INSTRUCTION           | DESCRIPTION                                                                                        | PROTOCOL   | PROTOCOL                                                                  | NOTES |

| ~                     | TEMPERATURE CO                                                                                     |            |                                                                           |       |

| Convert T             | Initiates temperature                                                                              | 44h        | <read busy<="" td="" temperature=""><td>1</td></read>                     | 1     |

|                       | conversion.                                                                                        |            | status>                                                                   |       |

|                       | MEMOR                                                                                              | Y COMMANDS |                                                                           |       |

| Read Scratchpad       | Reads bytes from scratchpad and reads CRC byte.                                                    | BEh        | <read 9="" bytes="" data="" to="" up=""></read>                           |       |

| Write Scratchpad      | Writes bytes into scratchpad at addresses 2 through 4 (TH and TL temperature triggers and config). | 4Eh        | <write 3="" bytes<br="" data="" into="">at addr. 2 through. 4&gt;</write> | 3     |

| Copy Scratchpad       | Copies scratchpad into nonvolatile memory (addresses 2 through 4 only).                            | 48h        | <read copy="" status=""></read>                                           | 2     |

| Recall E <sup>2</sup> | Recalls values stored in nonvolatile memory into scratchpad (temperature triggers).                | B8h        | <read busy="" status="" temperature=""></read>                            |       |

| Read Power Supply     | Signals the mode of DS18B20 power supply to the master.                                            | B4h        | <read status="" supply=""></read>                                         |       |

#### **NOTES:**

- 1. Temperature conversion takes up to 500 ms. After receiving the Convert T protocol, if the part does not receive power from the  $V_{DD}$  pin, the I/O line for the DS18B20 must be held high for at least 500 ms to provide power during the conversion process. As such, no other activity may take place on the 1-Wire bus for at least this period after a Convert T command has been issued.

- 2. After receiving the Copy Scratchpad protocol, if the part does not receive power from the  $V_{DD}$  pin, the I/O line for the DS18B20 must be held high for at least 10 ms to provide power during the copy process. As such, no other activity may take place on the 1-Wire bus for at least this period after a Copy Scratchpad command has been issued.

- 3. All three bytes must be written before a reset is issued.

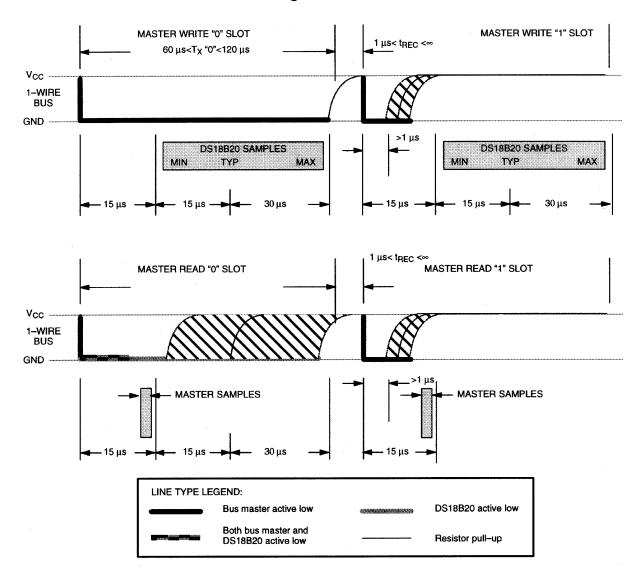

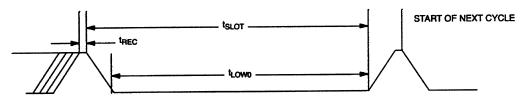

#### READ/WRITE TIME SLOTS

DS18B20 data is read and written through the use of time slots to manipulate bits and a command word to specify the transaction.

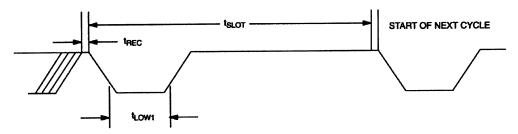

#### Write Time Slots

A write time slot is initiated when the host pulls the data line from a high logic level to a low logic level. There are two types of write time slots: Write 1 time slots and Write 0 time slots. All write time slots must be a minimum of  $60~\mu s$  in duration with a minimum of a 1- $\mu s$  recovery time between individual write cycles.

The DS18B20 samples the I/O line in a window of 15 µs to 60 µs after the I/O line falls. If the line is high, a Write 1 occurs. If the line is low, a Write 0 occurs (see Figure 13).

For the host to generate a Write 1 time slot, the data line must be pulled to a logic low level and then released, allowing the data line to pull up to a high level within 15 µs after the start of the write time slot.

For the host to generate a Write 0 time slot, the data line must be pulled to a logic low level and remain low for 60 µs.

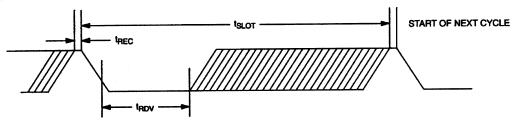

#### Read Time Slots

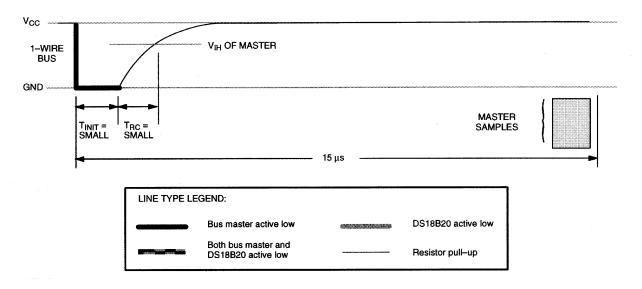

The host generates read time slots when data is to be read from the DS18B20. A read time slot is initiated when the host pulls the data line from a logic high level to logic low level. The data line must remain at a low logic level for a minimum of one  $\mu$ s; output data from the DS18B20 is valid for 15  $\mu$ s after the falling edge of the read time slot. The host therefore must stop driving the I/O pin low in order to read its state 15  $\mu$ s from the start of the read slot (see Figure 12). By the end of the read time slot, the I/O pin will pull back high via the external pullup resistor. All read time slots must be a minimum of 60  $\mu$ s in duration with a minimum of a 1- $\mu$ s recovery time between individual read slots.

Figure 12 shows that the sum of  $T_{INIT}$ ,  $T_{RC}$ , and  $T_{SAMPLE}$  must be less than 15  $\mu$ s. Figure 14 shows that system timing margin is maximized by keeping  $T_{INIT}$  and  $T_{RC}$  as small as possible and by locating the master sample time towards the end of the 15- $\mu$ s period.

## **READ/WRITE TIMING DIAGRAM** Figure 12

## **DETAILED MASTER READ 1 TIMING** Figure 13

## **RECOMMENDED MASTER READ 1 TIMING Figure 14**

#### **Related Application Notes**

The following Application Notes can be applied to the DS18B20. These notes can be obtained from the Dallas Semiconductor "Application Note Book," via our website at http://www.dalsemi.com/, or through our faxback service at (214) 450-0441.

Application Note 27: "Understanding and Using Cyclic Redundancy Checks with Dallas Semiconductor Touch Memory Product"

Application Note 55: "Extending the Contact Range of Touch Memories"

Application Note 74: "Reading and Writing Touch Memories via Serial Interfaces"

Application Note 104: "Minimalist Temperature Control Demo"

Application Note 106: "Complex MicroLANs"

Application Note 108: "MicroLAN - In the Long Run"

Sample 1-Wire subroutines that can be used in conjunction with AN74 can be downloaded from the website or our Anonymous FTP Site.

#### **MEMORY FUNCTION EXAMPLE** Table 5

Example: Bus Master initiates temperature conversion, then reads temperature (parasite power assumed).

| MASTER MODE | DATA (LSB FIRST)             | COMMENTS                                                   |

|-------------|------------------------------|------------------------------------------------------------|

| TX          | Reset                        | Reset pulse (480-960 µs).                                  |

| RX          | Presence                     | Presence pulse.                                            |

| TX          | 55h                          | Issue "Match ROM" command.                                 |

| TX          | <64-bit ROM code>            | Issue address for DS18B20.                                 |

| TX          | 44h                          | Issue "Convert T" command.                                 |

| TX          | <i high="" line="" o=""></i> | I/O line is held high for at least 500 ms by bus master to |

|             |                              | allow conversion to complete.                              |

| TX          | Reset                        | Reset pulse.                                               |

| RX          | Presence                     | Presence pulse.                                            |

| TX          | 55h                          | Issue "Match ROM" command.                                 |

| TX          | <64-bit ROM code>            | Issue address for DS18B20.                                 |

| TX          | BEh                          | Issue "Read Scratchpad" command.                           |

| RX          | <9 data bytes>               | Read entire scratchpad plus CRC; the master now            |

|             |                              | recalculates the CRC of the eight data bytes received      |

|             |                              | from the scratchpad, compares the CRC calculated and       |

|             |                              | the CRC read. If they match, the master continues; if not, |

|             |                              | this read operation is repeated.                           |

| TX          | Reset                        | Reset pulse.                                               |

| RX          | Presence                     | Presence pulse, done.                                      |

## **MEMORY FUNCTION EXAMPLE** Table 6

Example: Bus Master writes memory (parasite power and only one DS18B20 assumed).

| MASTER MODE | DATA (LSB FIRST) | COMMENTS                                                  |

|-------------|------------------|-----------------------------------------------------------|

| TX          | Reset            | Reset pulse.                                              |

| RX          | Presence         | Presence pulse.                                           |

| TX          | CCh              | Skip ROM command.                                         |

| TX          | 4Eh              | Write Scratchpad command.                                 |

| TX          | <3 data bytes>   | Writes three bytes to scratchpad (TH, TL, and config).    |

| TX          | Reset            | Reset pulse.                                              |

| RX          | Presence         | Presence pulse.                                           |

| TX          | CCh              | Skip ROM command.                                         |

| TX          | BEh              | Read Scratchpad command.                                  |

| RX          | <9 data bytes>   | Read entire scratchpad plus CRC. The master now           |

|             |                  | recalculates the CRC of the eight data bytes received     |

|             |                  | from the scratchpad, compares the CRC and the two         |

|             |                  | other bytes read back from the scratchpad. If data match, |

|             |                  | the master continues; if not, repeat the sequence.        |

| TX          | Reset            | Reset pulse.                                              |

| RX          | Presence         | Presence pulse.                                           |

| TX          | CCh              | Skip ROM command.                                         |

| TX          | 48h              | Copy Scratchpad command; after issuing this command,      |

|             |                  | the master must wait 6 ms for copy operation to           |

|             |                  | complete.                                                 |

| TX          | Reset            | Reset pulse.                                              |

| RX          | Presence         | Presence pulse, done.                                     |

#### **ABSOLUTE MAXIMUM RATINGS\***

Voltage on Any Pin Relative to Ground -0.5V to +6.0VOperating Temperature -55°C to +125°C Storage Temperature -55°C to +125°C 260°C for 10 seconds Soldering Temperature

#### RECOMMENDED DC OPERATING CONDITIONS

| PARAMETER      | SYMBOL            | CONDITION   | MIN  | TYP | MAX                  | UNITS | NOTES |

|----------------|-------------------|-------------|------|-----|----------------------|-------|-------|

| Supply Voltage | $V_{ m DD}$       | Local Power | 3.0  |     | 5.5                  | V     | 1     |

| Data Pin       | I/O               |             | -0.5 |     | +5.5                 | V     | 1     |

| Logic 1        | $V_{\mathrm{IH}}$ |             | 2.0  |     | V <sub>CC</sub> +0.3 | V     | 1,2   |

| Logic 0        | $V_{ m IL}$       |             | -0.3 |     | +0.8                 | V     | 1,3   |

#### DC ELECTRICAL CHARACTERISTICS $(-55^{\circ}\text{C to } +125^{\circ}\text{C}; V_{DD}=3.0\text{V to } 5.5\text{V})$

|                    |             |                  |      |     | , -               | , 0   | ,     |

|--------------------|-------------|------------------|------|-----|-------------------|-------|-------|

| PARAMETER          | SYMBOL      | CONDITION        | MIN  | TYP | MAX               | UNITS | NOTES |

| Thermometer Error  | $t_{ERR}$   | -10°C to         |      |     | $\pm \frac{1}{2}$ | °C    |       |

|                    |             | +85°C            |      |     |                   |       |       |

|                    |             | -55°C to         |      |     | . 2               |       |       |

|                    |             | +125°C           |      |     | ±2                |       |       |

| Input Logic High   | $V_{IH}$    |                  | 2.2  |     | 5.5               | V     | 1,2   |

| Input Logic Low    | $V_{ m IL}$ |                  | -0.3 |     | +0.8              | V     | 1,3   |

| Sink Current       | $I_{\rm L}$ | $V_{I/O} = 0.4V$ | -4.0 |     |                   | mA    | 1     |

| Standby Current    | $I_Q$       |                  |      | 200 | 500               | nA    | 7     |

| Active Current     | $I_{DD}$    |                  |      | 1   | 1.5               | mA    | 4,5   |

| Input Load Current | $I_{\rm L}$ |                  |      | 5   |                   | μA    | 6     |

<sup>\*</sup> This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| AC ELECTRICAL CHARACTERISTICS:     | (-55°C to +125°C; V <sub>DD</sub> =3.0V to 5.5V) |

|------------------------------------|--------------------------------------------------|

| AO ELEO INIOAE OHANAO I ENIO 1100. |                                                  |

| PARAMETER            | SYMBOL              | CONDITION     | MIN | TYP | MAX   | UNITS | NOTES |

|----------------------|---------------------|---------------|-----|-----|-------|-------|-------|

| Temperature          | $t_{CONV}$          | 9-bit         |     |     | 93.75 | ms    |       |

| Conversion           |                     | <i>9</i> -01t |     |     | 73.13 | 1115  |       |

| Time                 |                     | 10-bit        |     |     | 187.5 |       |       |

|                      |                     | 11-bit        |     |     | 375   |       |       |

|                      |                     | 12-bit        |     |     | 750   |       |       |

| Time Slot            | $t_{SLOT}$          |               | 60  |     | 120   | μs    |       |

| Recovery Time        | $t_{REC}$           |               | 1   |     |       | μs    |       |

| Write 0 Low Time     | $r_{LOW0}$          |               | 60  |     | 120   | μs    |       |

| Write 1 Low Time     | $t_{LOW1}$          |               | 1   |     | 15    | μs    |       |

| Read Data Valid      | $t_{ m RDV}$        |               |     |     | 15    | μs    |       |

| Reset Time High      | $t_{RSTH}$          |               | 480 |     |       | μs    |       |

| Reset Time Low       | $t_{RSTL}$          |               | 480 |     | 4800  | μs    |       |

| Presence Detect High | t <sub>PDHIGH</sub> |               | 15  |     | 60    | μs    |       |

| Presence Detect Low  | t <sub>PDLOW</sub>  |               | 60  |     | 240   | μs    |       |

| Capacitance          | C <sub>IN/OUT</sub> |               |     |     | 25    | pF    | ·     |

#### **NOTES:**

- 1. All voltages are referenced to ground.

- 2. Logic one voltages are specified at a source current of 1 mA.

- 3. Logic zero voltages are specified at a sink current of 4 mA.

- 4.  $I_{DD}$  specified with  $V_{CC}$  at 5.0 volts.

- 5. Active current refers to either temperature conversion or writing to the  $E^2$  memory. Writing to  $E^2$  memory consumes approximately 200  $\mu A$  for up to 10 ms.

- 6. Input load is to ground.

- 7. Standby current specified up to 70°C. Standby current typically is 5 µA at 125°C.

#### 1-WIRE WRITE ONE TIME SLOT

#### 1-WIRE WRITE ZERO TIME SLOT

#### 1-WIRE READ ZERO TIME SLOT

#### 1-WIRE RESET PULSE

欢迎索取免费详细资料、设计选型指南和光盘、样品;产品繁多未能尽录,欢迎来电查询。

中国传感器科技信息网:HTTP://WWW.SENSOR-IC.COM/

工控安防网:HTTP://WWW.PC-PS.NET/

消费电子专用电路网:HTTP://WWW.SUNSTARE.COM/

E-MAIL: xjr5@163.com szss20@163.com

MSN: suns8888@hotmail.com

QQ: 195847376

地址: 深圳市福田区福华路福庆街鸿图大厦 1602 室 电话: 0755-83376549 83376489 83387030 83387016

传真:0755-83376182 83338339 邮编:518033 手机:(0)13902971329

深圳展销部:深圳华强北路赛格电子市场 2583 号 TEL/FAX:

0755-83665529 25059422

北京分公司:北京海淀区知春路 132 号中发电子大厦 3097 号

TEL: 010-81159046 82615020 13501189838 FAX: 010-82613476 上海分公司:上海市北京东路 668 号上海賽格电子市场 2B35 号

TEL: 021-28311762 56703037 13701955389 FAX: 021-56703037 西安分公司:西安高新开发区 20 所(中国电子科技集团导航技术研究所)

西安劳动南路 88 号电子商城二楼 D23 号

TEL: 029-81022619 13072977981 FAX:029-88789382

成都:TEL:(0)13717066236

技术支持:0755-83394033 13501568376

SUNSTAR商斯达实业集团是集研发、生产、工程、销售、代理经销 、技术咨询、信息服务等为一体的高 科技企业,是专业高科技电子产品生产厂家,是具有10多年历史的专业电子元器件供应商,是中国最早和 最大的仓储式连锁规模经营大型综合电子零部件代理分销商之一,是一家专业代理和分銷世界各大品牌IC 芯片和電子元器件的连锁经营綜合性国际公司。在香港、北京、深圳、上海、西安、成都等全国主要电子 市场设有直属分公司和产品展示展销窗口门市部专卖店及代理分销商,已在全国范围内建成强大统一的供 货和代理分销网络。 我们专业代理经销、开发生产电子元器件、集成电路、传感器、微波光电元器件、工 控机/DOC/DOM电子盘、专用电路、单片机开发、MCU/DSP/ARM/FPGA软件硬件、二极管、三极管、模 块等,是您可靠的一站式现货配套供应商、方案提供商、部件功能模块开发配套商。专业以现代信息产业 (计算机、通讯及传感器)三大支柱之一的传感器为主营业务,专业经营各类传感器的代理、销售生产、 网络信息、科技图书资料及配套产品设计、工程开发。我们的专业网站——中国传感器科技信息网(全球 传感器数据库)www.SENSOR-IC.COM 服务于全球高科技生产商及贸易商,为企业科技产品开发提供技 术交流平台。欢迎各厂商互通有无、交换信息、交换链接、发布寻求代理信息。欢迎国外高科技传感器、 变送器、执行器、自动控制产品厂商介绍产品到 中国,共同开拓市场。本网站是关于各种传感器-变送器-仪器仪表及工业自动化大型专业网站,深入到工业控制、系统工程计 测计量、自动化、安防报警、消费电 子等众多领域, 把最新的传感器-变送器-仪器仪表买卖信息, 最新技术供求, 最新采购商, 行业动态, 发展方 向,最新的技术应用和市场资讯及时的传递给广大科技开发、科学研究、产品设计人员。本网站已成功为 石油、化工、电力、医药、生物、航空、航天、国防、能源、冶金、电子、工业、农业、交通、汽车、矿 山、煤炭、纺织、信息、通信、IT、安防、环保、印刷、科研、气象、仪器仪表等领域从事科学研究、产 品设计、开发、生产制造的科技人员、管理人员 、和采购人员提供满意服务。 我公司专业开发生产、代 理、经销、销售各种传感器、变送器、敏感元器件、开关、执行器、仪器仪表、自动化控制系统: 专门从 事设计、生产、销售各种传感器、变送器、各种测控仪表、热工仪表、现场控制器、计算机控制系统、数 据采集系统、各类环境监控系统、专用控制系统应用软件以及嵌入式系统开发及应用等工作。如热敏电阻、 压敏电阻、温度传感器、温度变送器、湿度传感器、 湿度变送器、气体传感器、 气体变送器、压力传感 器、 压力变送、称重传感器、物(液)位传感器、物(液)位变送器、流量传感器、 流量变送器、电流 (压) 传感器、溶氧传感器、霍尔传感器 、图像传感器、超声波传感器、位移传感器、速度传感器、加速 度传感器、扭距传感器、红外传感器、紫外传感器、 火焰传感器、激光传感器、振动传感器、轴角传感器、 光电传感器、接近传感器、干簧管传感器、继电器传感器、微型电泵、磁敏(阻)传感器 、压力开关、接 近开关、光电开关、色标传感器、光纤传感器、齿轮测速传感器、 时间继电器、计数器、计米器、温控仪、 固态继电器、调压模块、电磁铁、电压表、电流表等特殊传感器。 同时承接传感器应用电路、产品设计 和自动化工程项目。

#### 更多产品请看本公司产品专用销售网站:

商斯达中国传感器科技信息网: http://www.sensor-ic.com/

商斯达工控安防网: http://www.pc-ps.net/

商斯达电子 元器件网: http://www.sunstare.com/

商斯达微波光电产品网:HTTP://www.rfoe.net/

商斯达消费电子产品网://www.icasic.com/

商斯达军工产品网:http://www.junpinic.com/

商斯达实业科技产品网://www.sunstars.cn/传感器销售热线:

地址:深圳市福田区福华路福庆街鸿图大厦 1602 室

电话: 0755-83607652 83376489 83376549 83370250 83370251 82500323

传真: 0755-83376182 (0) 13902971329 MSN: SUNS8888@hotmail.com

邮编: 518033 E-mail:szss20@163.com QQ: 195847376

深圳赛格展销部: 深圳华强北路赛格电子市场 2583 号 电话: 0755-83665529 25059422

技术支持: 0755-83394033 13501568376

欢迎索取免费详细资料、设计指南和光盘 ; 产品凡多,未能尽录,欢迎来电查询。

北京分公司:北京海淀区知春路 132 号中发电子大厦 3097 号

TEL: 010-81159046 82615020 13501189838 FAX: 010-62543996

上海分公司: 上海市北京东路 668 号上海賽格电子市场 D125 号

TEL: 021-28311762 56703037 13701955389 FAX: 021-56703037

西安分公司: 西安高新开发区 20 所(中国电子科技集团导航技术研究所)

西安劳动南路 88 号电子商城二楼 D23 号

TEL: 029-81022619 13072977981 FAX:029-88789382