# MSM9563 IC for FM Multiplex Data Demodulation

# User's Manual [Hardware]

SECOND EDITION ISSUE DATE: Dec. 1999

FEUL9563-02

#### **IMPORTANT NOTICE**

DARC (DAta Radio Channel), an FM multiplex broadcast technology, has been developed by NHK (Japan Broadcasting Corporation). DARC is a registered trademark of NHK Engineering Service (NHK-ES).

Any manufacturer who intends to manufacture/sell products that utilize DARC technology needs to be licensed by NHK-ES.

For detailed information on licenses, please contact: NHK Engineering Service Phone: (+81) 3-3481-2650

DARC (DAta Radio Channel), an FM multiplex broadcast technology, has been developed by NHK (Japan Broadcasting Corporation). DARC is a registered trademark of NHK Engineering Service (NHK-ES). Any manufacturer licensed by NHK-ES can manufacture and sell products that utilize the DARC technology. The products utilizing the DARC technology can be marked with the logotype shown to the left. In the DARC system, 16kbps of digital data L-MSK modulated at 76KHz are multiplied on an ordinary FM broadcast base band signal. An FM multiplex demodulation LSI performs decoding of the digital data signal.

For detailed information on license, please contact: NHK Engineering Service Phone: 81-3-3481-2650 NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 1999 Oki Electric Industry Co., Ltd.

#### TABLE OF CONTENTS

| 1. | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                             | -1                                                                      |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 2. | BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                   | -1                                                                      |

| 3. | PIN INFORMATION33.1PIN CONFIGURATION (TOP VIEW)3.2PIN DESCRIPTIONS3                                                                                                                                                                                                                                                                                                                                             | -1                                                                      |

| 4. | ELECTRICAL CHARACTERISTICS44.1 ABSOLUTE MAXIMUM RATINGS44.2 RECOMMENDED OPERATING CONDITIONS44.3 DC CHARACTERISTICS44.4 AC CHARACTERISTICS44.5 FILTER CHARACTERISTICS44.6 TIMING DIAGRAM4                                                                                                                                                                                                                       | 1<br>1<br>2<br>3<br>4                                                   |

| 5. | CONTROL REGISTERS55.1 OPERATING MODE REGISTERS55.2 INTERRUPT REGISTERS55.3 RECEIVE DATA REGISTERS55.4 TIMING INTERRUPT REGISTERS55.5 CLOCK REGENERATION REGISTERS55.6 BLOCK SYNCHRONIZATION REGISTERS55.7 FRAME SYNCHRONIZATION REGISTERS55.8 ERROR CORRECTION REGISTERS55.9 LAYER 4 CRC REGISTERS55.10 ANALOG TEST REGISTER55.11 POWER DOWN REGISTER55.12 TEST CONTROL REGISTERS55.13 EXTENSION PORT REGISTER5 | 1<br>5<br>7<br>21<br>28<br>30<br>34<br>36<br>38<br>38<br>40<br>41<br>42 |

| 6. | EXTERNAL CONNECTION EXAMPLE                                                                                                                                                                                                                                                                                                                                                                                     | -1                                                                      |

| 7. | APPLICATION CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                             | -1                                                                      |

| AF | PPENDIX: LIST OF REGISTERS                                                                                                                                                                                                                                                                                                                                                                                      | ppendix-1                                                               |

## Chapter 1

# **GENERAL DESCRIPTION**

#### 1. GENERAL DESCRIPTION

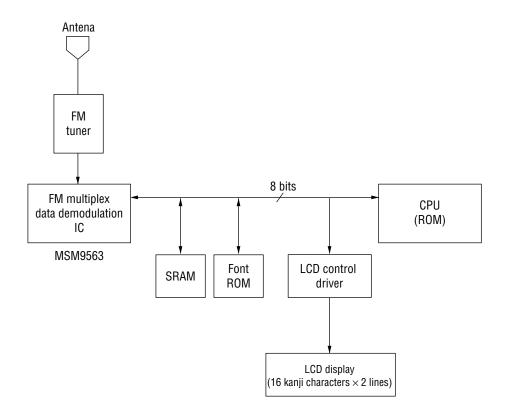

The MSM9563 is an IC which demodulates FM character multiplex signals in the DARC (DAta Radio Channel) format to acquire digital data. This IC operates at 3 V. In the DARC format, baseband signals at ordinary FM broadcasting frequencies are multiplexed with 16 kbps digital data which is L-MSK-modulated at 76 kHz.

The MSM9563 has a bandpass filter consisting of an SCF, frame synchronization circuit, and error correction circuit on a single chip.

They allow a system for acquisition of digital data to be easily constructed by externally mounting an FM receiver tuner, microcontroller for control, and memory for temporary storage of data.

The MSM9563, a FM multiplex demodulator, has a simple configuration, and is equipped with only necessary functions. By making changes to software for the external microcontroller, the MSM9563 meets the various requirements of FM multiplex broadcasting services to be offered in future.

\*1 DARC is a registered trademark of NHK Engineering Services. Any manufacturer licensed by NHK Engineering Service can manufacture and sell products that utilize the DARC technology.

For detailed information on license, please contact: NHK Engineering Service Phone: 81-3481-2650

#### FEATURES

- Built-in two receive channels including main channel and sub-channel (one of two FM stations can be selected)

- Pin compatible with MSM9553 / MSM9555

- Internal frame memory enables automatic error correction.

- Built-in bandpass filter (SCF)

- Built-in block synchronization circuit and frame synchronization circuit

- The number of synchronization protecting steps can be set

- Regeneration of data clocks by digital PLL

- 1T delay detector

- Built-in error correcting circuit (Vertical/Horizontal)

- Built-in layer-4 and layer-2 CRC processing circuit

- International frame formats A (supporting a real time block), B, and C available

- Microcontroller parallel interface

- Clock output for external devices (64 kHz to 8.192 MHz selectable)

- Power source: 2.7 to 3.6 V

- Package: 44-pin plastic QFP (QFP44-P-910-0.80-2K) (Product name: MSM9563GA)

## Chapter 2

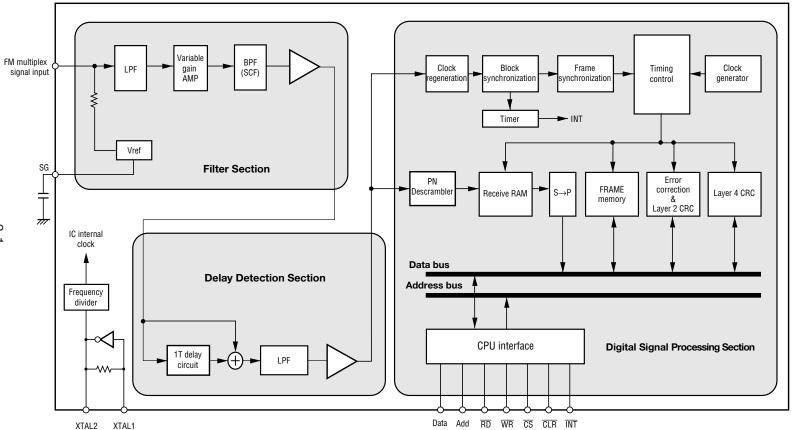

## **BLOCK DIAGRAM**

# **BLOCK DIAGRAM**

Ņ

2-1

## **Chapter 3**

## **PIN INFORMATION**

#### 3. PIN INFORMATION

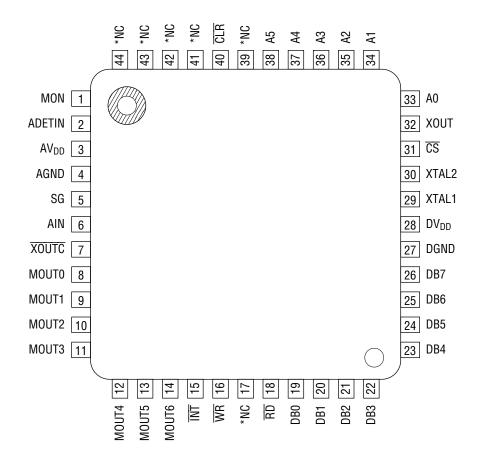

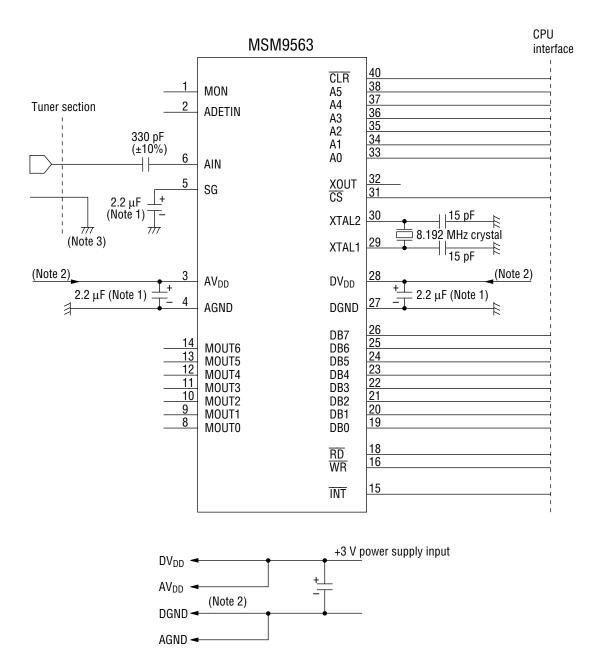

#### 3.1 PIN CONFIGURATION (TOP VIEW)

44-Pin Plastic QFP

Figure 3.1 Pin Layout

\* Leave the NC pins (17, 39, 41, 42, 43, and 44) open.

#### 3.2 PIN DESCRIPTIONS

| Function        | Symbol           | Pin      | Туре | Description                                            |

|-----------------|------------------|----------|------|--------------------------------------------------------|

| Microcontroller | WR               | 16       | I    | Write signal to internal register.                     |

| interface       | RD               | 18       | I    | Read signal to internal register.                      |

|                 | ĪNT              | 15       | 0    | Interrupt signal to microcontroller. When set to       |

|                 |                  |          |      | "L", an interrupt is generated.                        |

|                 | CS               | 31       | I    | Chip select signal. When set to "L", the read, write   |

|                 |                  |          |      | and data bus signals become effective.                 |

|                 | CLR              | 40       | I    | When set to "L", the internal register is initialized, |

|                 |                  |          |      | and the IC enters power down mode.                     |

|                 | A0 to A5         | 33 to 38 | I    | Address signal to internal register.                   |

|                 | DB0 to DB7       | 19 to 26 | I/O  | Data bus signal to internal register.                  |

| Tuner interface | AIN              | 6        | I    | FM multiple signal input.                              |

|                 | SG               | 5        | 0    | Analog reference voltage pin. Connect a                |

|                 |                  |          |      | capacitor between this pin and the analog ground       |

|                 |                  |          |      | pin to prevent noise.                                  |

| Analog section  | MON              | 1        | 0    | Analog section waveform monitoring pin. The            |

| test            |                  |          |      | mode setting for the blocks in the analog section      |

|                 |                  |          |      | is specified by the analog section control register.   |

|                 | ADETIN           | 2        | I    | Analog signal input pin for testing.                   |

| Digital section | MOUT0 to         | 8 to 14  | 0    | Digital section test signal output and monitor         |

| test            | MOUT6            |          |      | output pins.                                           |

| Clock           | XTAL1            | 29       | Ι    | 8.192 MHz crystal connection.                          |

|                 | XTAL2            | 30       | 0    | 8.192 MHz crystal connection.                          |

|                 | XOUT             | 32       | 0    | Pin to supply variable clock (64 kHz to 8.192 MHz)     |

|                 |                  |          |      | to external devices.                                   |

|                 | XOUTC            | 7        | I    | XOUT control. "L" sets XOUT output,                    |

|                 |                  |          |      | "H" sets XOUT output inhibit. This pin is pulled up    |

|                 |                  |          |      | internally.                                            |

| Power supply    | AV <sub>DD</sub> | 3        |      | Analog power supply.                                   |

|                 | AGND             | 4        | _    | Analog ground.                                         |

|                 | DV <sub>DD</sub> | 28       | —    | Digital power supply.                                  |

|                 | DGND             | 27       |      | Digital ground.                                        |

#### Table 3.1 Pin Description

### Chapter 4

# ELECTRICAL CHARACTERISTICS

#### 4. ELECTRICAL CHARACTERISTICS

#### 4.1 ABSOLUTE MAXIMUM RATINGS

| No. | Parameter            | Symbol           | Condition              | Rating                         | Unit |  |

|-----|----------------------|------------------|------------------------|--------------------------------|------|--|

| - 1 | Power cupply voltage | AV <sub>DD</sub> |                        | -0.3 to +7.0                   |      |  |

| -   | Power supply voltage | DV <sub>DD</sub> | $AV_{DD} = DV_{DD}$    | -0.3 10 +7.0                   | v    |  |

| 0   | Input voltage        | VI               | Ta = 25°C              | -0.3 to AV <sub>DD</sub> + 0.3 |      |  |

| 2   | Output voltage       | Vo               |                        | -0.3 to DV <sub>DD</sub> + 0.3 |      |  |

|     | Maximum power        | Р                | Ta = 25°C, per package | 400                            | m\// |  |

| 3   | dissipation          | PD               | Ta = 25°C, per output  | 50                             | mW   |  |

| 4   | Storage temperature  | T <sub>STG</sub> | —                      | -55 to +150                    | °C   |  |

#### 4.2 RECOMMENDED OPERATING CONDITIONS

| No. | Parameter             | Symbol             | Condition                                        | Range               | Unit             | Applied Pin      |

|-----|-----------------------|--------------------|--------------------------------------------------|---------------------|------------------|------------------|

| 1   | Dowar oupply voltage  | $AV_{DD}$          |                                                  | 2.7 to 3.6          | V                | AV <sub>DD</sub> |

| I   | Power supply voltage  | DV <sub>DD</sub>   | $AV_{DD} = DV_{DD}$                              | 2.7 10 3.0          | v                | DV <sub>DD</sub> |

| 2   | Crystal oscillation   | f                  |                                                  | 9 100 MUz . 100 ppm |                  | XTAL1,           |

| Z   | frequency             | † <sub>XTAL</sub>  | _                                                | 8.192 MHz ±100 ppm  |                  | XTAL2            |

|     |                       |                    | Variable amplifier gain: $	imes$ 1               | 0.6 to 0.9          |                  |                  |

| 3   | FM multiplex signal   | V +                | Variable amplifier gain: $\times 1.5$ 0.4 to 0.6 |                     |                  |                  |

| 3   | input voltage         | V <sub>AIN</sub> * | Variable amplifier gain: $	imes$ 2               | 0.3 to 0.4          | V <sub>P-P</sub> | AIN              |

|     |                       |                    | Variable amplifier gain: $	imes$ 3               | 0.2 to 0.3          |                  |                  |

| 4   | Operating temperature | Та                 | —                                                | -40 to +85          | °C               | _                |

\* Peak values (a total voltage of the following signals (a) to (c)) of composite signals including multiplex signals.

(a) Voice signals (100% modulated: voice max.)

(b) Pilot signal

(c) FM multiplex signals (10%: LMSK max.)

The maximum amplitude of an input signal is in the range of 0.9  $V_{\text{P-P}}$  in which the internal IC circuit is not saturated.

Therefore, multiplex singnals of up to 0.9  $V_{P-P}$  can be input if only multiplex signals (excluding composite signals) are input from a signal generator.

#### 4.3 DC CHARACTERISTICS

| No. | Parameter          | Symbol                         | Condition                                                        | Min.                          | Тур. | Max.                 | Unit             | Applied Pin                                                                                                                  |  |

|-----|--------------------|--------------------------------|------------------------------------------------------------------|-------------------------------|------|----------------------|------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | Input veltage      | V <sub>IH</sub>                |                                                                  | $0.8 \times$ DV <sub>DD</sub> |      |                      | V                | WR, RD,<br>XOUTC,<br>DB0 to DB7,                                                                                             |  |

| I   | Input voltage      | VIL                            |                                                                  | _                             | _    | $0.2 \times DV_{DD}$ | V                | $\frac{\overline{\text{CS}}}{\overline{\text{CS}}}, \text{ A0 to A5},$ $\frac{\overline{\text{CLR}}}{\overline{\text{CLR}}}$ |  |

| 2   | Output voltage     | V <sub>OH</sub>                | I <sub>OH</sub> = -1 mA                                          | DV <sub>DD</sub><br>-0.5      |      | _                    | V                | MOUT0 to<br>MOUT6, INT,                                                                                                      |  |

|     |                    | V <sub>OL</sub>                | I <sub>OL</sub> = 2 mA                                           | _                             |      | 0.45                 | V                | DB0 to DB7,<br>XOUT                                                                                                          |  |

| 3   | Input current 1    | I <sub>IH1</sub>               | $V_{IH} = DV_{DD}$                                               |                               |      | 2                    | μA               | WR, RD, CS,<br>DB0 to DB7,                                                                                                   |  |

|     |                    | $I_{IL1}$ $V_{IL} = DGND$ $-2$ |                                                                  |                               | _    | μΛ                   | A0 to A5,<br>CLR |                                                                                                                              |  |

| 4   | Input current 2    | I <sub>IH2</sub>               | $V_{IH} = AV_{DD}$                                               | _                             |      | 2                    | μA               | ADETIN                                                                                                                       |  |

|     |                    | I <sub>IL2</sub>               | V <sub>IL</sub> = AGND                                           | -2                            |      | _                    | μΛ               |                                                                                                                              |  |

| 5   | Input current 3    | I <sub>IH3</sub>               | $V_{IH} = DV_{DD}$                                               | —                             | _    | 2                    | μA               |                                                                                                                              |  |

| 6   | Pull-up current    | I <sub>pull</sub>              | DV <sub>DD</sub> = 3 V,<br>V <sub>IL</sub> = DGND                | 3                             | 15   | 50                   | μA               | XOUTC                                                                                                                        |  |

| 7   | Output off-leakage | I <sub>OH</sub>                | V <sub>OH</sub> = AV <sub>DD</sub><br>During nonmonitoring (Hiz) | _                             |      | 2                    | ۸                | MON                                                                                                                          |  |

| 1   | current            | I <sub>OL</sub>                | V <sub>OL</sub> = AGND<br>During nonmonitoring (Hiz)             | -2                            | —    | _                    | μA               |                                                                                                                              |  |

| 8   | Supply ourrent     |                                | During operation, no load<br>f = 8.192 MHz                       | _                             | 14   | 28                   | mA               |                                                                                                                              |  |

| 0   | Supply current     | I <sub>DD</sub>                | During power down,<br>no load                                    |                               |      | 50                   | μA               | - AV <sub>DD</sub> , DV <sub>DD</sub>                                                                                        |  |

$(DV_{DD} = AV_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{ DGND} = \text{AGND} = 0 \text{ V}, \text{ Ta} = -40 \text{ to } +85^{\circ}\text{C})$

#### 4.4 AC CHARACTERISTICS

|     |                                                     |                      | $(DV_{DD} = AV_{DD} = 2.7)$                                                   | to 3.6 V, | DGND = | AGND = | 0 V, Ta = | -40 to +85°C)                   |

|-----|-----------------------------------------------------|----------------------|-------------------------------------------------------------------------------|-----------|--------|--------|-----------|---------------------------------|

| No. | Parameter                                           | Symbol*              | Condition                                                                     | Min.      | Тур.   | Max.   | Unit      | Applied Pin                     |

|     |                                                     | t <sub>SWR1</sub>    | See figure 4.1                                                                | 3         | _      | _      |           | $\overline{WR}, \overline{CS},$ |

| 1   | Write setup time                                    | t <sub>SWR2</sub>    | See figure 4.1                                                                | 90        |        | _      | ns        | A0 to A5,<br>DB0 to DB7         |

|     |                                                     | t <sub>HWR1</sub>    | See figure 4.1                                                                | -18       | _      | _      |           | $\overline{WR}, \overline{CS},$ |

| 2   | Write hold time                                     | t <sub>HWR2</sub>    | See figure 4.1                                                                | 10        |        | _      | ns        | A0 to A5,<br>DB0 to DB7         |

| 3   | Write pulse width                                   | t <sub>WWR</sub>     | See figure 4.1                                                                | 90        | —      | —      | ns        | WR                              |

| 4   | Read setup time                                     | t <sub>SRD</sub>     | See figure 4.2                                                                | 3         | _      | _      | ns        | RD, CS,<br>A0 to A5             |

| 5   | Read hold time                                      | t <sub>HRD</sub>     | See figure 4.2                                                                | -18       |        | _      | ns        | RD, CS,<br>A0 to A5             |

| 6   | Read pulse width                                    | t <sub>WRD</sub>     | See figure 4.2                                                                | 90        | _      |        | ns        | RD                              |

| 7   | Read data output<br>delay (1)                       | t <sub>DRD1</sub>    | See figure 4.2                                                                | _         | _      | 90     | ns        | RD,<br>DB0 to DB7               |

| 8   | Read data output<br>delay (2)                       | t <sub>DRD2</sub>    | See figure 4.2                                                                | _         |        | 20     | ns        | RD,<br>DB0 to DB7               |

| 9   | Layer 4 data<br>Interval between write<br>and write | t <sub>IWRWR2</sub>  | Layer 4 CRC mode<br>See figure 4.3                                            | 620       |        |        | ns        | WR                              |

| 10  | Layer 4 data<br>Interval between write<br>and read  | t <sub>IWRRD1</sub>  | Layer 4 CRC mode<br>See figure 4.3                                            | 1.2       |        |        | μs        | WR, RD                          |

| 11  | Interval between write and write                    | t <sub>IWRWR</sub>   | See figure 4.4                                                                | 300       |        | _      | ns        | WR                              |

| 12  | Interval between write<br>and write                 |                      | Continuously writing<br>0x3B to 0x3D to the<br>same address<br>See figure 4.5 | 550       |        | _      | ns        | WR                              |

| 13  | Interval between write and read                     | t <sub>IWRRD</sub>   | See figure 4.4                                                                | 300       |        | _      | ns        | $\overline{WR}, \overline{RD}$  |

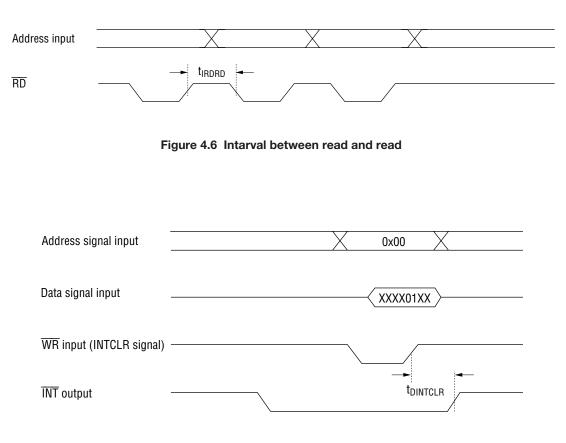

| 14  | Interval between read<br>and read                   | t <sub>IRDRD</sub>   | See figure 4.6                                                                | 300       |        | _      | ns        | RD                              |

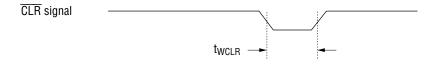

| 15  | Interrupt CLR delay                                 | t <sub>dintclr</sub> | See figure 4.7                                                                | 200       |        | _      | ns        | ÎNT,<br>WR                      |

| 16  | CLR pulse width                                     | twclr                | See figure 4.8                                                                | 200       |        | _      | ns        | CLR                             |

\* See "TIMING DIAGRAM".

#### 4.5 FILTER CHARACTERISTICS

#### $(DV_{DD} = AV_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{ DGND} = \text{AGND} = 0 \text{ V}, \text{ Ta} = -40 \text{ to } +85^{\circ}\text{C})$

| No. | Parameter                      | Symbol | Condition                                               | Min. | Тур. | Max. | Unit | Applied Pin |

|-----|--------------------------------|--------|---------------------------------------------------------|------|------|------|------|-------------|

| 1   | BPF pass band attenuation      | GAIN1  | 72 to 80 kHz<br>Variable gain amplifier<br>gain: 0 dB   |      |      | 3.0  | dB   | MON         |

| 2   | BPF block band attenuation (1) | GAIN2  | 0 to 53 kHz<br>Variable gain amplifier<br>gain: 0 dB    | 50   |      |      | dB   | MON         |

| 3   | BPF block band attenuation (2) | GAIN3  | 100 to 500 kHz<br>Variable gain amplifier<br>gain: 0 dB | 50   |      |      | dB   | MON         |

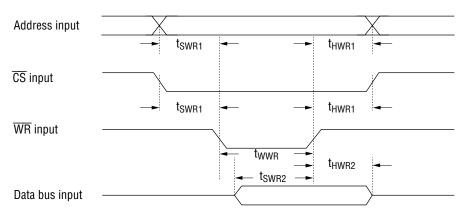

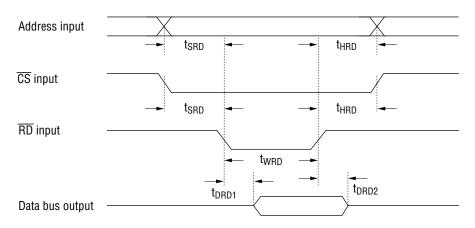

#### 4.6 TIMING DIAGRAM

Figure 4.1 Write Timing

#### MSM9563 User's Manual Chapter 4 ELECTRICAL CHARACTERISTICS

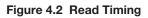

Figure 4.3 Layer 4 CRC mode and Layer 4 VICS mode Timing

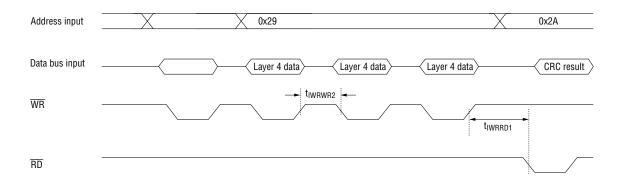

Figure 4.4 Internal between write and write or between write and read

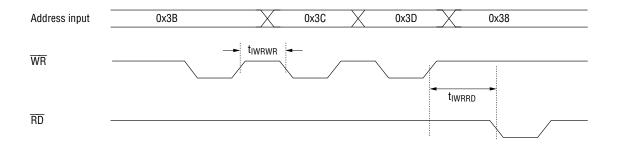

Figure 4.5 When 0x3B to 0x3D are continuously written at the same address (This is a rare case)

#### MSM9563 User's Manual Chapter 4 ELECTRICAL CHARACTERISTICS

Figure 4.8 Clear pulse width

## **Chapter 5**

## CONTROL REGISTERS

#### 5. CONTROL REGISTERS

#### 5.1 OPERATING MODE REGISTERS

#### 5.1.1 Mode setting of main channel and subchannel

#### Table 5.1.1 Main channel mode and subchannel mode

| Address | R/W           | DB7 | DB6 | DB5 | DB4         | DB3 | DB2 | DB1 | DB0          |

|---------|---------------|-----|-----|-----|-------------|-----|-----|-----|--------------|

| 0x04    | W             | —   | —   | _   | MOD_<br>SUB | —   |     | —   | MOD_<br>MAIN |

|         | Initial value | —   | —   |     | 0           | _   | —   | _   | 1            |

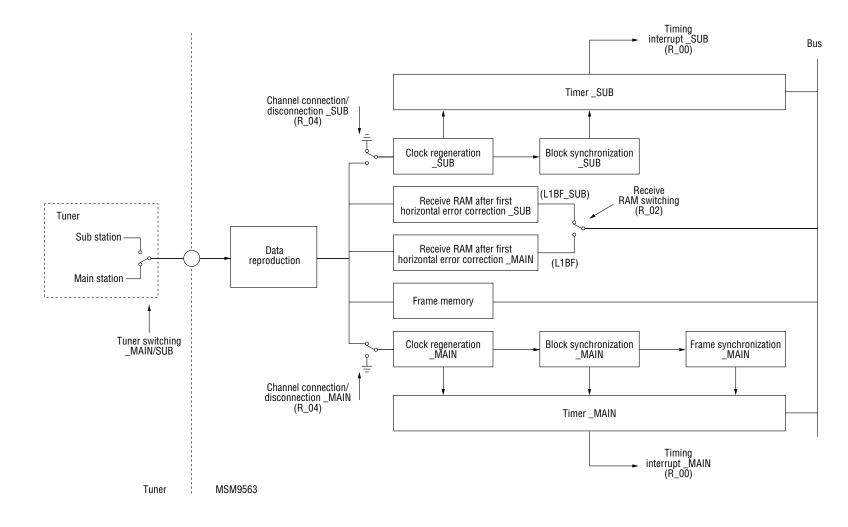

There are two modes available, namely, the main channel mode in which connection is made to the broadcasting station of the same channel and reception is made in units of a frame (the conventional method), and the subchannel mode in which the tuner is switched intermittently to other channels and reception is made in units of several packets of information.

The channel switching mode setting for simultaneously receiving subchannels by switching to high speed subchannel during main channel reception is shown in the following table.

#### Channel switching mode setting for simultaneous reception of main channel and subchannels.

| Mada         | Set v                 | /alue | Description                                                         |

|--------------|-----------------------|-------|---------------------------------------------------------------------|

| Mode         | DB4                   | DB0   | Description                                                         |

| MOD_MAIN/SUB | 1 1 The mode used for |       | The mode used for subchannel timing extraction (at the time of      |

|              |                       |       | initial setting).                                                   |

| MOD_MAIN     | 0                     | 1     | Main channel reception mode                                         |

| MOD_SUB      | 1                     | 0     | Subchannel reception mode                                           |

| MOD_OFF      | 0                     | 0     | The mode used for isolating the synchronization circuit after tuner |

|              |                       |       | switching until the tuning becomes stable.                          |

#### 5.1.2 Frame format

#### Table 5.1.2 Frame format

| Address | R/W           | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---------|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0,45    | W             | —   | —   |     | —   | —   | —   | B1  | B0  |

| 0x1F    | Initial value | _   | _   | _   | _   | _   | _   | 1   | 0   |

| Set v | Set value Fram |               | Symbol | Remarks                               |

|-------|----------------|---------------|--------|---------------------------------------|

| DB1   | DB0            | configuration | Symbol | nemarks                               |

| 0     | 0              | Format A      | A0     |                                       |

| 0     | 1              |               | A1     | Includes real time information blocks |

| 1     | 0              | Format B      | В      | Used in Japan                         |

| 1     | 1              | Format C      | С      |                                       |

#### 5.1.3 Page mode

| Address | R/W           | DB7 | DB6    | DB5 | DB4       | DB3    | DB2  | DB1   | DB0   |

|---------|---------------|-----|--------|-----|-----------|--------|------|-------|-------|

|         | W             | —   | MAINCH | —   | MOD_      | CLRMC0 | MOD_ | PAGE1 | PAGE0 |

| 0x3E    | (Note)        |     | _CLRB  |     | PARITERC2 | _PAGE  | PAGE |       |       |

|         | Initial value | —   | 0      | —   | 0         | 0      | 0    | 0     | 0     |

#### Table 5.1.3 Page mode

Note: The settings MOD\_SUB=1 and MOD\_MAIN=0 should be made in the register 0x04.

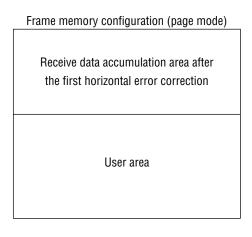

By setting the page mode, it is possible to automatically accumulate the received data after the first horizontal error correction in the frame memory. However, the frame synchronization, vertical error correction, and the second horizontal error correction are not made in the page mode. The frame memory can be divided into the receive data accumulation area after first horizontal error correction and the user area, and the sizes of the two areas are variable. DB3: The received packets are written startig from the packet address "0" if CLRMC0\_PAGE is set to "1".

| Receive data accumulation area after the first horizontal error correction and user area |

|------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------|

| Register 0x3E | Receive data accumulation area              | User area          |  |  |

|---------------|---------------------------------------------|--------------------|--|--|

| set value     | after the first horizontal error correction |                    |  |  |

| 0x04          | Packets 0 to 31                             | Packets 32 to 272  |  |  |

| 0x05          | Packets 0 to 63                             | Packets 64 to 272  |  |  |

| 0x06          | Packets 0 to 127                            | Packets 128 to 272 |  |  |

| 0x07          | Packets 0 to 271                            | Not present        |  |  |

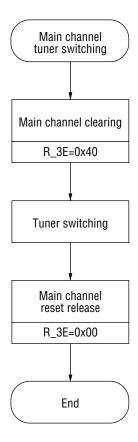

#### 5.1.4 Main channel clear bit (MAINCH\_CLRB)

This MAINCH\_CLRB bit (DB6 of register 0x3E) has been provided to speed up switching to the main channel. When this bit is set to "1" (MAINCH\_CLRB, BIT 6 =1), the main channel synchronization, error correction, internal frame memory control section, and interrupt will be reset.

However, the parameter setting registers, the counter for synchronization, and the pointer for reading out the frame memory are not cleared. Since the reset condition is retained, after switching the tuner, reset this bit to "0" (MAINCH\_CLRB, DB6=0) thereby releasing the reset condition.

Thereafter, reception starts even if the register is not set again.

Although the frame memory is not cleared, the new receive data will be written over the old ones.

#### 5.2 INTERRUPT REGISTERS

#### 5.2.1 Interrupt register

When an interrupt occurs, a "1" is written in this register and the INT Pin is set to the "0" level. After reading out this register, write a "1" in the corresponding bit of this register to clear the interrupt.

| Address | R/W           | DB7                                                                         | DB6             | DB5             | DB4                                                                     | DB3 | DB2                                     | DB1                                                                          | DB0            |

|---------|---------------|-----------------------------------------------------------------------------|-----------------|-----------------|-------------------------------------------------------------------------|-----|-----------------------------------------|------------------------------------------------------------------------------|----------------|

| 0x00    | R             | Receive interrupt<br>after the first<br>horizontal error<br>correction _SUB | TIMINT_<br>SUB  | TIMINT_<br>MAIN | Receive interrupt<br>after the second<br>horizontal error<br>correction |     | Out-of-<br>synchronization<br>interrupt | Receive interrupt<br>after the first<br>horizontal error<br>correction _MAIN | REAL<br>Packet |

|         | W             | Clear interrupt                                                             | Clear interrupt | Clear interrupt | Clear interrupt                                                         | —   | Clear interrupt                         | Clear interrupt                                                              | _              |

|         | Initial value | 0                                                                           | 0               | 0               | 0                                                                       | —   | 0                                       | 0                                                                            | 0              |

| Table 5.2.1 | Interrupt register |

|-------------|--------------------|

|-------------|--------------------|

(1) DB7: Receive interrupt after the first horizontal error correction\_SUB

1: Indicates that a packet was received in a subchannel.

0: There is no interrupt in the subchannels.

- (2) DB6: TIMINT\_SUB

- 1: Indicates that an interrupt set by the subchannel timer has occurred.

- 0: There is no interrupt in the subchannels.

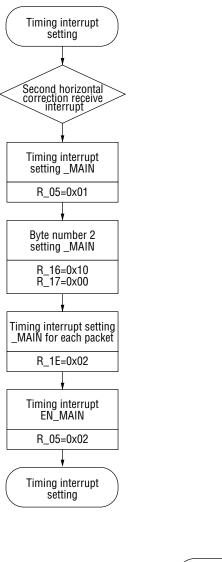

- (3) DB5: TIMINT\_MAIN

- 1: Indicates that an interrupt set by the main channel timer has occurred.

- 0: There is no interrupt in the main channel.

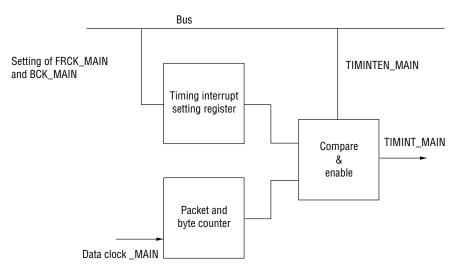

Settings of the registers 0x05, 0x16, 0x17, 0x1D, and 0x1E are necessary to activate the main channel timer interrupt.

- (4) DB4: Receive interrupt after the second horizontal error correction

- 1: Indicates that an interrupt of the frame data reception after the second horizontal error correction of the main channel has occurred.

- 0: There is no interrupt in the main channel.

- (5) DB2: Out-of-synchronization interrupt

- 1: Indicates that an interrupt of frame out-of-synchronization has occurred.

- 0: There is no interrupt in the main channel.

- (6) DB1: Receive interrupt after the first horizontal error correction\_MAIN

- 1: Indicates that a packet was received in the main channel.

- 0: There is no interrupt in the main channel.

#### (7) DB0: REAL

This bit is not an interrupt.

This bit is cleared simultaneously with the receive interrupt after the first horizontal error correction  $\_MAIN$  when a "1" is written in DB1.

- 1: Indicates that the received packet is a REAL packet.

- 0: The received packet is not a REAL packet.

#### 5.2.2 Interrupt mask

This is a register that controls the interrupts corresponding to the bit numbers of the interrupt register (0x00).

#### Table 5.2.2 Interrupt mask

| Address | R/W           | DB7            | DB6            | DB5            | DB4            | DB3 | DB2            | DB1            | DB0 |

|---------|---------------|----------------|----------------|----------------|----------------|-----|----------------|----------------|-----|

| 0x01    | W             | Interrupt mask | Interrupt mask | Interrupt mask | Interrupt mask | —   | Interrupt mask | Interrupt mask | —   |

|         | Initial value | 0              | 0              | 0              | 0              | —   | 0              | 0              | —   |

1: Interrupt enabled.

0: Interrupt disabled.

#### 5.3 RECEIVE DATA REGISTERS

When data is received, that fact is reported by generating an interrupt and setting the  $\overline{INT}$  pin to the "0" level, after which the received data should be read out from the receive data port. The receive data ports are the receive port (0x03) after first horizontal error correction from which data should be read out in units of a packet after the first horizontal error correction has been completed, and the receive port (0x38) after second horizontal error correction has been completed.

#### Receive port after the first horizontal error correction

Since the receive port after the first horizontal error correction is internally separated into one for the main channel and one for the subchnnel, it is necessary to select the required port before reading data. The receive data interrupt after the first horizontal error correction can be set to be enabled or disabled according to the conditions of parity packet, error correction result, service identifier, etc.

#### Receive port after the second horizontal error correction

The receive data of the receive port after the second horizontal error correction is reported by an interrupt at the timing of the 13th packet of the next frame. When all the packets of the frame have been received, the vertical error correction would have been completed. However, the vertical error correction would have been omitted when all the packets in the frame have not been received, such as when frame synchronization is entered in the middle of a frame. The second horizontal error correction is carried out for the packet received under frame synchronization and its result is indicated in register 0x37 by dividing it into four groups as the frame synchronization condition.

The test settings described later are necessary for reading the received data including the parity packet, and in this case, the reception is reported by an interrupt generated at the timing of the 15th packet. Before reading data from the receive port after the second horizontal error correction, it is necessary to set the address pointer (0x3B to 0x3D) and the access mode (0x39) of the frame memory. The address pointer consists of the packet number and the byte number, and specifies the starting address of reading. The setting of the access mode consists of setting the modes of horizontal/vertical reading direction, the parity read, etc., of the frame memory.

The frame data (for example, 190x24 bytes) of the receive port after the second horizontal error correction can be read out either successively or intermittently.

#### 5.3.1 Switching the receive port after the first horizontal error correction

| Address | R/W           | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0           |

|---------|---------------|-----|-----|-----|-----|-----|-----|-----|---------------|

| 0x02    | W             | _   | —   | _   |     |     | _   |     | MAINB/<br>SUB |

|         | Initial value | —   | —   | —   |     |     | —   | —   | 0             |

#### Table 5.3.1 Switching the receive port after the first horizontal error correction

Since the receive port after the first horizontal error correction is connected to the 36-byte RAM for the main channel (LIBF) and the RAM for the subchannel (LIBF\_SUB) (see Figure 5.1), it is necessary to switch between them according to the content of the receive interrupt register. When a value is set in this register, the RAM address pointer is reset and it is possible to read from the leading byte.

DB0: MAINB/SUB

- 1: The receive port after the first horizontal error correction is connected to the RAM (LIBF\_SUB) for the subchannel.

- 0: The receive port after the first horizontal error correction is connected to the RAM (LIBF) for the main channel.

- 5.3.2 Receive port after the first horizontal error correction and the receive data format

| Table 5.3.2.1 | Receive port after the first horizontal error correction |

|---------------|----------------------------------------------------------|

|---------------|----------------------------------------------------------|

| Address | R/W           | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---------|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0x03    | R             | B7  | B6  | B5  | B4  | B3  | B2  | B1  | B0  |

|         | W             | B7  | B6  | B5  | B4  | B3  | B2  | B1  | B0  |

|         | Initial value | —   | —   | —   | —   | —   | —   | —   | _   |

## Read

This is the one-packet receive data port after the first horizontal error correction. The read address of the internal RAM is "0x00" when a receive interrupt after the first horizontal error correction has occurred. When this port is read, the read address is automatically incremented to the next read address and hence it is possible to carry out successive reads.

<u>Write</u>

For testing only. Writing to this port is prohibited during normal use.

| Table 5.3.2.2 | <b>Receive data format after the first horizontal error correction</b> |

|---------------|------------------------------------------------------------------------|

|---------------|------------------------------------------------------------------------|

|          |        |             | Bit No.                                         |        |       |       |        |       |       |  |  |  |

|----------|--------|-------------|-------------------------------------------------|--------|-------|-------|--------|-------|-------|--|--|--|

|          |        | DB7         | DB6                                             | DB5    | DB4   | DB3   | DB2    | DB1   | DB0   |  |  |  |

|          | BYTE0  | CRC0        | ERC0                                            | RECCRC | FSYNC | BSYNC | BICDET | BIC1  | BICO  |  |  |  |

| -        | BYTE1  | VICSRDY     | PARITY                                          | INT0   | 0     | 0     | FNCHG  | FRN01 | FRN00 |  |  |  |

|          | BYTE2  | First horiz | First horizontal correction receive data No. 0  |        |       |       |        |       |       |  |  |  |

|          | :      |             | :                                               |        |       |       |        |       |       |  |  |  |

|          | :      |             | :                                               |        |       |       |        |       |       |  |  |  |

| Byte No. | BYTE23 | First horiz | First horizontal correction receive data No. 21 |        |       |       |        |       |       |  |  |  |

| -        | BYTE24 | CRC         |                                                 |        |       |       |        |       |       |  |  |  |

|          | BYTE25 | PARITY      |                                                 | CRC    |       |       |        |       |       |  |  |  |

|          | BYTE26 | PARITY      |                                                 |        |       |       |        |       |       |  |  |  |

| -        | :      | :           |                                                 |        |       |       |        |       |       |  |  |  |

|          | BYTE35 | PARITY      |                                                 |        |       |       |        |       |       |  |  |  |

BYTE0 and BYTE1 of the receive RAM data after the first horizontal error correction indicate the status of the received packet, BYTE2 to BYE23 are data, and BYTE 24 to BYTE 35 are the CRC/ parity data.

BYTE24 to BYTE35 are for testing and cannot be read out.

<u>BYTE0</u> (1) DB7: CRC0

- 1: Indicates that there is an error in the CRC of the packet after the first horizontal error correction.

- 0: Indicates that the CRC of the packet is normal after the first horizontal error correction.

- (2) DB6: ERC0

- 1: Indicates that there is an error in the correction result of the packet after the first horizontal error correction.

- 0: Indicates that the correction result of the packet is normal after the first horizontal error correction.

- (3) DB5: RECCRC

Indicates that there is an error in the CRC of the received packet before error correction.

Indicates that the CRC of the received packet is normal before error correction.

- (4) DB4: FSYNC

- 1: Indicates that the received packet is in a frame synchronization state.

- 0: Indicates that the received packet is in a frame out-of-synchronizaiton state.

- (5) DB3: BSYNC

- 1: Indicates that the received packet is in a block synchronization state.

- 0: Indicates that the received packet is in a block out-of-synchronization state.

- (6) DB2 to DB0: BIC Data

Indicate the detection condition of the block identification code (BIC).

| DB2 | DB1 | DB0 | BIC No.      |

|-----|-----|-----|--------------|

| 1   | 0   | 0   | 1            |

| 1   | 0   | 1   | 2            |

| 1   | 1   | 0   | 3            |

| 1   | 1   | 1   | 4            |

| 0   | _   |     | Not detected |

BYTE1

(1) DB7: VICSRDY

- 1: Indicates that the received packet is a VICS packet.

- 0: Indicates that the received packet is not a VICS packet.

- (2) DB6: PARITY

This bit indication is made only in a frame synchronization state.

- 1: Indicates that the received packet is a parity packet.

- 0: Indicates that the received packet is not a parity packet.

(3) DB5: INT0

This bit indicates the receive interrupt after the first horizontal error correction. Even though this bit indication is made in the reception condition after the second horizontal correction, it is possible to confirm that reading has been made when a receive interrupt has occurred after the first horizontal error correction.

- 1: Indicates that the received packet is one in which the receive interrupt occurred after the first horizontal error correction.

- 0: Indicates that the received packet is one in which no receive interrupt occurred after the first horizontal error correction.

- (4) DB4, DB3: "0" fixed

- (5) DB2: FNCHG

This bit indication is made only in a frame synchronization state.

- 1: Indicates that the packet is one given in the following table.

- 0: Indicates that the packet is one other than those indicated in the following table.

| Frame format                              |                                           |  |  |  |  |  |  |  |

|-------------------------------------------|-------------------------------------------|--|--|--|--|--|--|--|

| Format B                                  | Format A1, A0                             |  |  |  |  |  |  |  |

| Packet with a block number of 0, 13, 136, | Packet with a block number of 0, 60, 130, |  |  |  |  |  |  |  |

| or 149.                                   | or 190.                                   |  |  |  |  |  |  |  |

Note: The packet numbers are expressed in this manual as 0 to 271 (A1: 0 to 283).

### (6) DB1, DB0: FRNO1, FRNO0

These bit indications are made only in a frame synchronization state. These bits indicate that the packet is one with the block numbers given in the following table.

|     |     | Frame format                              |                                          |                                          |  |  |  |  |

|-----|-----|-------------------------------------------|------------------------------------------|------------------------------------------|--|--|--|--|

| DB1 | DB0 | Format B                                  |                                          | Format A1, A0                            |  |  |  |  |

| 0   | 0   | Packet with a block number of 0 to 12.    | Packet with a block number of 0 to 59    |                                          |  |  |  |  |

| 0   | 1   | Packet with a block number of 13 to 135.  | Packet with a block number of 60 to 129  |                                          |  |  |  |  |

| 1   | 0   | Packet with a block number of 136 to 148. | Packet with a block number of 130 to 189 |                                          |  |  |  |  |

| 1   | 1   | Packet with a block number of 149 to 271. | A0                                       | Packet with a block number of 190 to 271 |  |  |  |  |

|     |     |                                           | A1                                       | Packet with a block number of 190 to 283 |  |  |  |  |

Note: The packet numbers are expressed in this manual as 0 to 271 (A1: 0 to 283).

5.3.3 Conditions of receive interrupt after the first horizontal error correction

| Address | R/W           | DB7   | DB6    | DB5  | DB4  | DB3    | DB2     | DB1  | DB0   |

|---------|---------------|-------|--------|------|------|--------|---------|------|-------|

|         | W             | MOD_  | MOD_CH | MOD_ | MOD_ | MOD_   | MOD_    | MOD_ | SISEL |

| 0x34    |               | FSYNC | OFFDET | INTO | ERC0 | PARIT0 | BICDETO | SI   |       |

|         | Initial value | 0     | 0      | 1    | 0    | 0      | 0       | 0    | 0     |

### Table 5.3.3.1 Conditions of receive interrupt after the first horizontal error correction

This is the register for setting the conditions of interrupt after the first horizontal error correction. During the initial setting, all packets received in a synchronization state are set to generate an interrupt. It is possible to specify the four types of interrupt conditions shown in the following table regarding good (error-free) packets, frame synchronization, and specified SI (service identifier). It is possible to specify 16 types of service identifiers (SI0 to SI15) for which it is necessary to set this register and the register 0x35.

The packets that generated an interrupt after the first horizontal error correction are recorded in the frame memory (Receiving state 1 DB5 (INT0)) after the second horizontal error correction. Therefore, there is no need to read out good packets after the first horizontal error correction after the second horizontal error correction.

# Table 5.3.3.2 Interrupt conditions after the first horizontal error correction

|   | Interrupt condition                              | Set value | Set value of 0x35                     |

|---|--------------------------------------------------|-----------|---------------------------------------|

|   |                                                  | of 0x34   |                                       |

| 1 | All packets received in a synchronization state  | 0x20      | —                                     |

| 2 | Good packets received in a synchronization state | 0x70      | —                                     |

| 3 | Packets in a frame synchronization state         | 0xA0      | —                                     |

|   | (including bad packets)                          |           |                                       |

| 4 | Good packets with the specified service          | 0x7A      | SIO to SI7 written in units of a bit  |

|   | identifier SI.                                   | 0x7B      | SI8 to SI15 written in units of a bit |

# 5.3.4 Specification of SI (Service identifier)

|         |               |      |      |      |      | 1    | 1    |     |     |

|---------|---------------|------|------|------|------|------|------|-----|-----|

| Address | R/W           | DB7  | DB6  | DB5  | DB4  | DB3  | DB2  | DB1 | DB0 |

|         | W             | SI7  | SI6  | SI5  | SI4  | SI3  | SI2  | SI1 | SI0 |

|         | (Note 1)      |      |      |      |      |      |      |     |     |

| 0x35    | W             | SI15 | SI14 | SI13 | SI12 | SI11 | SI10 | SI9 | SI8 |

|         | (Note 2)      |      |      |      |      |      |      |     |     |

|         | Initial value | 1    | 1    | 1    | 1    | 1    | 1    | 1   | 1   |

## Table 5.3.4 SI Specification

Note 1: The setting SISEL=0 should have been made in the register 0x34.

Note 2: The setting SISEL=1 should have been made in the register 0x34.

This is the register for setting the service identifier SI which is an interrupt condition after the first horizontal error correction.

It is possible to specify multiple service identifiers by setting "1" to the bits corresponding to the required service identifiers among the 16 types SI0 to SI15 in the above table.

5.3.5 Receive port after the second horizontal error correction

| Table 5.3.5 | Receive data port after the second horizontal error correction |

|-------------|----------------------------------------------------------------|

|-------------|----------------------------------------------------------------|

| Address | R/W           | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---------|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0x38    | R             | B7  | B6  | B5  | B4  | B3  | B2  | B1  | B0  |

|         | W             | B7  | B6  | B5  | B4  | B3  | B2  | B1  | B0  |

|         | Initial value |     |     |     |     |     |     |     |     |

The receive port after the second horizontal error correction is connected to the frame memory. It is possible to read the frame memory successively since the frame memory address is incremented automatically whenever this port is read. It is also possible to read this port starting from any required address.

Packets in a frame synchronization state are accumulated in the frame memory. When the reception of one full frame is completed, the vertical error correction and the second horizontal error correction are made, and the receive interrupt after the second horizontal error correction occurs at the timing of the 13th packet in the next frame.

Although it is possible to receive from the middle of a frame, the vertical error correction will be omitted in that case. The frame synchronization state is indicated in the register 0x37 by dividing it into four groups. On the other hand, it is also possible to know this from the status indication byte at the beginning of each packet.

The volume of data in the frame memory is;

• 24x190 bytes in the case of 4-layer data including packet status indication;

• 36x273 bytes in the case of data including parity, etc.

See the data format of the receive frame memory after the second horizontal error correction in Section 5.3.6 for the detailed contents of data.

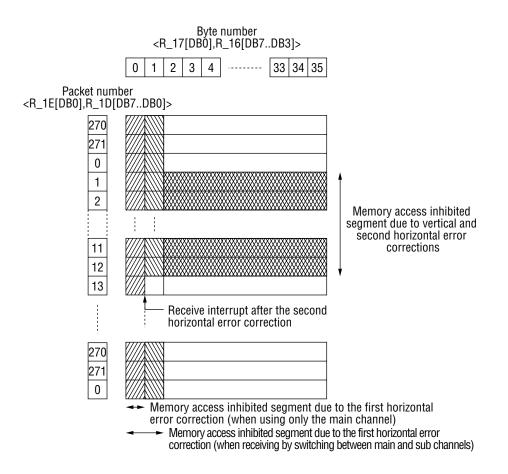

CAUTION: The frame memory has segments that are prohibited from being accessed. See Figure 5.3 for details.

# Figure 5.3 Access prohibited segments of the frame memory (R\_38)

- (1) The frame memory access inhibited time occurs when the intersection of the packet number and the byte number correspond to the hatched parts in the follwoing figure.

- (2) It is possible to know the packet number and the byte number by reading out the registers R\_1E, R\_1D, R\_16, and R\_17. (See the precautions to be taken at the time of reading out the packet number and byte number given in the next page.)

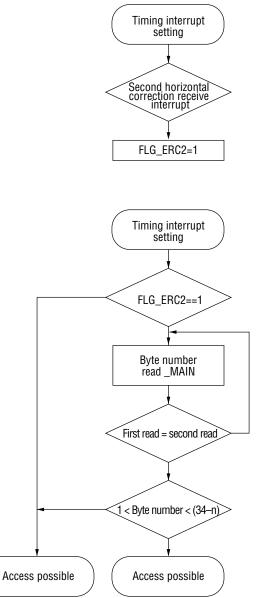

Precautions in reading the packet number and byte number

Since the microcontroller and data clocks are not mutually synchronized, it is possible that wrong values are read out when reading out is made when the packet number or the byte number is changing. Therefore, it is necessary to read them twice successively and use only after confirming that there is a match between the two successive values.

(1) Memory access is possible for about 16msec after the timing interrupt

(2) Checking the byte number and the packet number of Figure 5.3

n is the time of accessing the memory

5.3.6 Data configuration of the receive frame memory after the second horizontal error correction

|            |                       |                       |                                    | Byte                             | e No.                            |                                  |                                  |                                     |  |  |  |

|------------|-----------------------|-----------------------|------------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------------------|--|--|--|

| Packet No. | 0                     | 1                     | 2                                  | ••                               | 23                               | 24                               |                                  | 35                                  |  |  |  |

| 0          | Reception status 0    | Reception<br>status 1 | Data 0                             |                                  | Data 21                          | CRC/<br>PARITY                   |                                  | PARITY                              |  |  |  |

| :          | :                     | :                     | :                                  | :                                | :                                | :                                | :                                | :                                   |  |  |  |

| 189        | Reception status 0    | Reception<br>status 1 | Data 0                             |                                  | Data 21                          | CRC/<br>PARITY                   |                                  | PARITY                              |  |  |  |

| 190        | Reception status 0    | Reception<br>status 1 | Vertical<br>correction<br>parity   | Vertical<br>correction<br>parity | Vertical<br>correction<br>parity | Vertical<br>correction<br>parity | Vertical<br>correction<br>parity | Vertical<br>correction<br>parity    |  |  |  |

| :          | :                     | :                     | :                                  | :                                | :                                | :                                | :                                | :                                   |  |  |  |

| 271        | Reception<br>status 0 | Reception<br>status 1 | Vertical<br>correction<br>parity   | Vertical<br>correction<br>parity | Vertical<br>correction<br>parity | Vertical<br>correction<br>parity | Vertical<br>correction<br>parity | Vertical<br>correction<br>parity    |  |  |  |

| 272        |                       | _                     | Vertical<br>correction<br>result 0 |                                  |                                  |                                  |                                  | Vertical<br>correction<br>result 33 |  |  |  |

| Table 5.3.6.1 Receive frame memory data configuration after |

|-------------------------------------------------------------|

| the second horizontal error correction                      |

The frame memory data configuration is shown in Table 5.3.6.1. The data consists of 190 data packets, 82 parity packets, and one vertical correction result packet. Normally, the second horizontal error correction of the parity packets 190 to 271 are omitted. To read packets including the parity packets after the second horizontal error correction, it is necessary to set and carry out the error correction separately for testing purposes.

The leading two bytes of each packet indicate the reception status.

The details of the reception status are shown in Table 5.3.6.2.

### Table 5.3.6.2 Reception status after the second horizontal error correction

|                    | DB7     | DB6    | DB5    | DB4   | DB3   | DB2    | DB1   | DB0   |

|--------------------|---------|--------|--------|-------|-------|--------|-------|-------|

| Reception status 0 | CRC0    | ERC0   | RECCRC | FSYNC | BSYNC | BICDET | BIC1  | BICO  |

| Reception status 1 | VICSRDY | PARITY | INT0   | CRC2  | ERC2  | FNCHG  | FRN01 | FRN00 |

Reception status 0

The reception status 0 is equal to the contents of BYTE0 received after the first horizontal error correction.

(1) DB7: CRC0

Indicates that there is an error in the CRC of the packet after the first horizontal error correction.

Indicates that the CRC of the packet is normal after the first horizontal error correction.

- 1: Indicates that there is an error in the correction result of the packet after the first horizontal error correction.

- 0: Indicates that the correction result of the packet is normal after the first horizontal error correction.

<sup>(2)</sup> DB6: ERC0

### (3) DB5: RECCRC

Indicates that there is an error in the CRC of the received packet before error correction.

Indicates that the CRC of the received packet is normal before error correction.

## (4) DB4: FSYNC

1: Indicates that the received packet is in a frame synchronization state.

- 0: Indicates that the received packet is in a frame out-of-synchronizaiton state.

- (5) DB3: BSYNC

- 1: Indicates that the received packet is in a block synchronization state.

- 0: Indicates that the received packet is in a block out-of-synchronization state.

- (6) DB2 to DB0: BIC Monitor

Indicate the detection condition of the block identification code (BIC).

| DB2 | DB1 | DB0 | BIC No.      |  |  |

|-----|-----|-----|--------------|--|--|

| 1   | 0   | 0   | 1            |  |  |

| 1   | 0   | 1   | 2            |  |  |

| 1   | 1   | 0   | 3            |  |  |

| 1   | 1   | 1   | 4            |  |  |

| 0   | _   |     | Not detected |  |  |

Reception status 1

(1) DB7: VICSRDY

- 1: Indicates that the received packet after the second horizontal error correction is a VICS packet.

- 0: Indicates that the received packet after the second horizontal error correction is not a VICS packet.

- (2) DB6: PARITY

This bit indication is made only in a frame synchronization state.

- 1: Indicates that the received packet is a parity packet.

- 0: Indicates that the received packet is not a parity packet.

- (3) DB5: INT0

- Indicates that the received packet is the one in which the receive interrupt occurred after the first horizontal error correction.

It is not necessary to read this if the reading has already been done during the reception after the first horizontal error correction.

- 0: Indicates that the received packet is one in which no receive interrupt occurred after the first horizontal error correction.

- (4) DB4: CRC2

- 1: Indicates that there is an error in the CRC of the packet after the second horizontal error correction.

- 0: Indicates that the CRC of the packet is normal after the second horizontal error correction.

- (5) DB3: ERC2

- 1: Indicates that there is an error in the correction result of the packet after the second horizontal error correction.

- 0: Indicates that the correction result of the packet is normal after the second horizontal error correction.

Note: CRC2=ERC2=0 is necessary for the packet to be good (error-free).

(6) DB2: FNCHG

This bit indication is made only in a frame synchronization state.

- 1: Indicates that the packet is one with a block number of 1, 14, 137, or 150 in the case of the frame format B, and with a block number of 1, 61, 131, or 191 in the case of the frame formats A0 and A1.

- 0: Indicates that the packet is one other than the above.

- (7) DB1, DB0: FRNO1, FRNO0

These bit indications are made only in a frame synchronization state.

These bits indicate that the packet is one with the block numbers given in the following table.

|     |     | Frame format                              |                                          |                                          |  |  |  |  |  |  |

|-----|-----|-------------------------------------------|------------------------------------------|------------------------------------------|--|--|--|--|--|--|

| DB1 | DB0 | Format B                                  |                                          | Format A1, A0                            |  |  |  |  |  |  |

| 0   | 0   | Packet with a block number of 0 to 12.    | Packet with a block number of 0 to 59    |                                          |  |  |  |  |  |  |

| 0   | 1   | Packet with a block number of 13 to 135.  | Packet with a block number of 60 to 129  |                                          |  |  |  |  |  |  |

| 1   | 0   | Packet with a block number of 136 to 148. | Packet with a block number of 130 to 189 |                                          |  |  |  |  |  |  |

| 1   | 1   | Packet with a block number of 149 to 271. | A0                                       | Packet with a block number of 190 to 271 |  |  |  |  |  |  |

|     |     |                                           | A1                                       | Packet with a block number of 190 to 283 |  |  |  |  |  |  |

Note: The packet numbers are expressed in this manual as 0 to 271 (A1: 0 to 283).

5.3.7  $\,$  Setting the receive frame memory access mode after the second horizontal error correction

| Address | R/W           | DB7   | DB6   | DB5    | DB4   | DB3   | DB2    | DB1    | DB0    |

|---------|---------------|-------|-------|--------|-------|-------|--------|--------|--------|

|         | W             | BANK  | BANK  | VLBCNT | PCTL1 | VBACK | LBACK1 | LBACK0 | LSTART |

| 0x39    |               | CONT1 | CONTO |        | BL2   |       |        |        |        |

|         | Initial value | 0     | 0     | 0      | 0     | 0     | 1      | 0      | 0      |

Table 5.3.7

Frame memory access mode

This is the register for setting the access mode so that reading can be done efficiently when reading the frame memory successively.

(1) DB7, DB6: BANK1, BANK0

These bits are for making settings for testing purposes. Normally use with the settings of DB7=DB6=0.

- (2) DB5: VLBCNT

- 1: The frame memory is read in the vertical direction (in an ascending order of the packet number with the byte number being kept fixed).

- 0: The frame memory is read in the horizontal direction (in an ascending order of the byte number with the packet number being kept fixed).

The packet number is incremented by 1 when the byte number reaches that specified by LBACK0 and LBACK1.

- (3) DB4: PCTL1BL2

The readable frame memory address (packet number) is selected from the registers 0x3C and 0x3D.

- 1: Enables the MSM9563 to read the address (packet number) of the receive data packet that is being written.

- 0: Enables an external microcontroller to read the address (packet number) of the receive data packet that is being accessed.

- (4) DB3: VBACK

- 1: When the packet number becomes 272, the next packet number will be reset to 0. For testing purposes only.

- 0: When the packet number becomes 189, the next packet number will be reset to 0.

- (5) DB2, DB1: LBACK1, LBACK0

The next byte number is reset to the byte number specified by LSTART when the current byte number becomes the returning byte number given in the following table.

| LBACK1 | LBACK0 | Returning byte No. |

|--------|--------|--------------------|

| 0      | 0      | 1                  |

| 0      | 1      | 2                  |

| 1      | 0      | 23                 |

| 1      | 1      | 35                 |

- (6) DB0: LSTART

- 1: The next byte number is reset to 2 when the current byte number becomes equal to the value specified by LBACK0 and LBACK1.

- 0: The next byte number is reset to 0 when the current byte number becomes equal to the value specified by LBACK0 and LBACK1.

5.3.8 Receive frame memory pointer after the second horizontal error correction

| Address | R/W           | DB7 | DB6 | DB5   | DB4   | DB3   | DB2   | DB1   | DB0   |

|---------|---------------|-----|-----|-------|-------|-------|-------|-------|-------|

|         | R/W           |     | —   | EXT   | EXT   | EXT   | EXT   | EXT   | EXT   |

| 0x3B    |               |     |     | BYTE5 | BYTE4 | BYTE3 | BYTE2 | BYTE1 | BYTE0 |

|         | Initial value |     | _   | 0     | 0     | 0     | 0     | 0     | 0     |

#### Table 5.3.8.1 Frame memory address (1/3)

Table 5.3.8.2 Frame memory address (2/3)

| Address | R/W           | DB7  | DB6  | DB5  | DB4  | DB3  | DB2  | DB1  | DB0  |

|---------|---------------|------|------|------|------|------|------|------|------|

|         | R             | EXT  |

|         | (Note 1)      | PCT7 | PCT6 | PCT5 | PCT4 | PCT3 | PCT2 | PCT1 | PCT0 |

|         | R             | L1BF |

| 0x3C    | (Note 2)      | PCT7 | PCT6 | PCT5 | PCT4 | PCT3 | PCT2 | PCT1 | PCT0 |

|         | W             | EXT  |

|         |               | PCT7 | PCT6 | PCT5 | PCT4 | PCT3 | PCT2 | PCT1 | PCT0 |

|         | Initial value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

Note 1: The setting PCTL1BL2=0 should have been made in the register 0x39.

Note 2: The setting PCTL1BL2=1 should have been made in the register 0x39 (used in the page mode).

| Address | R/W           | DB7     | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0  |

|---------|---------------|---------|-----|-----|-----|-----|-----|-----|------|

|         | R             | MEMSTAT | _   |     | _   | _   |     | _   | EXT  |

|         | (Note 1)      |         |     |     |     |     |     |     | PCT8 |

|         | R             | _       | _   | _   | _   |     |     | _   | L1BF |

| 0x3D    | (Note 2)      |         |     |     |     |     |     |     | PCT8 |

|         | W             | _       | _   | _   | _   |     |     | _   | EXT  |

|         |               |         |     |     |     |     |     |     | PCT8 |

|         | Initial value | _       | _   | —   | _   | _   | _   | _   | 0    |

Table 5.3.8.3 Frame memory address (3/3)

Note 1: The setting PCTL1BL2=0 should have been made in the register 0x39.

Note 2: The setting PCTL1BL2=1 should have been made in the register 0x39.

### <u>Write</u>

Before reading from the receive port after the second horizontal error correction of the register 0x38, it is necessary to set the packet number and the byte number in the register. Specify the packet number of the starting byte and the starting byte number of the data to be read according to Table 5.3.6.1 "Data configuration of the receive frame memory after the second horizontal error correction".

Thereafter successive reads will be possible according to the "Access mode setting of the receive frame memory after the second horizontal error correction".

## Read (PCTL1BL2=0)

It is possible to know the byte number and the packet number of the data to be read next by reading these registers 0x3B, 0x3C, and 0x3D.

However, it is necessary to set PCTL1BL2 of the register 0x39 to "0". Before reading these registers.

## Read (PCTL1BL2=1)

The registers 0x3C and 0x3D indicate the frame memory address (packet number) of the data packet received after the first horizontal error correction, which is to be written next.

5.3.9 Reception status of the receive frame memory after the second horizontal error correction

| Address | R/W           | DB7  | DB6    | DB5   | DB4      | DB3     | DB2     | DB1     | DB0     |

|---------|---------------|------|--------|-------|----------|---------|---------|---------|---------|

|         | R             | BANK | —      | _     | _        | BANK    | BANK    | BANK    | BANK    |

|         |               |      |        |       |          | _ERCFR0 | _ERCFR1 | _ERCFR2 | _ERCFR3 |

| 0x37    | W             |      | BANKLT | MOD_  | EXPCTCNT | BANK    | BANK    | BANK    | BANK    |

|         |               |      | _CLR   | EXERC | STARTB   | _ERCFR0 | _ERCFR1 | _ERCFR2 | _ERCFR3 |

|         | Initial value | —    | 0      | 0     | 0        | 0       | 0       | 0       | 0       |

# Table 5.3.9 Frame synchronization status

Read

# (1) DB0 to DB3: BANK\_ERCFR3 to BANK\_ERCFR0

When data is read after a receive interrupt after the second horizontal error correction, these four bits indicate whether the four packet groups listed in the following table are in a frame synchronization state or not.