# **MSM9405**

**Application Manual**

IrDA Controller LSI

SECOND EDITION

ISSUE DATE: Jul. 2000

FEAL9405-02

#### NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents cotained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 2000 Oki Electric Industry Co., Ltd.

# CONTENTS

| 1. | Gen | eral Description                                      | 1  |

|----|-----|-------------------------------------------------------|----|

|    | 1.1 | Features                                              | 1  |

|    | 1.2 | Pin Configuration & Pin Descriptions                  | 2  |

|    | 1.3 | External Connection Example                           | 4  |

| 2. |     | nsmit/Receive Procedure Examples                      |    |

|    | 2.1 | Initialization Procedure Example                      | 5  |

|    | 2.2 | Receive Procedure Example: SIR                        |    |

|    |     | Transmit Procedure Example: SIR                       |    |

|    | 2.4 | Receive Procedure Example: Ex-SIR                     |    |

|    | 2.5 | Transmit Procedure Example: Ex-SIR (S_EOT is used)    |    |

|    | 2.6 | Transmit Procedure Example: Ex-SIR (TFL/TCC are used) |    |

|    | 2.7 | Transmit Procedure Example: MIR                       |    |

|    | 2.8 | Media Busy Detection Procedure Example                |    |

| 3  |     | ernal Interface Settings                              |    |

| 0. | 3.1 |                                                       |    |

|    | 0.1 | 3.1.1 SD_INV                                          |    |

|    |     | 3.1.2 IRIN_SL                                         |    |

|    |     | 3.1.3 RXINV                                           |    |

|    |     | 3.1.4 MS_EN                                           |    |

|    | 32  | Selecting the Crystal Unit                            |    |

|    | 3.3 | Setting the DMAC Interface                            |    |

|    | 0.0 | 3.3.1 DMA_EN                                          |    |

|    |     | 3.3.2 DMA_SL1, DMA_SL0                                |    |

|    |     | 3.3.3 DMATH1, DMATH0                                  |    |

|    |     | 3.3.4 TC_INV, DACK_INV, DREQ_INV                      |    |

|    | 3.4 | Setting the Interrupt Interface                       |    |

| л  | -   | munication Mode Settings                              |    |

| 4. | 4.1 | Setting the Operating Modes                           |    |

|    | 4.1 | 4.1.1 Power-Down Mode                                 |    |

|    |     | 4.1.2 Idle Mode                                       |    |

|    |     | 4.1.2 Transmit Mode                                   |    |

|    |     | 4.1.3 Hanshit Mode                                    |    |

|    | 4.2 | Setting the Transfer Mode                             |    |

|    | 4.2 | •                                                     |    |

|    | 4.3 | Setting the Transfer Speed                            |    |

| F  |     | Setting the Number of BOFs (STAs)                     |    |

| э. |     | ing Interrupts<br>TXE_EV, TXE_IE                      |    |

|    |     |                                                       |    |

|    | 5.2 | TXL_EV, TXL_IE<br>RXH/T_EV, TOUT, RXH/T_IE            | 20 |

|    | 5.3 |                                                       |    |

|    |     |                                                       |    |

|    |     |                                                       |    |

|    |     |                                                       |    |

|    |     |                                                       |    |

|    | 5.8 | FE_EV, FE_IE                                          | 30 |

| 6. How  | to Ad  | d FCS/EOF                                 | 31  |

|---------|--------|-------------------------------------------|-----|

| 6.1     | How t  | to Use S_EOT                              | 31  |

| 6.2     | How    | to Use TFL/TCC                            | 31  |

| 6.3     | How    | to Use TC                                 | 31  |

| 7. FIFC | D      |                                           | 32  |

| 7.1     | Settin | g the Transmit/Receive Threshold Levels   | 32  |

| 7.2     | Numb   | per of Data Bytes in the FIFO             | 33  |

| 7.3     | FCLR   | )                                         | 33  |

|         |        | ctions                                    |     |

| 8.1     | How t  | to Use IR_DET                             | 34  |

| 8.2     | How t  | o Send Serial Infrared Interaction Pulses | 34  |

| 8.3     | Invert | ed CRC                                    | 34  |

| 8.4     | RST.   |                                           | 35  |

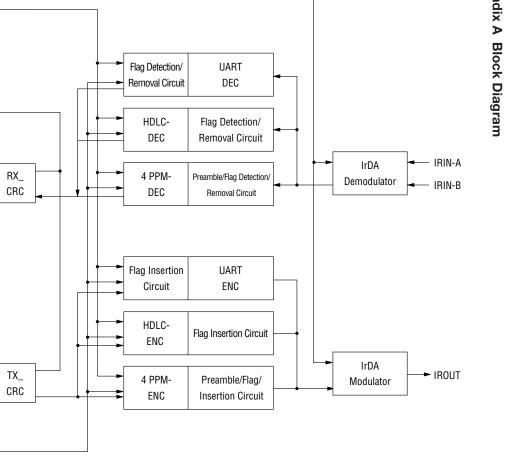

| Appen   | dix-A  | Block Diagram                             | A-1 |

| Appen   | dix-B  | Electrical Characteristics                | B-1 |

| Appen   | dix-C  | Timing Diagram                            | C-1 |

| Appen   | dix-D  | Register Table                            | D-1 |

| Appen   | dix-E  | Package Outline and Dimensions            | E-1 |

# 1. General Description

The MSM9405 is a communication controller conforming to the physical specification ver1.1 of IrDA, the international standard for infrared data communication.

By combining the MSM9405 with another microcontroller, a protocol stack, and an infrared transceiver module, equipment provided with IrDA-compliant communication function can be configured.

The MSM9405 is provided with a unique Extended-SIR mode to insert or remove BOF, EOF, and CRC by hardware. They were inserted or removed only by software before.

With the Extended-SIR mode, it is possible to cut down the software development cost, to speed up the processing, and to reduce the ROM capacity.

Since the input and I/O pins except the XIN pin are composed of 5 V tolerant buffers, the MSM9405 can interface with 5 V systems.

#### 1.1 Features

• Data transfer rates

2400, 9600 bps; 19.2, 38.4, 57.6, 115.2 kbps; 0.576, 1.152, 4 Mbps

• Extended-SIR mode to support some functions of protocol

| Mode         | Transfer rate       | Insert or<br>remove BOF | Insert or<br>remove CRC | Insert or<br>remove EOF | Insert or<br>remove CE | Insert or<br>remove "0" | Insert or<br>remove<br>Preamble |

|--------------|---------------------|-------------------------|-------------------------|-------------------------|------------------------|-------------------------|---------------------------------|

| SIR          | 2.4 to 115.2 kbps   | SW                      | SW                      | SW                      | SW                     |                         | —                               |

| Extended-SIR | 2.4 to 115.2 kbps   | HW                      | HW                      | HW                      | HW                     |                         | _                               |

| MIR          | 0.576 M, 1.152 Mbps | HW                      | HW                      | HW                      | —                      | HW                      | _                               |

| FIR          | 4 Mbps              | HW                      | HW                      | HW                      | —                      |                         | HW                              |

CE: Control Escape Byte

SW: Supported by software (microcontroller) HW: Supported by hardware (MSM9405)

| <ul> <li>Host interface</li> </ul> |                                                 |

|------------------------------------|-------------------------------------------------|

| 8-bit data bus                     | : D0 to D7                                      |

| DMA transfer                       | : DREQ, DACK, TC                                |

| Interrupt                          | : INTR                                          |

| Address                            | : $A_0$ to $A_3$                                |

| Control signal                     | $: \overline{CS}, \overline{RD}, \overline{WR}$ |

| T ( 1, · ·                         | 1 1 / 1 / 1                                     |

- Infrared transceiver module control signal : SD

- Built-in 32-byte transmit-receive FIFOs

- Power down mode

- Built-in oscillator circuit

- Crystal oscillation frequency : 18.432 MHz (other than 4 Mbps data rate) : 48 MHz (up to 4 Mbps data rate)

- Operating voltage (V<sub>DD</sub>) : 2.7 to 3.6 V

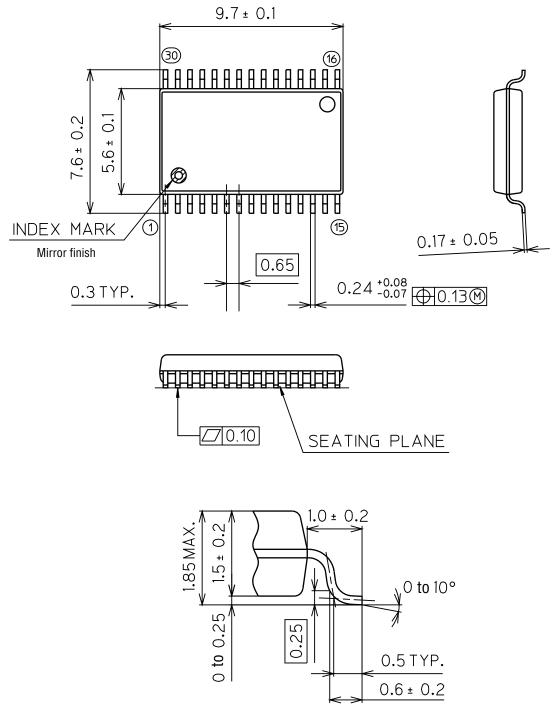

- Package: 30-pin plastic SSOP (SSOP30-P-56-0.65-K) (Product name : MSM9405MB)

#### **1.2 Pin Configuration & Pin Descriptions**

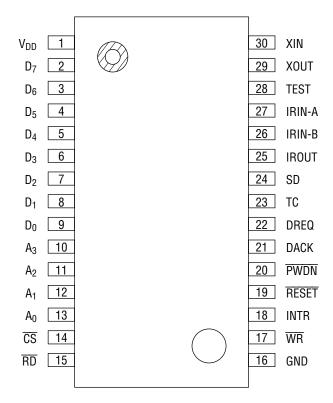

#### Pin Configuration (Top View)

**30-Pin Plastic SSOP**

#### **Pin Descriptions**

| Function             | Pin   | Symbol                         | Туре | Description                                                       |

|----------------------|-------|--------------------------------|------|-------------------------------------------------------------------|

| Infrared Transceiver | 27    | IRIN-A                         | I    | Receive signal input A. (2.4 kbps to 4 Mbps) <sup>*1</sup>        |

| Module Interface     | 26    | IRIN-B                         | I    | Receive signal input B. (0.576 to 4 Mbps)                         |

|                      |       |                                |      | When connecting this device to an infrared transceiver            |

|                      |       |                                |      | module, tie this pin high or low if the number of the receive     |

|                      |       |                                |      | signal output pins that the module has is only one. <sup>*1</sup> |

|                      | 25    | IROUT                          | 0    | Transmit signal output. Active high.                              |

|                      | 24    | SD                             | 0    | Infrared transceiver module control signal output.                |

|                      |       |                                |      | Becomes active when PWDN is set low. <sup>*1</sup>                |

|                      |       |                                |      | This pin must be left open if connecting this device to an        |

|                      |       |                                |      | infrared transceiver module having no shutdown pins.              |

| Microcontroller      | 2-9   | D7-D0                          | I/0  | Data input-output.                                                |

| Interface            | 10-13 | A <sub>3</sub> -A <sub>0</sub> | I    | Register address inputs.                                          |

|                      | 14    | CS                             | I    | Chip select input. Active low.                                    |

|                      |       |                                |      | When low, read and write signals are enabled.                     |

|                      | 15    | RD                             | I    | Read signal input. Active low.                                    |

|                      | 17    | WR                             | I    | Write signal input. Active low.                                   |

|                      | 18    | INTR                           | 0    | Interrupt request signal output. *1                               |

| DMA Controller       | 22    | DREQ                           | 0    | DMA Request signal output. <sup>*1</sup>                          |

| Interface            | 21    | DACK                           | I    | DMA acknowledge signal input. <sup>*1</sup>                       |

|                      | 23    | TC                             | Ι    | DMA transfer end signal input. <sup>*1</sup>                      |

| Others               | 20    | PWDN                           | I    | Power down control. Active low.                                   |

|                      |       |                                |      | When set low, oscillation stops and the device enters power       |

|                      |       |                                |      | down (low supply current) mode.                                   |

|                      | 19    | RESET                          | I    | System reset input. Active low.                                   |

|                      |       |                                |      | When set low, the internal registers are initialized.             |

|                      | 28    | TEST                           | 0    | Test. Must be left open.                                          |

|                      | 30    | XIN                            | I    | Crystal connect.                                                  |

|                      | 29    | XOUT                           | 0    | Crystal connect.                                                  |

|                      | 1     | V <sub>DD</sub>                | _    | Power supply.                                                     |

|                      | 16    | GND                            | _    | Ground.                                                           |

\*1 Either active high or active low can be selected depending on the register setting.

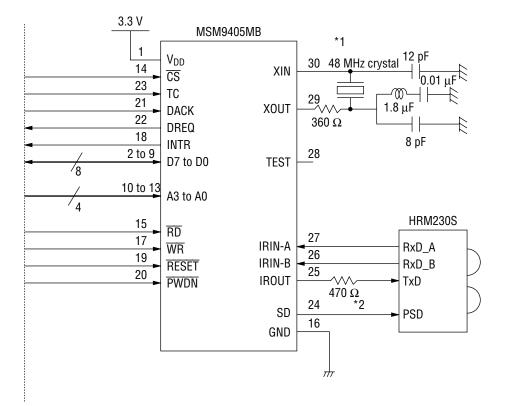

#### **1.3 External Connection Example**

#### **Microcontroller interface**

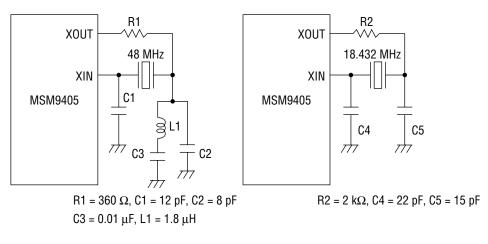

- \*1: Crystal units manufactured by MEIDENSHA CORP. are recommended. For details, refer to section 3.2, "Selecting the Crystal Unit."

- \*2: The value of this resistor is the reference value for connection to a HRM230S device manufactured by Stanley Electric Co., Ltd. Consult with individual module manufacturers regarding peripheral components for each infrared transceiver module.

- Note: Since the input and I/O pins except the XIN pin are composed of 5 V tolerant buffers, the MSM9405 can interface with 5 V systems. The I/O pins should not be pulled up to 5 V supply.

# 2. Transmit/Receive Procedure Examples

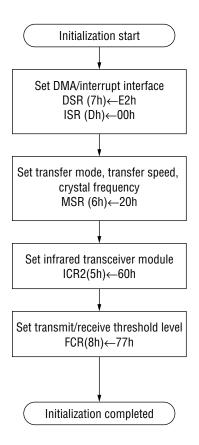

#### 2.1 Initialization Procedure Example

Transfer mode: SIR Transfer speed: 9600 bps Crystal: 48 MHz Infrared transceiver module: HRM230S (manufactured by Stanley Electric Co., Ltd.) DMA controller: 8237 type (DMA transfer is disabled)

Set the DMA interface according to the 8237 type. (Set DREQ = Active High; DACK = Active Low; TC = Active High; DMA threshold during transmission = 32, during reception = 0; DMA transfer mode = single; disable DMA transfer) (See section 3.3, "Setting the DMAC Interface") Set INTR = Active Low. (See section 3.4, "Setting the Interrupt Interface")

Set transfer mode to SIR, transfer speed to 9600 bps, and crystal frequency to 48 MHz. (See section 3.2, "Selecting the Crystal Unit", section 4.2, "Setting the Transfer Mode", and section 4.3, "Setting the Transfer Speed")

Set shutdown signal polarity and receive pulse polarity to the HRM230S polarity, set the receive pin setting to 2 pins. (See section 3.1, "Setting the Infrared Transceiver Module Interface")

Set the threshold level for both transmit and receive to "14". (See section 7.1, "Setting the Transmit/Receive Threshold Levels")

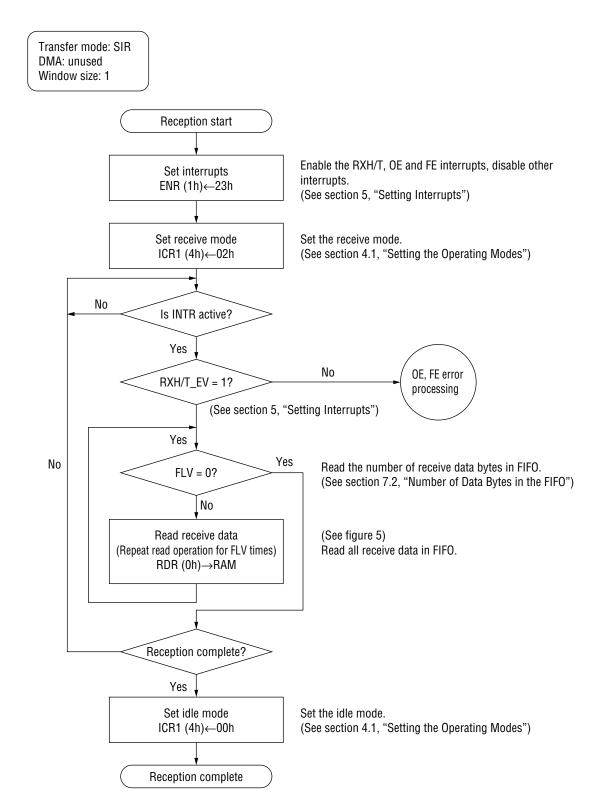

#### 2.2 Receive Procedure Example: SIR

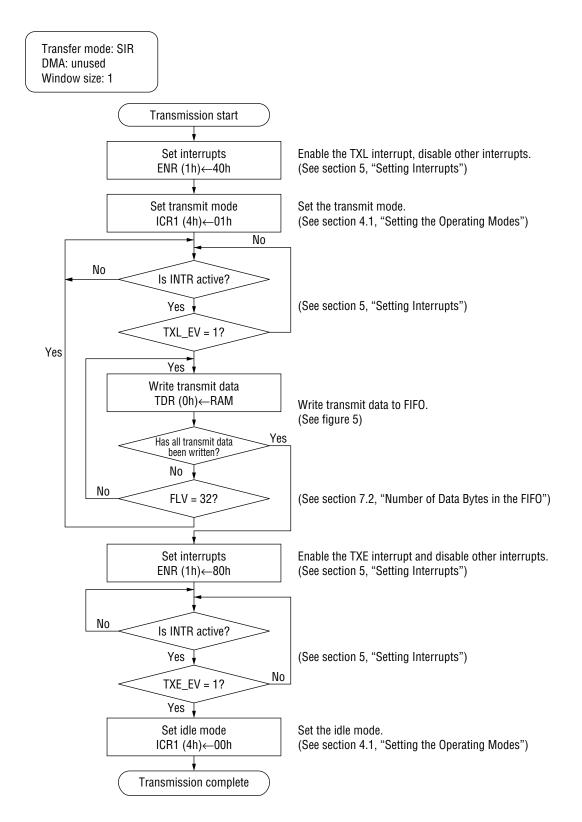

#### 2.3 Transmit Procedure Example: SIR

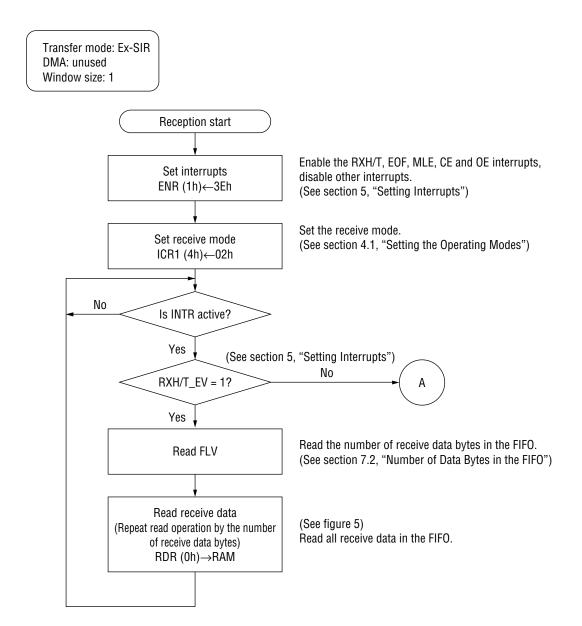

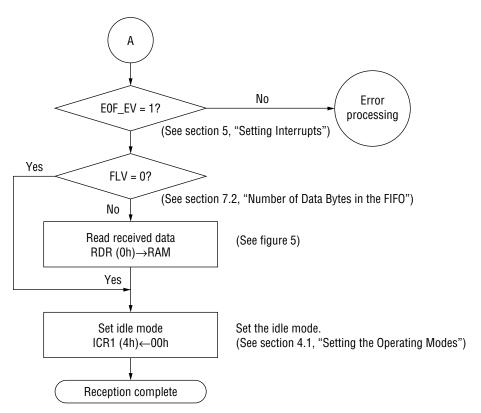

#### 2.4 Receive Procedure Example: Ex-SIR

# Receive Procedure Example: Ex-SIR (continued)

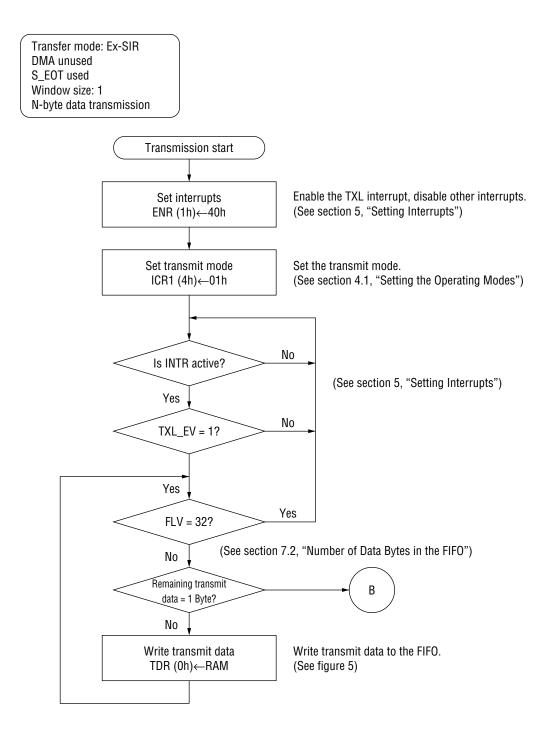

#### 2.5 Transmit Procedure Example: Ex-SIR (S\_EOT is used)

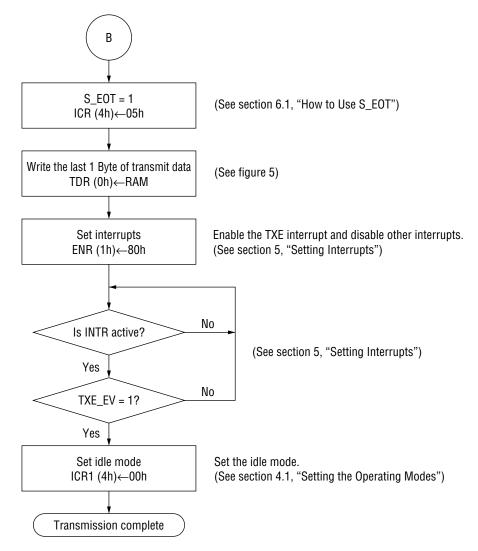

# Transmit Procedure Example: Ex-SIR (S\_EOT is used) (continued)

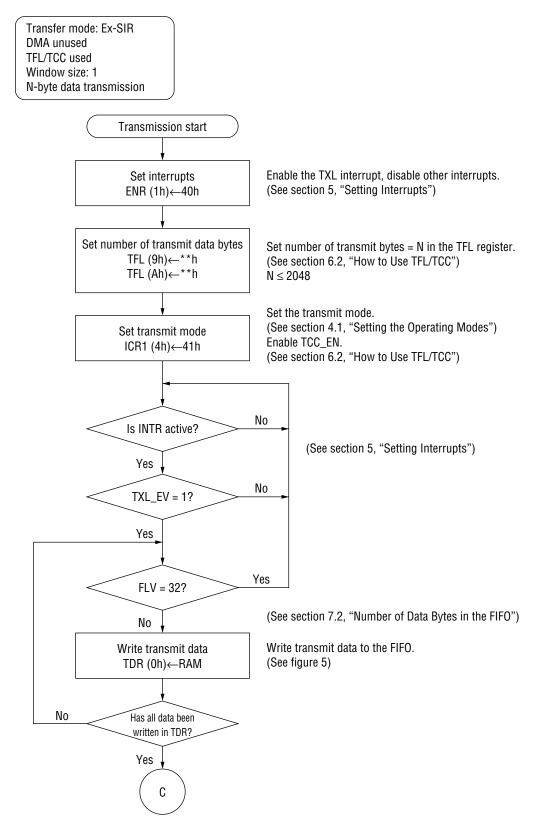

#### 2.6 Transmit Procedure Example: Ex-SIR (TFL/TCC are used)

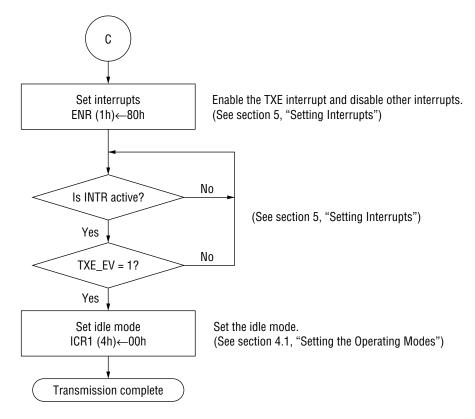

# Transmit Procedure Example: Ex-SIR (TFL/TCC are used) (continued)

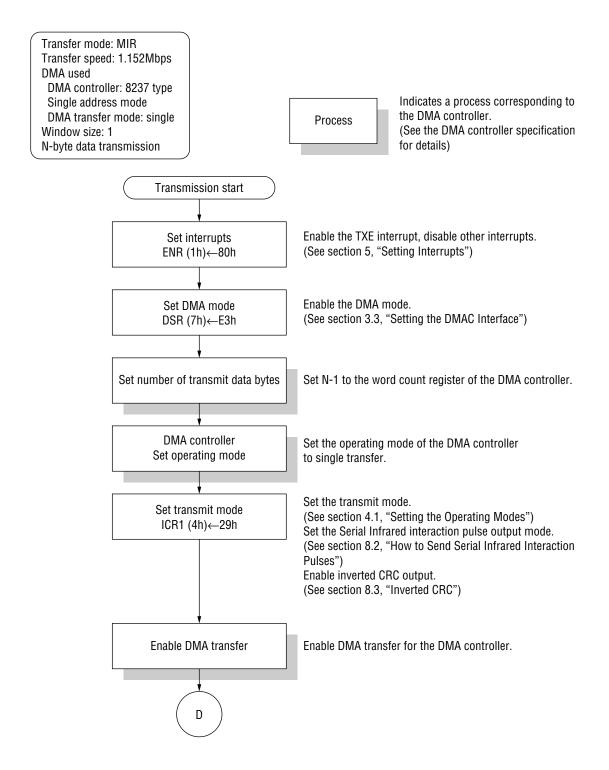

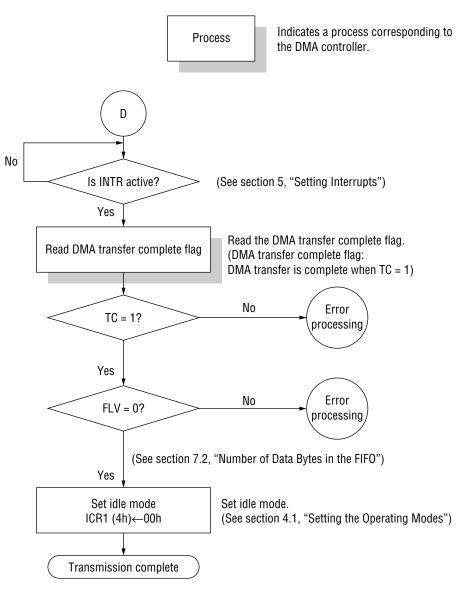

#### 2.7 Transmit Procedure Example: MIR

# Transmit Procedure Example: MIR (continued)

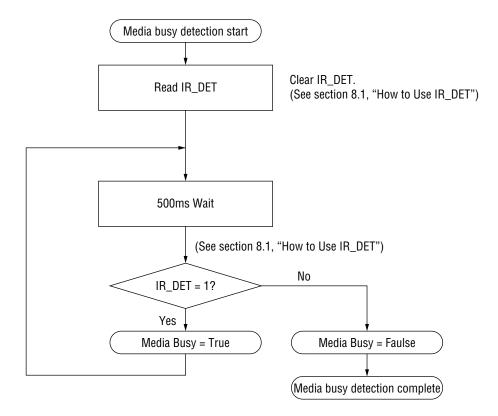

#### 2.8 Media Busy Detection Procedure Example

# 3. External Interface Settings

#### 3.1 Setting the Infrared Transceiver Module Interface

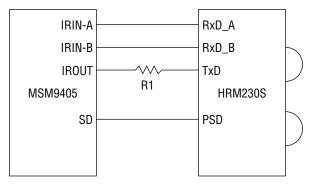

The MSM9405 contains the following 4 pins for interfacing to an infrared transceiver: IRIN-A, IRIN-B, IROUT, and SD. Selection of receive pins (IRIN-A, IRIN-B) and selection of polarity for IRIN-A, IRIN-B, and SD pins are performed by bit 6 (SD\_INV), bit 5 (IRIN\_SL), and bit 4 (RXINV) of the ICR2 register (address 5h). These pins and settings allow connection to various types of infrared transceiver modules. An example showing the connection to the HRM230S infrared transceiver module (manufactured by Stanley Electric Co., Ltd.) is shown in figure 1.

$R1 = 470 \ \Omega$  (reference value) Figure 1

#### 3.1.1 SD\_INV

The SD pin (pin 24) is linked to the input signal of the  $\overline{PWDN}$  pin (pin 20).

If connecting to a infrared transceiver module that has an active-low power-down pin (shuts down when at a low level), set SD\_INV to 1. In this state, if a low level is input to the PWDN pin of the MSM9405, the SD pin of the MSM9405 will output a low level and the infrared transceiver module will enter the shut down state. (The MSM9405 will enter the power-down mode.) If connecting to a transceiver module that has an active-high power-down pin (shuts down when at a high level), set SD\_INV to 0. In this state, if a low level is input to the PWDN pin of the MSM9405, the SD pin of the MSM9405 will output a high level and the infrared transceiver module will enter the shut down state. (The MSM9405 will enter the power-down pin (shuts down when at a high level), set SD\_INV to 0. In this state, if a low level is input to the PWDN pin of the MSM9405, the SD pin of the MSM9405 will output a high level and the infrared transceiver module will enter the shut down state. (The MSM9405 will enter the power-down mode.) If the infrared transceiver module to be connected does not contain a shut down pin, leave the SD pin of the MSM9405 open (unconnected) and SD\_INV can be set to either 0 or 1.

3.1.2 IRIN\_SL

The MSM9405 has two receive signal input pins, IRIN-A and IRIN-B.

If IRIN\_SL is set to 1, the input signal will be received from IRIN-A when the transfer speed is  $\leq$  115.2 kbps, and from IRIN-B when the transfer speed is  $\geq$  0.576 Mbps.

If IRIN\_SL is set to 0, the input signal will be received only from IRIN-A, regardless of the transfer speed.

Set IRIN\_SL to 1 when connecting to an infrared transceiver module that contains 2 receive signal output pins. Set IRIN\_SL to 0 when connecting to an infrared transceiver module that contains 1 receive signal output pin.

#### 3.1.3 RXINV

The RXINV setting selects polarity of the receive signal.

If RXINV is set to 0, the IRIN-A (or IRIN-B) polarity is active low. If set to 1, the polarity is active high.

Set RXINV to 0 when connecting to an infrared transceiver module that will output a high level when there is no signal and a low level pulse when an infrared pulse is received. Set RXINV to 1 when connecting to an infrared transceiver module that will output a low level when there is no signal and a high level pulse when an infrared pulse is received.

3.1.4 MS\_EN

MS\_EN (bit 7 of the ICR1 register) is utilized when an infrared transceiver module (Note) is used that requires the mode to be set externally. If a "1" is written to this bit, the MSM9405 will operate as follows corresponding to the transfer mode. After operation is complete, MS\_EN is automatically reset to "0."

When the MSM9405 is in the FIR mode:

- 1. The SD pin is set to a high level \*2, and the IROUT pin is set to a high level.

- 2. After approximately 300 ns, set the SD pin to a low level \*2

- 3. Approximately 300 ns after step 2 (above), set the IROUT pin to a low level

When the MSM9405 is in the SIR, Ex-SIR, and MIR modes:

- 1. The SD pin is set to a high level \*2 and the IROUT pin is set to a low level

- 2. After approximately 300 ns, set the SD pin to a low level \*2

- 3. Maintain the IROUT pin at a low level from approximately 300 ns after step 2 (above)

MS\_EN cannot be used when a 18.432 MHz crystal is used (XT\_SL = 1, see section 3.2, "Selecting the Crystal Unit")

- Note: \*1 For methods to set the modes of infrared transceiver modules, refer to the data sheet for each module.

- \*2 When the SD pin is active high. When the SD pin is active low, the level is inverted.

### 3.2 Selecting the Crystal Unit

A 48 MHz or 18.432 MHz external crystal Unit can be connected to the MSM9405.

If an 18.432 MHz unit is used, the transfer speed will be up to 1.152 Mbps.

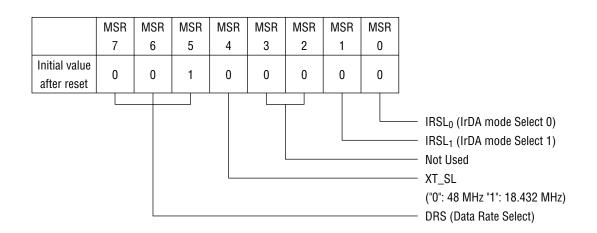

Selection of the crystal unit is performed by bit 4 (XT\_SL) of the MSR register (address 6h). Set XT\_SL to 0 if a 48 MHz crystal unit is to be used, and set XT\_SL to 1 if an 18.432 MHz crystal unit is to be used.

The following crystal units manufactured by MEIDENSHA Corp. are recommended. Depending upon the crystal or usage conditions, appropriate R, L, and C values will differ. Please consult with the crystal manufacturer.

48 MHz: 49U3H 48 MHz, MS-3H 48 MHz 18.432 MHz: 49U3H 18.432 MHz, MS-3H 18.432 MHz

#### 3.3 Setting the DMAC Interface

The DSR register (address 7h) performs various settings related to DMA transfer.

3.3.1 DMA\_EN

$DMA\_EN$  (bit 0) enables or disables the DMA transfer. DMA transfer is disabled when DMA\\_EN is "0" and transfer is enabled when DMA\\_EN is "1."

3.3.2 DMA\_SL1, DMA\_SL0

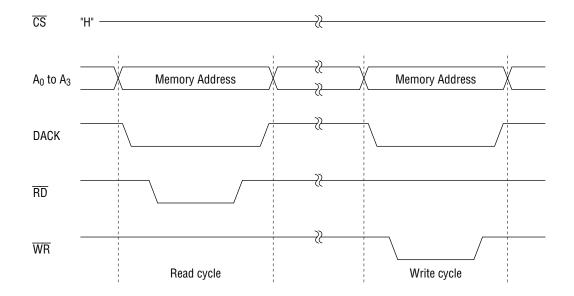

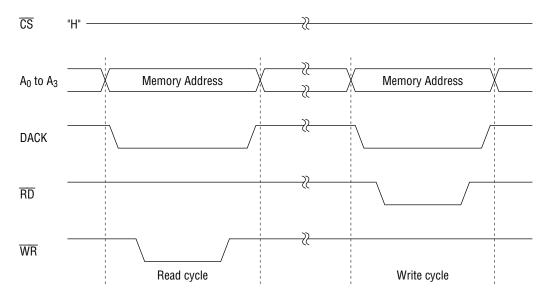

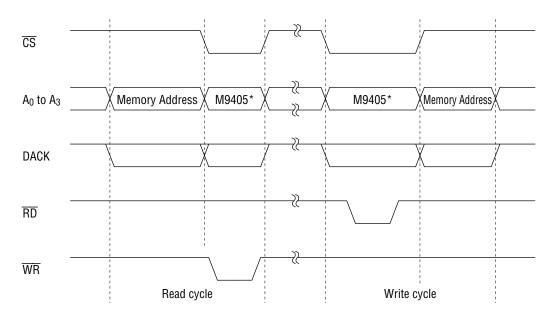

DMA\_SL1 and DMA\_SL0 (bits 2 and 1) select the DMA transfer mode. Modes can be selected as follows. (See Figure 3 and Figure 4)

| DMA_SL <sub>1</sub> | DMA_SL <sub>0</sub> | Function                                                                                                                                |

|---------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0                   | 0                   | Supports single address mode DMA transfer                                                                                               |

|                     |                     | If the $\overline{\text{RD}}$ signal is asserted while DACK is active, a read cycle <sup>*1</sup> begins. If the $\overline{\text{WR}}$ |

|                     |                     | signal is asserted while DACK is active, a write cycle <sup>*2</sup> begins. When DACK is                                               |

|                     |                     | active, access address 0h (TDR/RDR) independently of A0 to A3.                                                                          |

| 0                   | 1                   | Supports single address mode DMA transfer                                                                                               |

|                     |                     | If the $\overline{WR}$ signal is asserted while DACK is active, a read cycle <sup>*1</sup> begins. If the $\overline{RD}$               |

|                     |                     | signal is asserted while DACK is active, a write cycle <sup>*2</sup> begins. When DACK is                                               |

|                     |                     | active, access address 0h (TDR/RDR) independently of A0 to A3.                                                                          |

| 1                   | 0                   | Supports dual address mode DMA transfer                                                                                                 |

|                     |                     | Access TDR/RDR via $\overline{\text{CS}}$ and A0 to A3.                                                                                 |

| 1                   | 1                   | Reserved                                                                                                                                |

\*1 Read cycle: Memory→MSM9405

\*2 Write cycle: MSM9405→Memory

• Single address mode (DMA\_SL1 = 0, DMA\_SL0 = 0, DACK: active low)

• Single address mode (DMA\_SL1 = 0, DMA\_SL0 = 1, DACK: active low)

Figure 3

• Dual address mode (DMA\_SL1 = 1, DMA\_SL0 = 0, DACK: active low)

\* Specify TDR/RDR (address 0h).

Figure 4

### 3.3.3 DMATH1, DMATH0

DMATH1 and DMATH0 (bits 4 and 3) determine the threshold level at which the DREQ signal is deasserted.

When DMA is enabled during reception, the DREQ signal is asserted when the number of receive data bytes in FIFO is equal to or greater than the receive threshold level set in the FCR register. (See section 7.1, "Setting the Transmit/Receive Threshold Levels")

And when data is read from FIFO and the number of data bytes in FIFO is equal to the value set by DMATH, the DREQ signal is deasserted.

When DMA is enabled during transmission, the DREQ signal is asserted when the number of transmit data bytes in FIFO is smaller than the transmit threshold level set in the FCR register. (See section 7.1, "Setting the Transmit/Receive Threshold Levels")

And when data is written in FIFO and the number of data bytes in FIFO is equal to the value set by DMATH, the DREQ signal is deasserted.

A value greater than TXTH (see section 7.1, "Setting the Transmit/Receive Threshold Levels") should be set to DMATH during transmission, and a value smaller than RXTH should be set to DMATH during reception.

| DMATH <sub>1</sub> | DMATH <sub>0</sub> | During transmission | During reception |

|--------------------|--------------------|---------------------|------------------|

| 0                  | 0                  | 32                  | 0                |

| 0                  | 1                  | 30                  | 2                |

| 1                  | 0                  | 28                  | 4                |

| 1                  | 1                  | 24                  | 8                |

#### 3.3.4 TC\_INV, DACK\_INV, DREQ\_INV

TC\_INV (bit 5) sets the polarity of the TC signal. When TC\_INV is "0", the TC signal is active low and when TC\_INV is "1", the TC signal is active high.

DACK\_INV (bit 6) sets the polarity of the DACK signal. When DACK\_INV is "0", the DACK signal is active high and when DACK\_INV is "1", the DACK signal is active low.

DREQ\_INV (bit 7) sets the polarity of the DREQ signal. When DREQ\_INV is "0", the DREQ signal is active low and when DREQ\_INV is "1", the DREQ signal is active high.

When the DMA transfer function is not used, the DREQ pin should be open and the DACK and TC pins should be connected to  $V_{DD}$  or GND.

DREQ\_INV may be set to either "0" or "1". However, DACK\_INV and TC\_INV should be set so that the DACK and TC pins become inactive.

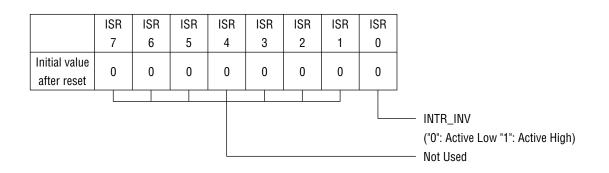

#### 3.4 Setting the Interrupt Interface

ISR (address Dh) sets the interrupt interface.

INTR\_INV (bit 0) sets the polarity of the INTR signal. When INTR\_INV is "0", the INTR signal is active low and when INTR\_INV is "1", the INTR signal is active high.

When the interrupt function is not used, the INTR pin should be open and INTR-INV can be set to either "0" or "1".

Bit 7 through bit 1 are reserved for future use.

# 4. Communication Mode Settings

#### 4.1 Setting the Operating Modes

The MSM9405 has the following four operating modes. Operation in any of the modes may be directly controlled externally via a microcontroller or other device. If the <u>PWDN</u> pin is pulled to a low-level, the MSM9405 enters the power-down mode. Or, with a high-level applied to the <u>PWDN</u> pin, bits 1 and 0 (RX\_EN and TX\_EN) of the ICR1 register can set the receive or transmit modes.

| PWDN | RX_EN | TX_EN | Operating Mode |

|------|-------|-------|----------------|

| L    | Х     | Х     | Power-down     |

| Н    | 0     | 0     | Idle           |

| Н    | 0     | 1     | Transmit       |

| Н    | 1     | Х     | Receive        |

X: Don't care

#### 4.1.1 Power-Down Mode

In the power-down mode, the MSM9405 stops oscillation and enters a low supply current state. In this state, do not access the TDR/RDR register (address 0h). Other registers may be accessed (addresses 1h to Dh).

After the power-down mode is released, wait at least 20 ms before performing transmission or reception.

#### 4.1.2 Idle Mode

In the idle mode, the MSM9405 does not perform transmission or reception. The register at address 0h operates as TDR, and transmit data can be written to the FIFO. The FIFO cannot be read.

#### 4.1.3 Transmit Mode

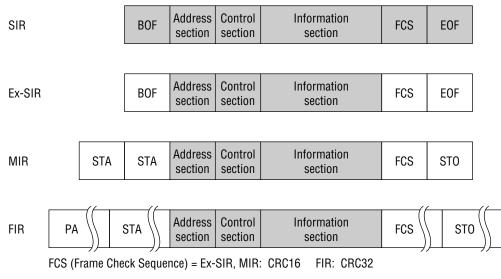

In the transmit mode, the register at address 0h operates as TDR, and transmit data can be written to the FIFO. The FIFO cannot be read. Transmission automatically begins when there is data in the FIFO. Data written to the FIFO differs depending upon the transfer mode. Write data for the shaded sections of figure 5. The MSM9405 automatically adds sections outside the shaded areas. (See section 6, "How to Add FCS/EOF.")

In the Ex-SIR mode, a specific code (C0, C1, 7D) escape sequence (7D is inserted in front of the specific code and the 5th bit of the specific code is inverted) is automatically performed. In the MIR mode, 0 is inserted (if there are consecutive 1's at the 5th bit or after, 0 is inserted at the 6th bit).

When transmission is completed, after all transmit data has been written to the FIFO, TXE\_EV has become "1", and after both FIFO and TSR (See APPENDIX-A "Block Diagram" for Transmitter Shift Register (TSR)) are empty, set TX\_EN to 0. (See section 5, "Setting Interrupts.")

To shift the receive mode to the transmit mode in the DMA mode, the following operations should be taken.

- 1. Set the idle mode.

- 2. Set the bits 3 to 0 (TXTH 3 to 0) of the FCR register (address 8h) to "0000".

- 3. Write 1 byte of dummy data to FIFO.

- 4. Set the value of TXTH to an arbitrary value.

- 5. Write 1 byte of dummy data to FIFO again.

- 6. Clear the dummy data written to FIFO by using FCLR.

- 7. Start transmission.

4.1.4 Receive Mode

In the receive mode, the register at address 0h operates as RDR, and the FIFO can be read. Writing to the FIFO is not possible.

If BOF code (Note) is input to the IRIN-A (or IRIN-B) pin, reception will begin. Thereafter, serial pulse strings input to the IRIN-A (or IRIN-B) pin are transformed into 8-bit parallel data and are written to the FIFO.

Data written to the FIFO differs depending upon the transfer mode. This data is the shaded sections of figure 5.

The MSM9405 automatically deletes sections outside the shaded areas.

However, if in the Ex-SIR mode, MIR mode, and FIR mode, the MSM9405 cannot detect EOF (STO) due to errors after reception begins and the BOF code of the next frame is input, the MSM9405 will write the BOF code into the FIFO as data without identifying the BOF code as the begining of the frame.

In this case, setting RX\_EN to "0" and then to "1" allows the MSM9405 to detect the BOF code that is input thereafter as the begining of the frame.

In the Ex-SIR mode, in contrast to a transmission, the specific code (C0, C1, 7D) is automatically reconstructed (7D in front of specific code is deleted and 5th bit of specific code is inverted). In the MIR mode, 0 is deleted (if there are consecutive 1s at the 5th bit or before, the 0 at the 6th bit is deleted).

Note : BOF code

- SIR : BOF (C0h)

- Ex-SIR : BOF (C0h)

MIR : STA (7Eh)

FIR : Preamble (100000010101000) + STA (0000110000011000001100000)

Figure 5

#### 4.2 Setting the Transfer Mode

The MSM9405 can be set to one of the following 4 different transfer modes using bit 1 (IRSL1) and bit 0 (IRSL0) of the MSR register (at address 6h)

| IRSL1 | IRSL0 | Mode         | Transfer speed      |

|-------|-------|--------------|---------------------|

| 0     | 0     | SIR          | 2.4 to 115.2 kbps   |

| 0     | 1     | Extended-SIR | 2.4 to 115.2 kbps   |

| 1     | 0     | MIR          | 0.576 to 1.152 Mbps |

| 1     | 1     | FIR          | 4 Mbps              |

#### 4.3 Setting the Transfer Speed

The MSM9405 can select the transfer speed using bit 7 to bit 5 (DRS2 to 0) of the MSR register (at address 6h). There are different transfer speeds selectable for each transfer mode as shown below.

| Bit 7 to bit 5 | During SIR mode | During MIR mode | During FIR mode |

|----------------|-----------------|-----------------|-----------------|

| 000            | 2400 bps        | 0.576 Mbps      | Reserved        |

| 001            | 9600 bps        | 1.152 Mbps      | 4 Mbps          |

| 010            | 19.2 kbps       | Reserved        | Reserved        |

| 011            | 38.4 kbps       | Reserved        | Reserved        |

| 100            | 57.6 kbps       | Reserved        | Reserved        |

| 101            | 115.2 kbps      | Reserved        | Reserved        |

| 110            | Reserved        | Reserved        | Reserved        |

| 111            | Reserved        | Reserved        | Reserved        |

# 4.4 Setting the Number of BOFs (STAs)

The MSM9405 can set the number of BOFs (STAs), that indicate the beginning of a frame during Ex-SIR mode or MIR mode, using bit 3 to bit 0 (SBF3 to 0 or MBF3 to 0) of the ICR2 register. The number of BOFs (STAs) set by SBF3 through SBF0 (or MBF3 to MBF0) are automatically appended in front of the data written to the FIFO, and then transmitted.

These bits are not used in the SIR and FIR modes.

During the FIR mode, 16 preambles of 16 chips and 1 STA of 32 chips are automatically appended in front of the data written to the FIFO. (See figure 5.)

| ICR2 bit 3 to bit 0 | During Ex-SIR mode | During MIR mode |

|---------------------|--------------------|-----------------|

| 0000                | 1                  | 2               |

| 0001                | 2                  | 3               |

| 0010                | 3                  | 4               |

| 0011                | 4                  | 5               |

| 0100                | 5                  | 8               |

| 0101                | 7                  | 12              |

| 0110                | 9                  | 16              |

| 0111                | 13                 | 24              |

| 1000                | 17                 | Reserved        |

| 1001                | 25                 | Reserved        |

| 1010                | 49                 | Reserved        |

| 1011                | Reserved           | Reserved        |

| 1100                | Reserved           | Reserved        |

| 1101                | Reserved           | Reserved        |

| 1110                | Reserved           | Reserved        |

# 5. Setting Interrupts

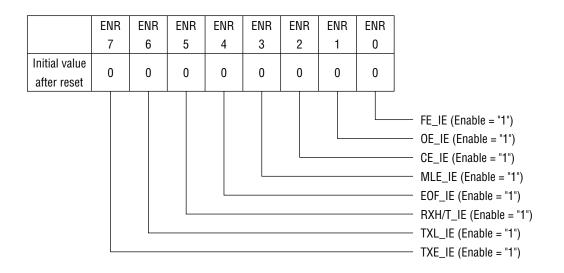

The MSM9405 has 9 factors of interrupts. Bit 7 (TXE\_EV), bit 6 (TXL\_EV), bit 5 (RXH/T\_EV), bit 4 (EOF\_EV), bit 3 (MLE\_EV), bit 2 (CE\_EV), bit 1 (OE\_EV), bit 0 (FE\_EV) of the EIR register (address 2h), and bit 0 (TOUT) of the LSR register (address 3h) indicate interrupts, and change to 1 when an interrupt occurs.

The ENR register (address 1h) can enable and disable each interrupt. All 8 bits correspond to the bit array of the interrupts indicated by the EIR register. Enable necessary interrupts by setting the corresponding bits to 1. Setting a bit to 0 disables the corresponding interrupt. Even if the corresponding bits in the ENR register are 0 (disabled) each bit of the EIR register will still change to 1 when an interrupt event occurs.

#### 5.1 TXE\_EV, TXE\_IE

TXE\_EV is set to 1 if all of the data written in the FIFO is transmitted and both the FIFO and TSR (Transmitter Shift Register: See APPENDIX-A "Block Diagram") become empty. If the EIR register is read, it is reset to 0. TXE\_EV will be set to 1 if the FIFO and TSR become empty not only in the middle of a frame, but also after normal completion of a frame transfer.

The significance of TXE\_EV differs depending upon the transfer mode and the generated timing. When in the MIR or FIR mode, if an interrupt occurs before 1 frame of data has been written to the FIFO, TXE\_EV indicates that the transmit data write was not complete, and that the data is fragmented. In this case, data written hereafter to the FIFO will not be transmitted. To restart transmission, it is necessary to first reset TX\_EN to 0 and then set TX\_EN to 1.

In all the modes (SIR, Ex-SIR, MIR and FIR), if an interrupt occurs after 1 frame of data has been written to the FIFO, TXE\_EV indicates that transmission of that frame is complete.

TXE\_IE enables and disables the interrupt asserted by TXE\_EV.

TXE\_IE and TXE\_EV are valid in all the modes (SIR, Ex-SIR, MIR and FIR).

#### 5.2 TXL\_EV, TXL\_IE

During the transmit or idle mode, if the number of transmit data bytes in the FIFO is less than the transmit threshold level set by bits 3 through 0 (TXTH3 to TXTH0) of the FCR register (address 8h), then TXL\_EV is set to 1 (See section 7.1, "Setting the Transmit/Receive Threshold Levels"). Transmit data is written to the FIFO and if the number of transmit data bytes in the FIFO is equal to or greater than the transmit threshold level, TXL\_EV is set to 0.

In the receive mode, TXL\_IE is always set to 0.

TXL\_EV is a trigger to write the transmit data.

TXL\_IE enables and disables the interrupt asserted by TXL\_EV.

TXL\_IE and TXL\_EV are valid in all the modes (SIR, Ex-SIR, MIR and FIR).

# 5.3 RXH/T\_EV, TOUT, RXH/T\_IE

When in the receive mode, RXH/T\_EV is set to 1 if the number of receive data bytes in the FIFO is equal or greater than the receive threshold level (See section 7.1, "Setting the Transmit/Receive Threshold Levels) set by bits 7 through 4 (RXTH3 to RXTH0) of the FCR register (address 8h) or if a timeout is generated. When a timeout is generated, bit 0 (TOUT) of the LSR register (address 3h) is also set to 1. If RXH/T\_EV has been set to 1 because the received number of data bytes is equal or greater than the receive threshold level, the received data is read. And the number of received data bytes in the FIFO is less than the receive threshold level, RXH/T\_EV is set to 0. If RXH/T\_EV has been set to 1 due to generation of a timeout, RXH/T\_EV will be reset to 0 when the received data is read. TOUT will also be reset to 0 when the received data is read. In the transmit and idle modes, RXH/T\_EV is always set to 0.

The condition causing timeout in the SIR and Ex-SIR modes:

At least 1 or more bytes of data are in the FIFO and time Tout has elapsed since the last data was written from the receiver shift register (RSR) to the FIFO. During this interval, FIFO data has not been read by the CPU or DMA controller.

Tout =  $4 \times 8 \times 1$ /baud rate baud rate: transfer speed (2.4 to 115.2 kbps) The condition causing timeout in the MIR and FIR modes:

At least 1 or more bytes of data are in the FIFO and 69.5  $\mu$ s has elapsed since the last data was written from the receiver shift register to the FIFO. During this interval, FIFO data has not been read by the CPU or DMA controller. RXH/T\_IE enables and disables the interrupt asserted by RXH/T\_EV.

RXH/T\_EV is a trigger to read the receive data.

RXH/T\_EV, RXH/T\_IE, and TOUT are valid in all the modes (SIR, Ex-SIR, MIR and FIR).

# 5.4 EOF\_EV, EOF\_IE

During the receive mode, EOF\_EV is set to 1 when the last byte of the information section of the receive frame reaches the bottom of the FIFO (= RDR). If the EIR register is read, EOF\_EV is set to 0.

EOF\_EV indicates that the next data to be read is the last data in the frame.

EOF\_IE enables and disables the interrupt asserted by EOF\_EV.

EOF\_IE and EOF\_EV are valid in the Ex-SIR, MIR and FIR modes.

In the SIR mode, set EOF\_IE to 0 and do not use EOF\_EV.

### 5.5 MLE\_EV, MLE\_IE

During the receive mode, MLE\_EV is set to 1 when a frame is received whose length exceeds the maximum receive data size as set by the MDS(L) and MDS(H) registers (addresses Bh, Ch). If the EIR register is read, MLE\_EV will be reset to 0.

MLE\_IE enables and disables the interrupt asserted by MLE\_EV.

MLE \_IE and MLE \_EV are valid in the Ex-SIR, MIR and FIR modes.

In the SIR mode, set MLE\_IE to 0 and do not use MLE\_EV.

The data size set in the MDS register does not include CE, FCS, BOF and EOF. (In the SIR mode,

set MLE\_IE to 0 and do not use MLE\_EV.)

CE (Control Escape Byte) = 7D

FCS (Frame Check Sequence) = Ex-SIR, MIR: CRC16 FIR:CRC32

# 5.6 CE\_EV, CE\_IE

In the receive mode, a CRC check of the receive frame is performed and CE\_EV is set to 1 when an error occurs.

If the EIR register is read, CE\_EV will be reset to 0.

CE\_EV indicates that there is an error in the received frame.

CE \_IE enables and disables the interrupt asserted by CE \_EV.

CE\_IE and CE\_EV are valid in the Ex-SIR, MIR and FIR modes.

In the SIR mode, set CE\_IE to 0 and do not use CE\_EV.

# 5.7 OE\_EV, OE\_IE

During the receive mode, OE\_EV is set to 1 when the FIFO already full of 32 bytes of receive data, and the next receive data is completely received in the receiver shift register (RSR) (See Appendix-A, "Block Diagram").

If the EIR register is read, OE\_EV will be reset to 0.

When OE\_EV is asserted, data in the RSR is not written to the FIFO. Data in the receiving shift register will be overwritten by the next receive data.

OE \_EV indicates that the received data could not be read and a portion of the received data is lost.

Even if OE\_EV is asserted, CE\_EV will not be asserted.

OE \_IE enables and disables the interrupt asserted by OE \_EV.

OE \_IE and OE \_EV are valid in all the modes (SIR, Ex-SIR, MIR and FIR modes).

#### 5.8 FE\_EV, FE\_IE

In the receive mode, FE\_EV is set to 1 if there is no stop bit in the received data.

If the EIR register is read, FE\_EV will be reset to 0.

FE \_IE enables and disables the interrupt asserted by FE \_EV.

FE \_IE and FE \_EV are valid in the SIR and Ex-SIR modes.

In the MIR and FIR modes, set FE\_IE to 0 and do not use FE\_EV.

# 6. How to Add FCS/EOF

FCS (Frame Check Sequence) = Ex-SIR, MIR: CRC16 FIR: CRC32

#### 6.1 How to Use S\_EOT

Disable TCC by setting bit 6 (TCC\_EN) of the ICR1 (address 4h) register to 0 or set the value greater than the number of bytes (Note) of the frame to be transmitted to the TFL register (addresses 9h and Ah). Set the operating mode of the MSM9405 to transmit by setting the ICR1 register's bit 1 (RX\_EN) to 0 and bit 0 (TX\_EN) to 1. Write the transmit data to the TDR register. Just prior to writing the last data of the frame, write a 1 to bit 4 (S\_EOF) of the ICR1 register. The MSM9405 will recognize data written to the TDR register as the last data of that frame, FCS and EOF (STO) are then added and the frame is transmitted. After EOF is transmitted, S\_EOF is automatically reset to 0.

#### 6.2 How to Use TFL/TCC

Enable TCC by setting bit 6 (TCC\_EN) of the ICR1 register to 1 and set the number of bytes (Note) of the frame to be transmitted to the TFL register. Set the operating mode of the MSM9405 to the transmit mode by setting the ICR1 register's bit 1 (RX\_EN) to 0 and bit 0 (TX\_EN) to 1. Write the transmit data to the TDR register. When 1 is written in TX\_EN, the value of TFL previously set as a frame length is loaded into TCC.

TCC is a counter to count down the number of transmit data bytes.

The value of TCC is decremented by 1 each time when 1 Byte is transmitted.

When the value of TCC is zero, the MSM9405 recognizes that the last data byte of the frame has been transmitted and automatically transmits FCS and EOF together with it.

When BOF of the next frame is transmitted, the value of TFL is loaded into TCC again.

Set CTEST (bit 7 of the ICR2 register) to 1 to access TFL and set CTEST to 0 to read TCC.

#### 6.3 How to Use TC

The TC signal can be used when writing data with a DMA controller that has a TC output. Disable TCC by setting bit 6 (TCC\_EN) of the ICR1 register to 0 or set the value greater than the number of bytes (Note) of the frame to be transmitted to the TFL register. Set the operating mode of the MSM9405 to transmit by setting the ICR1 register's bit 1 (RX\_EN) to 0 and bit 0 (TX\_EN) to 1. Write the transmit data to the TDR register. When the TC signal is received from the DMA controller, the data written at that time will be recognized as the end of the frame, FCS and EOF (STO) will be added and the frame transmit.

Note: Number of bytes of the frame does not include CE, FCS, BOF (STA), and EOF (STO).

# 7. FIFO

### 7.1 Setting the Transmit/Receive Threshold Levels

The MSM9405 can set the receive threshold level with bits 7 to 4 (RXTH3 to RXTH0) of the FCR register (address 8h) and the transmit threshold level with bits 3 to 0 (TXTH3 to TXTH0) of the FCR register.

In the receive mode, if the number of receive data bytes in the FIFO is equal to or greater than the receive threshold level set in the FCR register, an RXH interrupt is generated and RXH/T\_EV of the EIR register is set to 1. (If DMA has been enabled, the DREQ signal will be asserted.) In this state, the FIFO data is read, and if the number of data bytes in the FIFO becomes less than the receive threshold level, RXH/T\_EV is set to 0. (The FIFO data is read and when the number of data bytes in the FIFO becomes the same as the value set by DMATH (See section 3.3, "Setting the DMAC Interface"), the DREQ signal will be deasserted.)

In the transmit mode, if the number of receive data bytes in the FIFO is less than the transmit threshold level set in the FCR register, a TXL interrupt is generated and TXL\_EV of the EIR register is set to 1. (If DMA has been enabled, the DREQ signal will be asserted.) In this state, the data is written to the FIFO, and if the number of data bytes in the FIFO becomes equal or greater than the transmit threshold level, TXL\_EV is set to 0. (Data is written to the FIFO and when the number of data bytes in the FIFO becomes the same as the value set by DMATH, the DREQ signal will be deasserted.)

When setting the transmit and receive threshold levels, a value smaller than the value set by DMATH should be set to TXTH during transmission, and a value greater than the value set by DMATH should be set to RXTH during reception.

| bit 3 to bit 0<br>(bit 7 to bit 4 for reception) | TX Threshold Level | RX Threshold Level |

|--------------------------------------------------|--------------------|--------------------|

| 0000                                             | Reserved           | Reserved           |

| 0001                                             | 02                 | 02                 |

| 0010                                             | 04                 | 04                 |

| 0011                                             | 06                 | 06                 |

| 0100                                             | 08                 | 08                 |

| 0101                                             | 10                 | 10                 |

| 0110                                             | 12                 | 12                 |

| 0111                                             | 14                 | 14                 |

| 1000                                             | 16                 | 16                 |

| 1001                                             | 18                 | 18                 |

| 1010                                             | 20                 | 20                 |

| 1011                                             | 22                 | 22                 |

| 1100                                             | 24                 | 24                 |

| 1101                                             | 26                 | 26                 |

| 1110                                             | 28                 | 28                 |

| 1111                                             | 30                 | 30                 |

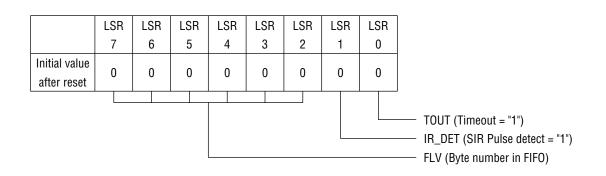

## 7.2 Number of Data Bytes in the FIFO

When in the transmit mode, bits 7 to 2 (FLV5 to FLV0) of the LSR register (address 3h) indicate the number of transmit data bytes currently in the FIFO. When in the receive mode, these bits indicate the number of receive data bytes currently in the FIFO. Bit 7 indicates MSB, and bit 2 indicates LSB.

A maximum of 85ns (at original oscillation of 48MHz) is required from the time when FIFO data is accessed until the value of the LSR register changes. (When the original oscillation is 18.432MHz, the maximum time is 130ns.)

Data in the FIFO (including TDR and RDR) and FLV5 through FLV0 are cleared by writing 1 to bit 4 (FCLR) of the ICR1 register (address 4h). After data is cleared in the FIFO, FCLR is automatically set to 0.

## 7.3 FCLR

The MSM9405 can clear data in the FIFO by using FCLR (bit 4 of the ICR1).

Setting the FCLR to "1" clears the FIFO (including TDR and RDR) and sets the FLV to "0". The TSR and RSR (Transmitter Shift Register and Receive Shift Register: see Appendix-A, "Block Diagram") are not cleared. The FCLR is automatically set to "0".

\* In the transmit mode or idle mode, in case the FCLR has cleared the FIFO when the number of data bytes is more than the transmit threshold level, the TXL\_EV event does not occur and the INTR and DREQ pins do not become active.

When starting transmission after clearing the FIFO, the following operations should be performed.

- 1. Set the idle mode.

- 2. Write 1 byte of dummy data to FIFO.

- 3. Clear the dummy data written to FIFO by using FCLR.

- 4. Start transmission.

## 8. Other Functions

## 8.1 How to Use IR\_DET

Infrared pulses can be detected by monitoring bit 1 (IR\_DET) of the LSR register (address 3h). In the SIR and Ex-SIR modes, if a 0.9s (minimum value of SIR pulse width during reception) or longer pulse is input to IRIN-A pin, IR\_DET will be set to 1. If IR\_DET is read, it is reset to 0. IR\_DET is not used in the MIR and FIR modes.

IR\_DET is cleared by setting FCLR to 1.

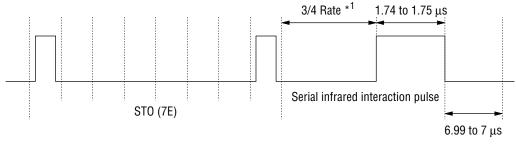

## 8.2 How to Send Serial Infrared Interaction Pulses

Setting bit 3 (IR\_PLS) of the ICR1 register (address 4h) to 1 causes a serial infrared interaction pulse to be output. After the interaction pulse is output, IR\_PLS is automatically set to 0. After IR\_PLS is set to 1, a serial infrared interaction pulse is output immediately after the first STO that is output.

Serial infrared interaction pulses are only output in the MIR and FIR modes. Serial infrared interaction pulses are not output in the SIR and Ex-SIR modes.

In MIR mode

\*1 Rate: 1/transfer speed

## 8.3 Inverted CRC

In the MIR and FIR modes, if TXE\_EV is asserted during a frame transfer, the MSM9405 has a function to transmit inverted CRC (Note) and EOF, and to terminate subsequent data transmission. This function is enabled by setting bit 5 (CRC\_INV) of the ICR1 register (address 4h) to 1, and is disabled by setting that bit to 0.

To restart data transmission that has been stopped by the assertion of TXE\_EV, it is necessary to set bit 0 (TX\_EN) of the ICR1 register to 0, and then set TX\_EN to 1 again. This function is invalid in the SIR and Ex-SIR modes.

Note: Inverted CRC is obtained by calculating the CRC of data transmitted before the TXE\_EV event accurs, and then inverting all the calculated bits.

## 8.4 RST

The RST register (address Bh, Ch) is a register that stacks receive frame lengths. When one frame is completely received and EOF\_EV (bit 4) of the EIR register (address 2h) has become 1, the receive frame length counted by the internal counter is pushed onto the RST register.

If the next frame is completely received and EOF\_EV is set again to 1, the register value will be overwritten. If data from two or more frames is received together, read RST at every 1-frame reception.

Even if transmission and reception of the MSM9405 are switched, the RST value will be maintained.

RST can be read while bit 7 (CTEST) of the ICR2 register (address 5h) is 0. It is not possible to write to RST. While CTEST is 1, MDS will be read.

RST is valid in the Ex-SIR, MIR and FIR modes. RST is not used in the SIR mode.

## Appendix A

# **Block Diagram**

# Appendix A Block Diagram

- SD

**OKI** Semiconductor

P-1

$V_{DD}$  —

A<sub>0-3</sub>

$\overline{\text{CS}}$

RD

WR —

INTR 🗕

RESET -

PWDN

тс

DREQ 🔫

DACK

XIN

XOUT 🛥

TEST 🗕

8

Microcontroller I/F

DMA

I/F

OSC

D<sub>0-7</sub>

GND -

8

8

Control/Status

Register

DMA

**Control Circuit**

TCC/RCC

**Receiver Shift** Register (RSR)

Transmit-Receive FIFO

$(32 \times 8 \text{ bit})$

Transmitter Shift Register (TSR)

Baud Rate

Generator

8

8

## Appendix B

# **Electrical Characteristics**

## Appendix B Electrical Characteristics

## Absolute Maximum Ratings

| Parameter           | Symbol           | Condition | Rating       | Unit |

|---------------------|------------------|-----------|--------------|------|

| Supply Voltage      | V <sub>DD</sub>  | —         | -0.5 to +4.6 | V    |

| Input Voltage       | VI               |           | -0.5 to +6.0 | V    |

| Output Current      | I <sub>0</sub>   |           | ±10          | mA   |

| Power Dissipation   | PD               |           | 230          | mW   |

| Storage Temperature | T <sub>STG</sub> |           | -55 to +150  | °C   |

## **Recommended Operating Conditions**

| Parameter             | Symbol          | Condition | Range                                  | Unit |

|-----------------------|-----------------|-----------|----------------------------------------|------|

| Supply Voltage        | V <sub>DD</sub> | —         | 2.7 to 3.6                             | V    |

| Operating Temperature | T <sub>op</sub> | —         | -20 to +70                             | °C   |

| Crystal Oscillation   | fooo            |           | 18.432 MHz ±200 ppm or 48 MHz ±100 ppm |      |

| Frequency             | tosc            |           |                                        |      |

## **DC Characteristics**

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{ Ta} = -20 \text{ to } +70^{\circ}\text{C})$

| Parameter             | Symbol           | Condition             | Min.              | Тур.  | Max.     | Unit | Applicable Pin                                                         |

|-----------------------|------------------|-----------------------|-------------------|-------|----------|------|------------------------------------------------------------------------|

| "H" Input Voltage     | V <sub>IH1</sub> | —                     | 2.1               | —     | 5.5      | v    | IRIN-A, IRIN-B, PWDN                                                   |

| "L" Input Voltage     | V <sub>IL1</sub> | —                     | 0                 | —     | 0.8      | v    | $A_0$ to $A_3$ , $\overline{CS}$ , $\overline{RD}$ , $\overline{WR}$ , |

| Input Leakage Current | I <sub>LI1</sub> | $V_I = V_{DD}/0 V$    | —                 | —     | ±10      | μA   | TC, <u>RESET</u> , DACK                                                |

| "H" Input Voltage     | V <sub>IH2</sub> | —                     | 2.1               | —     | 5.5      | v    |                                                                        |

| "L" Input Voltage     | V <sub>IL2</sub> | —                     | 0                 | —     | 0.8      | v    |                                                                        |

| Input Leakage Current | I <sub>LI2</sub> | $V_I = V_{DD}/0 V$    | —                 | —     | ±10      | μA   | D <sub>0</sub> to D <sub>7</sub>                                       |

| "H" Output Voltage    | V <sub>OH1</sub> | $I_0 = -4 \text{ mA}$ | 2.2 <sup>*1</sup> | —     | $V_{DD}$ | v    |                                                                        |

| "L" Output Voltage    | V <sub>0L1</sub> | $I_0 = 4 \text{ mA}$  | —                 | —     | 0.4      | v    |                                                                        |

| "H" Output Voltage    | V <sub>0H2</sub> | $I_0 = -4 \text{ mA}$ | 2.2 <sup>*1</sup> | —     | $V_{DD}$ | v    |                                                                        |

| "L" Output Voltage    | V <sub>0L2</sub> | $I_0 = 4 \text{ mA}$  | —                 | — — 0 |          | V    | IROUT, INTR, DREQ, SD                                                  |

| Supply Current        | I <sub>DD</sub>  |                       | —                 | —     | 30       | mA   | V <sub>DD</sub>                                                        |

\*1 2.4 V when  $V_{DD}$  = 3.0 to 3.6 V

#### **AC Characteristics**

| Parameter                     | Symbol            | Condition   | Min.   | Тур. | Max.   | Unit | Note   |

|-------------------------------|-------------------|-------------|--------|------|--------|------|--------|

| Read Pulse Width              | t <sub>rpw</sub>  | _           | 120/70 |      | _      | ns   | *1     |

| Read Data Delay Time          | t <sub>rdd</sub>  | _           | _      |      | 60     | ns   | *3, *5 |

| Read Data Hold Time           | t <sub>rdh</sub>  | _           | 0      |      | _      | ns   | *4, *6 |

| Data Bus Open Time            | t <sub>hz</sub>   | _           | _      |      | 25     | ns   |        |

| Read/Write Recovery Time      | t <sub>rcv</sub>  | _           | 60     |      | _      | ns   |        |

| CS Setup Time                 | t <sub>css</sub>  | _           | 60     |      | _      | ns   |        |

| CS Hold Time                  | t <sub>csh</sub>  | _           | 0      |      |        | ns   |        |

| Write Address Hold Time       | t <sub>wah</sub>  | _           | 0      |      |        | ns   |        |

| Write Pulse Width             | t <sub>wpw</sub>  | _           | 120/70 |      | _      | ns   | *1     |

| Write Data Setup Time         | t <sub>wds</sub>  | _           | 60     |      | _      | ns   | *7     |

| Write Data Hold Time          | t <sub>wdh</sub>  | _           | -10    |      | _      | ns   | *7     |

| Write Address Setup Time      | t <sub>was</sub>  | _           | -10    |      | _      | ns   |        |

| Interrupt Clear Time          | t <sub>intr</sub> | _           | _      |      | 135/95 | ns   | *2     |

| DACK Setup Time               | t <sub>acs</sub>  | _           | 60     |      | _      | ns   |        |

| DREQ Clear Time               | t <sub>drqr</sub> | _           | _      |      | 80     | ns   | *8     |

| DACK Hold Time (during Read)  | t <sub>achr</sub> | _           | 60     |      | _      | ns   |        |

| DACK Hold Time (during Write) | t <sub>achw</sub> | _           | 60     |      | _      | ns   |        |

| TC Pulse Width                | t <sub>tcw</sub>  | _           | 25     |      | _      | ns   |        |

| TC Setup Time                 | t <sub>tcs</sub>  | _           | 15     |      | _      | ns   |        |

| TC Hold Time                  | t <sub>tch</sub>  | _           | 15     |      | _      | ns   |        |

|                               |                   | Transmitter | _      | 1.63 | _      | μs   |        |

| SIR Pulse Width               | t <sub>spw</sub>  | Receiver    | 0.9    |      | _      | μs   |        |

|                               | ODDT              | Transmitter | _      |      | ±0.87  | %    |        |

| SIR Data Rate Tolerance       | SDRT              | Receiver    | _      |      | ±1.0   | %    |        |

|                               |                   | Transmitter | _      | 218  | _      | ns   |        |

| MIR Pulse width               | t <sub>mpw</sub>  | Receiver    | 100    |      | _      | ns   |        |

|                               | MDDT              | Transmitter | _      |      | ±0.1   | %    |        |

| MIR Data Rate Tolerance       | MDRT              | Receiver    |        |      | ±0.2   | %    |        |

|                               |                   | Transmitter | _      | 125  | _      | ns   |        |

| FIR Single Pulse Width        | t <sub>fpw</sub>  | Receiver    | 70     |      | 165    | ns   |        |

|                               | FDDT              | Transmitter | _      |      | ±0.01  | %    |        |

| FIR Data Rate Tolerance       | FDRT              | Receiver    | _      |      | ±0.1   | %    |        |

|                               |                   | Transmitter | —      | 250  |        | ns   |        |

| FIR Double Pulse Width        | t <sub>fdpw</sub> | Receiver    | 195    |      | 285    | ns   |        |

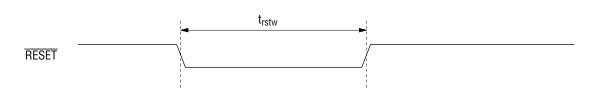

| Reset Pulse Width             | t <sub>rstw</sub> |             | 70     |      | _      | ns   |        |

\*1 120 ns when the master oscillation frequency is 18.432 MHz, and 70 ns when it is 48 MHz.

\*2 135 ns when the master oscillation frequency is 18.432 MHz, and 95 ns when it is 48 MHz.

\*3 That which occurs latest of the following is to be used for the data delay time  $(t_{rdd})$ : the change from  $A_0$ - $A_3$  invalid to valid, the change from  $\overline{CS}$  high to low, and the change from  $\overline{RD}$  high to low (in the PIO mode).

- \*4 That which occurs first of the following is to be used for the read data hold time  $(t_{rdh})$ : the change from  $A_0$ - $A_3$  valid to invalid, the change from  $\overline{CS}$  low to high, and the change from  $\overline{RD}$  low to high.

- \*5 That which occurs latest of the following is to be used for the data delay time  $(t_{rdd})$ : the change from DACK inactive to active and the change from  $\overline{RD}$  high to low (in the DMA mode).

- \*6 That which occurs first of the following is to be used for the read data hold time  $(t_{rdd})$ : the change from DACK active to inactive and the change from  $\overline{RD}$  low to high (in the DMA mode).

- \*7 That which occurs first of the following is to be used for the write data setup time and write data hold time (t<sub>wds</sub> and t<sub>wdh</sub>): the change from DACK active to inactive and the change from WR low to high.

- \*8 That which occurs latest of the following is to be used for the DREQ clear time ( $t_{drqr}$ ): the change from DACK low to high and the change from WR (or RD) high to low.

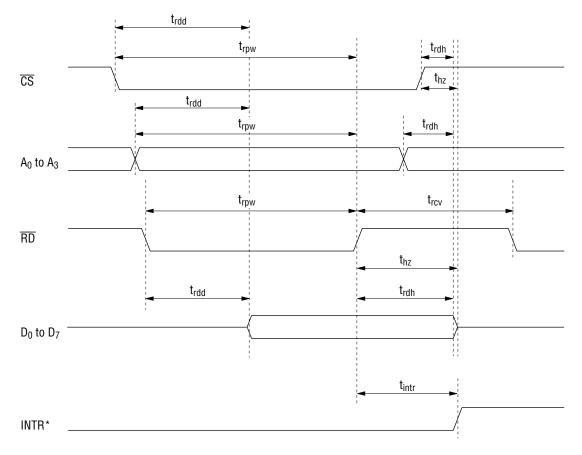

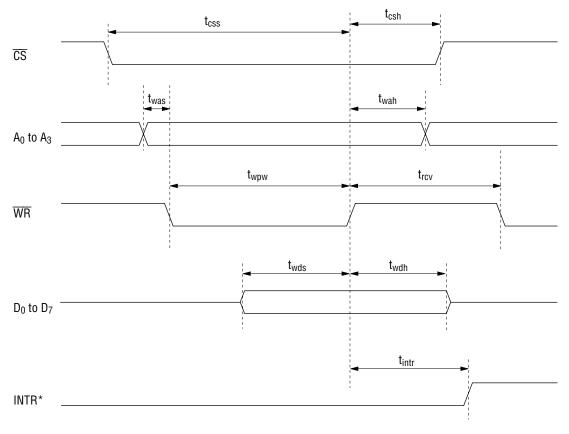

## Appendix C

# **Timing Diagram**

## Appendix C Timing Diagram

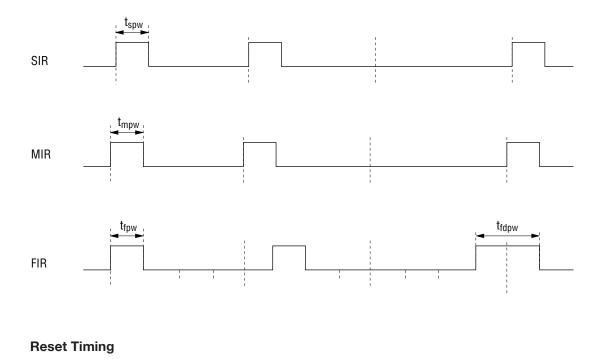

## **Read Timing**

\* When the INTR pin is active low.

## Write Timing

\* When the INTR pin is active low.

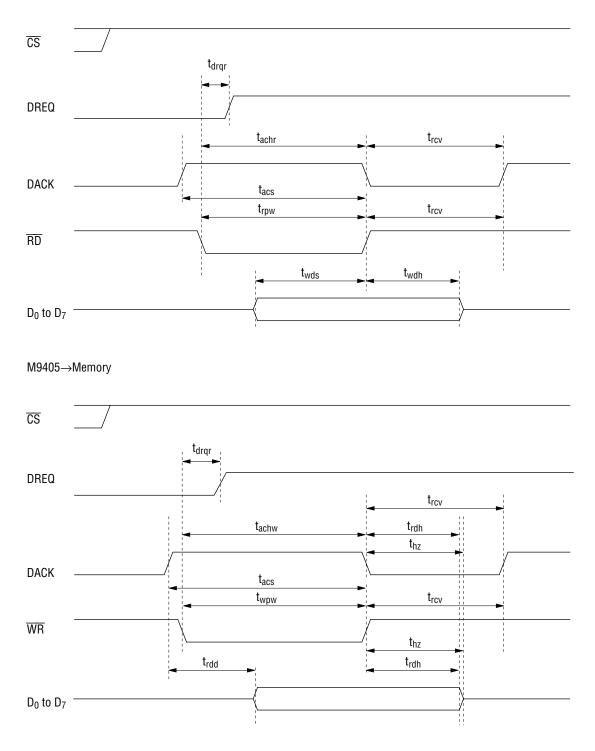

## DMAC Access Timing 1

DMA\_EN = "1", DMA\_SL<sub>1</sub> = "0", DMA\_SL<sub>0</sub> = "0", DREQ: active low, DACK: active high Memory $\rightarrow$ M9405

## **DMAC Access Timing 2**

DMA\_EN = "1", DMA\_SL<sub>1</sub> = "0", DMA\_SL<sub>0</sub> = "1", DREQ: active low, DACK: active high M9405 $\rightarrow$ Memory

\* When the TC pin is active low.

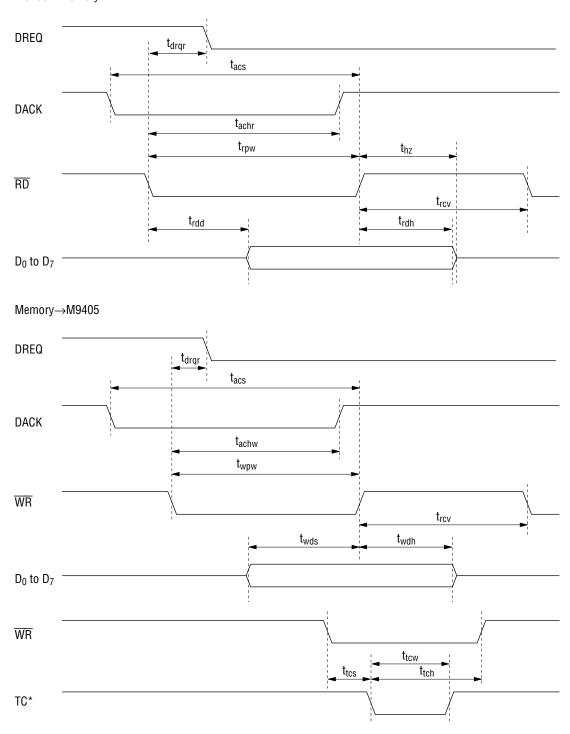

## **DMAC Access Timing 3**

DMA\_EN = "1", DMA\_SL<sub>1</sub> = "1", DMA\_SL<sub>0</sub> = "1" or "0", DREQ: active high M9405 $\rightarrow$ Memory

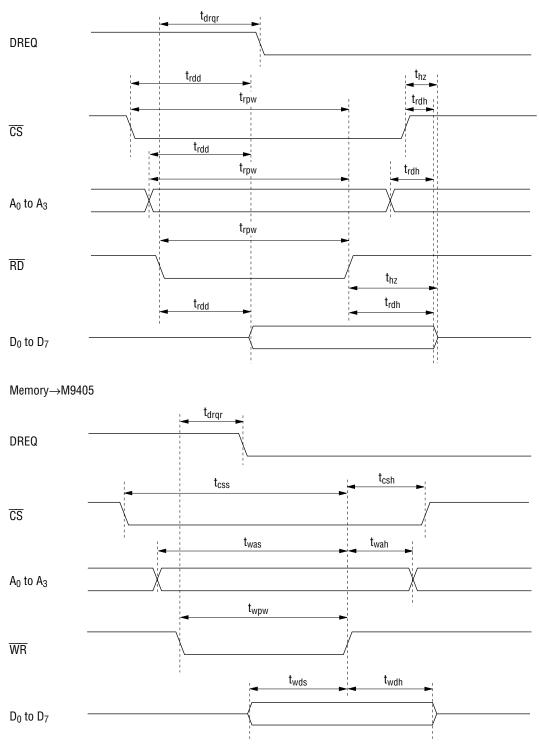

## Infrared Interface Timing

## Appendix D

# **Register Table**

## Appendix D Register Table

## **Register Table**

| Add | Register | Mode          | R/W          |                                       |                                       | Fu                                    | unction                               | of each l                             | oit                                   |                                       |                                       |                  |

|-----|----------|---------------|--------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|------------------|

| Add | name     | wode          | R/W          | Bit7                                  | Bit6                                  | Bit5                                  | Bit4                                  | Bit3                                  | Bit2                                  | Bit1                                  | Bit0                                  |                  |

| 0   | TDR/RDR  | all           | R/W          | TDR <sub>7</sub><br>/RDR <sub>7</sub> | TDR <sub>6</sub><br>/RDR <sub>6</sub> | TDR <sub>5</sub><br>/RDR <sub>5</sub> | TDR <sub>4</sub><br>/RDR <sub>4</sub> | TDR <sub>3</sub><br>/RDR <sub>3</sub> | TDR <sub>2</sub><br>/RDR <sub>2</sub> | TDR <sub>1</sub><br>/RDR <sub>1</sub> | TDR <sub>0</sub><br>/RDR <sub>0</sub> |                  |

| 1   | ENR      | SIR<br>Ex-SIR | R/W          | TXE_IE                                | TXL_IE                                | RXH/T                                 | *                                     | MLE_IE                                | *                                     | OE_IE                                 | FE_IE                                 |                  |

|     |          | MIR<br>FIR    |              |                                       |                                       | _IE                                   | EOF_IE                                |                                       | CE_IE                                 | 0                                     | *                                     |                  |

| 2   | EIR      | SIR<br>Ex-SIR | R            | TXE_EV                                | TXL_EV                                | RXH/T                                 | *                                     | MLE_EV                                | *                                     | OE_EV                                 | FE_EV                                 |                  |

|     |          | MIR<br>FIR    |              |                                       |                                       | _EV                                   | EOF_EV                                |                                       | CE_EV                                 | 01_11                                 | *                                     |                  |

| 3   | LSR      | all           | R            | FLV <sub>5</sub>                      | FLV4                                  | FLV3                                  | FLV <sub>2</sub>                      | FLV <sub>1</sub>                      | FLV <sub>0</sub>                      | IR_DET                                | TOUT                                  |                  |

|     |          | SIR           |              |                                       |                                       | *                                     |                                       | *                                     | *                                     | _                                     |                                       |                  |

| 4   | 4 ICR1   | Ex-SIR        | R/W          | MS_EN                                 | TCC_EN                                | CRC_                                  | FCLR                                  |                                       |                                       | RX_EN                                 | TX_EN                                 |                  |

|     | Ion      | MIR<br>FIR    | 1000         | NIO_EN                                | TOO_EN                                | INV                                   | TOEN                                  | IR_PLS                                | S_EOT                                 |                                       | IX_EN                                 |                  |

|     |          | SIR           |              |                                       |                                       |                                       |                                       | *                                     | *                                     | *                                     | *                                     |                  |

| 5   | ICR2     | Ex-SIR        | R/W          | CTEST                                 | SD_INV                                | IRIN                                  | RXINV                                 | SBF <sub>3</sub>                      | SBF <sub>2</sub>                      | SBF <sub>1</sub>                      | SBF <sub>0</sub>                      |                  |

| -   | -        | MIR           |              |                                       |                                       | _SL                                   |                                       |                                       | MBF <sub>3</sub>                      | MBF <sub>2</sub>                      | MBF <sub>1</sub>                      | MBF <sub>0</sub> |

|     |          | FIR           | <b>6</b> 4 4 |                                       |                                       |                                       |                                       | *                                     | *                                     | *                                     | *                                     |                  |

| 6   | MSR      | all           | R/W          | DRS <sub>2</sub>                      | DRS <sub>1</sub>                      | DRS <sub>0</sub>                      | XT_SL                                 | *                                     | *                                     | IRSL1                                 | IRSL <sub>0</sub>                     |                  |

| 7   | DSR      | all           | R/W          | DREQ_<br>INV                          | DACK_<br>INV                          | TC_<br>INV                            | DMATH1                                | DMATH0                                | DMA_<br>SL <sub>1</sub>               | DMA_<br>SL <sub>0</sub>               | DMA_<br>EN                            |                  |

| 8   | FCR      | all           | R/W          | RXTH <sub>3</sub>                     | RXTH <sub>2</sub>                     | RXTH <sub>1</sub>                     | RXTH <sub>0</sub>                     | TXTH <sub>3</sub>                     | TXTH <sub>2</sub>                     | TXTH <sub>1</sub>                     | TXTH <sub>0</sub>                     |                  |

| 9   | TFL (L)  | all           | R/W          | TFL <sub>7</sub>                      | TFL <sub>6</sub>                      | TFL <sub>5</sub>                      | TFL <sub>4</sub>                      | TFL <sub>3</sub>                      | TFL <sub>2</sub>                      | TFL <sub>1</sub>                      | TFL <sub>0</sub>                      |                  |

|     | TCC (L)  | all           | R            | TCC7                                  | TCC <sub>6</sub>                      | TCC <sub>5</sub>                      | TCC4                                  | TCC3                                  | TCC <sub>2</sub>                      | TCC1                                  | TCC0                                  |                  |

| А   | TFL (H)  | all           | R/W          | *                                     | *                                     | *                                     | *                                     | TFL <sub>11</sub>                     | TFL <sub>10</sub>                     | TFL <sub>9</sub>                      | TFL <sub>8</sub>                      |                  |

|     | TCC (H)  | all           | R            | *                                     | *                                     | *                                     | *                                     | TCC <sub>11</sub>                     | TCC <sub>10</sub>                     | TCC <sub>9</sub>                      | TCC8                                  |                  |

| В   | MDS (L)  | all           | R/W          | MDS <sub>7</sub>                      | MDS <sub>6</sub>                      | MDS <sub>5</sub>                      | MDS <sub>4</sub>                      | MDS <sub>3</sub>                      | MDS <sub>2</sub>                      | MDS <sub>1</sub>                      | MDS <sub>0</sub>                      |                  |

|     | RST (L)  | all           | R            | RST <sub>7</sub>                      | RST <sub>6</sub>                      | RST <sub>5</sub>                      | RST <sub>4</sub>                      | RST <sub>3</sub>                      | RST <sub>2</sub>                      | RST <sub>1</sub>                      | RST <sub>0</sub>                      |                  |

| С   | MDS (H)  | all           | R/W          | *                                     | *                                     | *                                     | *                                     | MDS <sub>11</sub>                     | MDS <sub>10</sub>                     | MDS <sub>9</sub>                      | MDS <sub>8</sub>                      |                  |

|     | RST (H)  | all           | R            | *                                     | *                                     | *                                     | *                                     | RST <sub>11</sub>                     | RST <sub>10</sub>                     | RST <sub>9</sub>                      | RST <sub>8</sub>                      |                  |

| D   | ISR      | all           | R/W          | *                                     | *                                     | *                                     | *                                     | *                                     | *                                     | *                                     | INTR_<br>INV                          |                  |

| F   | TEST     | all           | R/W          | TEST <sub>7</sub>                     | TEST <sub>6</sub>                     | TEST <sub>5</sub>                     | TEST <sub>4</sub>                     | TEST <sub>3</sub>                     | TEST <sub>2</sub>                     | TEST <sub>1</sub>                     | TEST <sub>0</sub>                     |                  |

\* Reserved

## Registers

## 1. TDR: Transmitter Data Register (Write Only) RDR: Receiver Data Register (Read Only) (Address = 0h)