# **OKI** Semiconductor

# **MSM9200-xx**

This version: Nov. 1997 Previous version: Jul. 1996

#### $5 \times 7$ Dot Character $\times$ 16-Digit Display Controller/Driver with Character RAM

### **GENERAL DESCRIPTION**

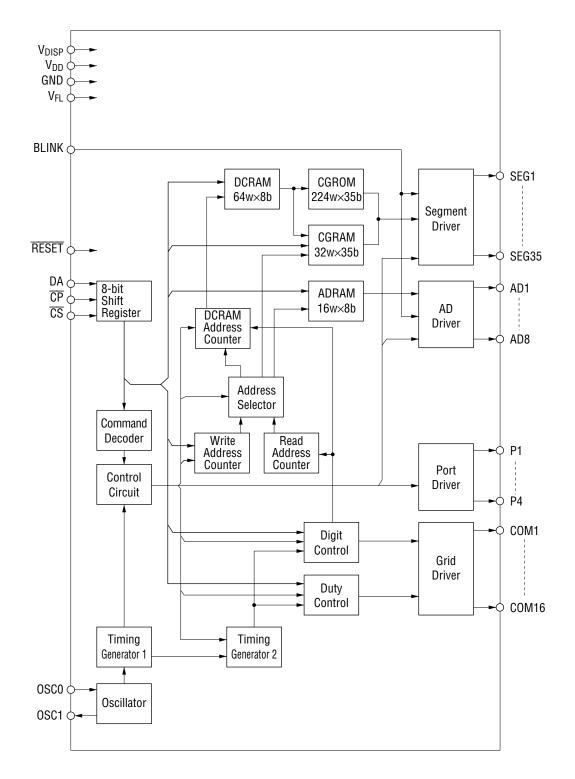

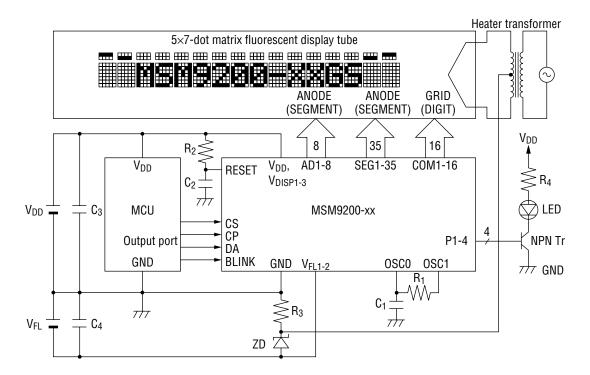

The MSM9200-xx is a dot matrix vacuum fluorescent display tube controller driver IC which displays characters, numerics and symbols.

Dot matrix vacuum fluorescent display tube drive signals are generated by serial data sent from a microcontroller. A display system is easily realized by internal ROM and RAM for character display.

The MSM9200-xx has low power consumption because it is munufactured in CMOS process technology.

-01 and -02 are available as general codes.

Custom codes are provided if necessary.

### FEATURES

Logic power supply (V<sub>DD</sub>) : 3.3 V±10%/5.0 V±10%

Fluorescent display tube drive power supply (V<sub>DISP</sub>) : 3.3 V±10%/5.0 V±10%

Fluorescent display tube drive power supply (V<sub>FL</sub>) :-20 to -60 V

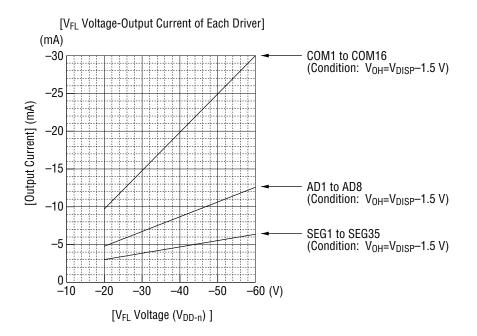

VFD driver output current

(VFD driver output can directly be connected to the fluorescent display tube. No pull-down resistor is required.)

| 10010101 10 100                   | [uncu.)               |              |                                                                                              |                                   |  |

|-----------------------------------|-----------------------|--------------|----------------------------------------------------------------------------------------------|-----------------------------------|--|

| - Segment dr                      | iver (SEG1 to SEG35   | ) : -5 1     | mA                                                                                           | $(V_{FL}=-60V)$                   |  |

| - Segment dr                      | iver (AD1 to AD8)     | :-10         | mA                                                                                           | $(V_{FL}=-60V)$                   |  |

| - Grid driver                     | (COM1 to COM16)       | : -30        | mA                                                                                           | $(V_{FL} = -60V)$                 |  |

| General outp                      | ut port output curre  | nt           |                                                                                              |                                   |  |

| - Output driv                     |                       |              | mA (V <sub>DD</sub> =                                                                        | =3.3V±10%)                        |  |

| *                                 |                       | ±2           | mA (V <sub>DD</sub> =                                                                        | =5.0V±10%)                        |  |

| • Content of di                   | splay                 |              | 22                                                                                           |                                   |  |

|                                   | 5×7 dots, 224 types   | (cha         | racter data                                                                                  | h)                                |  |

|                                   | 5×7 dots, 32 types    |              |                                                                                              |                                   |  |

|                                   | 16 (display digit) >  |              |                                                                                              |                                   |  |

|                                   |                       |              |                                                                                              | aracter data display)             |  |

| - General out                     | •                     | 4 bits (stat |                                                                                              | 1 7                               |  |

| • Display contr                   |                       |              |                                                                                              |                                   |  |

| - Display dig                     |                       | : 1 to       | 0 16 digits                                                                                  |                                   |  |

|                                   | y (contrast adjustme  |              | 0                                                                                            |                                   |  |

| × ,                               | k position specificat |              | 8                                                                                            |                                   |  |

| × ,                               | ft (left and right)   |              | : Can be set only for SEG output                                                             |                                   |  |

| - All lights O                    | e                     |              |                                                                                              |                                   |  |

| 6                                 |                       |              | : DA, $\overline{CS}$ , $\overline{CP}$ , and BLINK (5 interfaces when $\overline{RESET}$ is |                                   |  |

|                                   |                       | add          |                                                                                              |                                   |  |

| • 1 byte instru<br>specification) |                       | cluding da   | ata write f                                                                                  | to RAM and display blink position |  |

| <b>^</b>                          | rcuit included (exter | mal C and I  | <b>२</b> )                                                                                   |                                   |  |

| Package:                          | can menurea (catel    |              | ••/                                                                                          |                                   |  |

| i ucinage.                        |                       |              |                                                                                              |                                   |  |

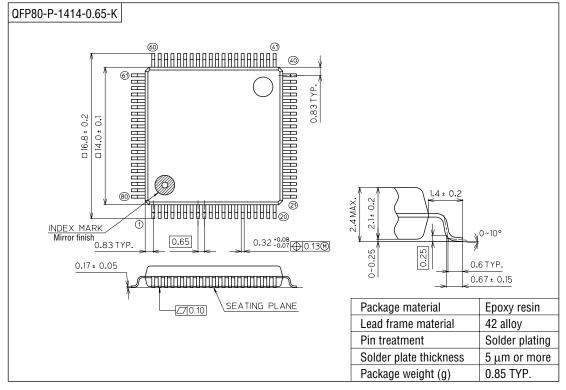

80-pin plastic QFP (QFP80-P-1414-0.65-K)

(Product name: MSM9200-xxGS-K) xx indicated the code number.

# **BLOCK DIAGRAM**

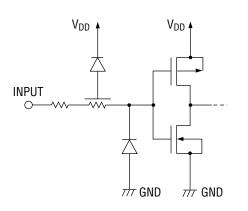

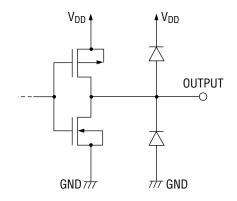

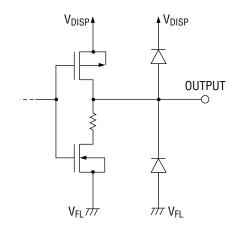

# INPUT AND OUTPUT CONFIGURATION

Schematic Diagrams of Logic Portion Input and Output Circuits

Input Pin

### Output Pin

Schematic Diagram of Driver Output Circuit

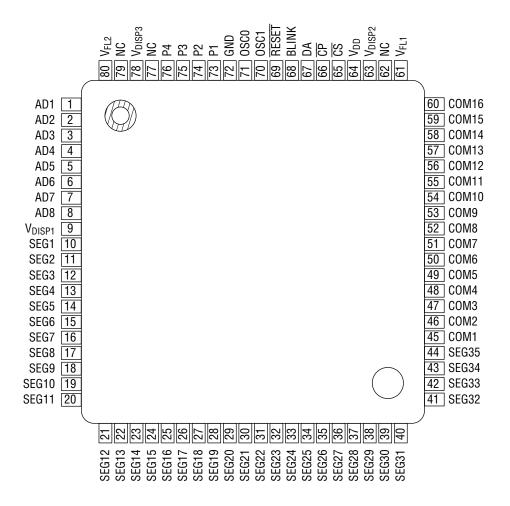

# **PIN CONFIGURATION (TOP VIEW)**

NC: No connection

80-Pin Plastic QFP

# **PIN DESCRIPTION**

| Pin       | Symbol               | Туре    | Connects to: | Description                                                                              |

|-----------|----------------------|---------|--------------|------------------------------------------------------------------------------------------|

|           |                      |         | Fluorescent  | Fluorescent display tube anode electrode drive output.                                   |

| 10 to 44  | SEG1-35              | 0       | tube grid    | Directly connected to fluorescent display tube and a pull-down                           |

|           |                      |         | electrode    | resistor is not necessary. I <sub>0H</sub> >–5 mA                                        |

|           |                      |         | Fluorescent  | Fluorescent display tube grid electrode drive output.                                    |

| 45 to 60  | COM1-16              | 0       | tube grid    | Directly connected to fluorescent display tube and a pull-down                           |

|           |                      |         | electrode    | resistor is not necessary. I <sub>OH</sub> >-30 mA                                       |

|           |                      |         | Fluorescent  | Fluorescent display tube grid electrode drive output.                                    |

| 1 to 8    | AD1-8                | 0       | tube grid    | Directly connected to fluorescent display tube and a pull-down                           |

|           |                      |         | electrode    | resistor is not necessary. I <sub>OH</sub> >-10 mA                                       |

|           |                      |         | LED drive    | General port output.                                                                     |

| 73 to 76  | P1-4                 | 0       | control      | Output of these pins in static mode, so control for LED driving is                       |

|           |                      |         | terminals    | performed through these pins.                                                            |

| 64        | V <sub>DD</sub>      | —       | Power        | V <sub>DD</sub> -GND are power supplies for internal logic.                              |

| 9, 63, 78 | V <sub>DISP1-3</sub> |         | supply       | $V_{\text{DISP}}\text{-}V_{\text{FL}}$ are power supplies for driving fluorescent tubes. |

| 72        | GND                  | _       |              | Use the same power supply for $V_{\text{DD}}$ and $V_{\text{DISP}}.$                     |

| 61, 80    | V <sub>FL1-2</sub>   | _       |              | Apply $V_{FL}$ after $V_{DD}$ and $V_{DISP}$ are applied.                                |

| 67        | DA                   |         | Micro-       | Serial data input (positive logic).                                                      |

| 07        | DA                   |         | controller   | Input from LSB.                                                                          |

| 66        | CP                   |         | Micro-       | Shift clock input.                                                                       |

| 00        | 01                   |         | controller   | Serial data is shifted on the rising edge of $\overline{CP}$ .                           |

| 65        | CS                   | 1       | Micro-       | Chip select input.                                                                       |

| 00        | 00                   |         | controller   | "H" disables serial data transfer.                                                       |

|           |                      |         |              | Display blink frequency input (square wave).                                             |

|           |                      |         |              | Only the position specified by the display blink position set command                    |

|           |                      |         | Micro-       | is validated.                                                                            |

| 68        | BLINK                | BLINK I |              | The time of "High" (light ON) and "Low" (light OFF) level of the signal                  |

|           |                      |         | controller   | frequency to be input to BLINK is the blink time.                                        |

|           |                      |         |              | Fix BLINK pin to the $V_{\text{DD}}$ or GND pin when the display blink control           |

|           |                      |         |              | is not used.                                                                             |

| Pin | Symbol | Туре | Connects to:                                                  | Description                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------|------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 69  | RESET  | 1    | Micro-<br>controller<br>or<br>C <sub>2</sub> , R <sub>2</sub> | Reset input (pull-up resistor included)."Low" initializes all the functions.Initial status is as follows.• Address of each RAM• Data of each RAM• Display digit• Display digit• Content is undefined• Display digit• Contrast adjusment• O/16• Display blink• All lights ON or OFF• All outputs• All outputs• Concected externally)• Connected externally)• See Application Circuit. |

| 71  | OSCO   | I    |                                                               | External RC pin for RC oscillation.<br>Connect R and C externally. The RC time constant depends on the<br>V <sub>DD</sub> voltage used. Set the target oscillation frequency to 2 MHz.                                                                                                                                                                                               |

| 70  | OSC1   | 0    | - C <sub>1</sub> , R <sub>1</sub>                             | $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                             |

| Parameter           | Symbol            | Condition  | Rating                        | Unit |

|---------------------|-------------------|------------|-------------------------------|------|

| Supply Voltage 1    | V <sub>DD</sub>   | (*1)       | -0.3 to 6.5                   | V    |

| Supply Voltage 1    | V <sub>DISP</sub> | (*1)       | -0.3 to 6.5                   | V    |

| Supply Voltage 2    | V <sub>FL</sub>   | —          | -80 to V <sub>DISP</sub> +0.3 | V    |

| Input Voltage       | V <sub>IN</sub>   | —          | -80 to V <sub>DD</sub> +0.3   | V    |

| Power Dissipation   | PD                | Ta≤25°C    | 565                           | mW   |

| Storage Temperature | T <sub>STG</sub>  | —          | –55 to 150                    | °C   |

|                     | I <sub>01</sub>   | COM1-COM16 | -40 to 0.0                    |      |

| Output Current      | I <sub>02</sub>   | AD1-AD8    | -20 to 0.0                    | m 1  |

| Output Current      | I <sub>03</sub>   | SEG1-SEG35 | -10 to 0.0                    | — mA |

|                     | I <sub>04</sub>   | P1-P4      | -4.0 to 4.0                   |      |

# **ABSOLUTE MAXIMUM RATINGS**

\*1 Use the same power supply for  $V_{DD}$  and  $V_{DISP}$ .

# **RECOMMENDED OPERATING CONDITIONS-1**

| When the power supply voltage is 5V (typ). | When the | power supp | oly voltage | e is 5V (typ | ). |

|--------------------------------------------|----------|------------|-------------|--------------|----|

|--------------------------------------------|----------|------------|-------------|--------------|----|

| Parameter                | Symbol                               | Condition                                               | Min.               | Тур. | Max.               | Unit |

|--------------------------|--------------------------------------|---------------------------------------------------------|--------------------|------|--------------------|------|

| Supply Voltage 1         | V <sub>DD</sub>                      | _                                                       | 4.5                | 5.0  | 5.5                | V    |

| Supply Voltage 2         | V <sub>DISP</sub><br>V <sub>FL</sub> |                                                         | -60                |      | -20                | V    |

| High Level Input Voltage | V <sub>IH</sub>                      | All input pins excluding OSCO pin                       | 0.7V <sub>DD</sub> | _    |                    | V    |

| Low Level Input Voltage  | V <sub>IL</sub>                      | All input pins excluding OSCO pin                       |                    | _    | 0.3V <sub>DD</sub> | V    |

| CP Frequency             | f <sub>C</sub>                       | —                                                       | _                  | _    | 1.0                | MHz  |

| Oscillation Frequency    | fosc                                 | R <sub>1</sub> =3.3kΩ, C <sub>1</sub> =47pF             | 1.5                | 2.0  | 2.5                | MHz  |

| Frame Frequency          | f <sub>FR</sub>                      | DIGIT=1–16, R <sub>1</sub> =3.3kΩ, C <sub>1</sub> =47pF | 183                | 244  | 305                | Hz   |

| RESET Input Time         | t <sub>RSON</sub>                    | R <sub>2</sub> =1.0kΩ, C <sub>2</sub> =0.1PF            | 0                  | _    | 200                | μs   |

| Operating Temperature    | T <sub>OP</sub>                      | —                                                       | -40                |      | 85                 | °C   |

# **RECOMMENDED OPERATING CONDITIONS-2**

| Parameter                | Symbol            | Condition                                               | Min.               | Тур. | Max.               | Unit |

|--------------------------|-------------------|---------------------------------------------------------|--------------------|------|--------------------|------|

| Supply Voltage 1         | V <sub>DD</sub>   |                                                         | 3.0                | 3.3  | 3.6                | V    |

| Supply Voltage 1         | V <sub>DISP</sub> | _                                                       | 3.0                | 3.3  | 3.0                | v    |

| Supply Voltage 2         | V <sub>FL</sub>   | —                                                       | -60                |      | -20                | V    |

| High Level Input Voltage | VIH               | All input pins excluding OSCO pin                       | 0.8V <sub>DD</sub> |      |                    | V    |

| Low Level Input Voltage  | VIL               | All input pins excluding OSCO pin                       | _                  |      | 0.2V <sub>DD</sub> | V    |

| CP Frequency             | f <sub>C</sub>    | —                                                       | _                  |      | 1.0                | MHz  |

| Oscillation Frequency    | f <sub>OSC</sub>  | R <sub>1</sub> =3.3kΩ, C <sub>1</sub> =39pF             | 1.5                | 2.0  | 2.5                | MHz  |

| Frame Frequency          | f <sub>FR</sub>   | DIGIT=1-16, R <sub>1</sub> =3.3kΩ, C <sub>1</sub> =39pF | 183                | 244  | 305                | Hz   |

| RESET Input Time         | t <sub>RSON</sub> | R <sub>2</sub> =1.0kΩ, C <sub>2</sub> =0.1µF            | 0                  |      | 200                | μs   |

| Operating Temperature    | T <sub>OP</sub>   | —                                                       | -40                | _    | 85                 | °C   |

When the power supply voltage is 3.3V (typ).

# **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics-1**

( $V_{DD}=V_{DISP}=5.0V\pm10\%$ ,  $V_{FL}=-60V$ , Ta=-40 to +85°C, unless otherwise specified)

| Parameter                | Symbol           | Applied pin                                                 |                            | Condition                        | Min.                   | Max.                 | Unit |

|--------------------------|------------------|-------------------------------------------------------------|----------------------------|----------------------------------|------------------------|----------------------|------|

| High Level Input Voltage | V <sub>IH</sub>  | $\overline{\text{CS}}, \overline{\text{CP}}, \text{BLINK},$ |                            |                                  | 0.7V <sub>DD</sub>     |                      | V    |

|                          | • IN             | DA, RESET                                                   |                            |                                  | 0.1 100                |                      |      |

| Low Level Input Voltage  | V <sub>IL</sub>  | CS, CP, BLINK,                                              |                            | _                                | _                      | 0.3V <sub>DD</sub>   | V    |

|                          | ۷IL              | DA, RESET                                                   |                            |                                  |                        | 0.0100               | v    |

| High Level Input Current | I                | CS, CP, BLINK,                                              |                            | V <sub>IH</sub> =V <sub>DD</sub> | -1.0                   | 1.0                  | μA   |

|                          | I <sub>IH</sub>  | DA, RESET                                                   |                            | VIH-VDD                          | -1.0                   | 1.0                  | μΛ   |

| Low Level Input Current  | I.,              | $\overline{\text{CS}}, \overline{\text{CP}}, \text{BLINK},$ |                            | V <sub>IL</sub> =0.0V            | -1.0                   | 1.0                  |      |

| Low Level input Guilent  | Ι <sub>ΙL</sub>  | DA, RESET                                                   |                            | VIL=0.0V                         | -1.0                   | 1.0                  | μA   |

|                          | V <sub>OH1</sub> | COM1-16                                                     | I <sub>0H1</sub> =–30mA    |                                  | V <sub>DISP</sub> -1.5 | —                    | V    |

| High Level Output        | V <sub>0H2</sub> | AD1-8                                                       |                            | I <sub>0H2</sub> =–10mA          | V <sub>DISP</sub> -1.5 | —                    | V    |

| Voltage                  | V <sub>OH3</sub> | SEG1-35                                                     | I <sub>OH3</sub> =–5mA     |                                  | V <sub>DISP</sub> -1.5 | —                    | V    |

|                          | V <sub>OH4</sub> | P1-4                                                        |                            | I <sub>OH4</sub> =-2mA           | V <sub>DD</sub> -1.0   | —                    | V    |

|                          |                  | COM1-16                                                     |                            |                                  |                        |                      |      |

| Low Level Output         | V <sub>OL1</sub> | AD1-8                                                       |                            | —                                | —                      | V <sub>FL</sub> +1.0 | V    |

| Voltage                  |                  | SEG1-35                                                     |                            |                                  |                        |                      |      |

|                          | V <sub>0L2</sub> | P1-4                                                        |                            | I <sub>0L1</sub> =2mA            | —                      | 1.0                  | V    |

|                          |                  |                                                             |                            | Duty=15/16                       |                        |                      |      |

|                          | I <sub>DD1</sub> |                                                             | faaa                       | Digit=1-16                       | —                      | 4                    | mA   |

| Ourset Consumption       |                  | W W                                                         | f <sub>OSC</sub> =<br>2MHz | All output lights ON             |                        |                      |      |

| Current Consumption      |                  | V <sub>DD</sub> , V <sub>DISP</sub>                         |                            | Duty=8/16                        |                        |                      |      |

|                          | I <sub>DD2</sub> |                                                             | no load                    | Digit=1–9                        | _                      | 3                    | mA   |

|                          |                  |                                                             |                            | All output lights OFF            |                        |                      |      |

#### **DC Characteristics-2**

( $V_{DD}=V_{DISP}=3.3V\pm10\%$ ,  $V_{FL}=-60V$ , Ta=-40 to +85°C, unless otherwise specified)

| Parameter                   | Symbol           | Applied pin                           |                            | Condition                                        | Min.                   | Max.                 | Unit |

|-----------------------------|------------------|---------------------------------------|----------------------------|--------------------------------------------------|------------------------|----------------------|------|

| High Level Input Voltage    | V <sub>IH</sub>  | CS, CP, BLINK,<br>DA, RESET           |                            | _                                                | 0.8V <sub>DD</sub>     |                      | V    |

| Low Level Input Voltage     | V <sub>IL</sub>  | CS, CP, BLINK,<br>DA, RESET           |                            | _                                                |                        | 0.2V <sub>DD</sub>   | V    |

| High Level Input Current    | I <sub>IH</sub>  | CS, CP, BLINK,<br>DA, RESET           |                            | V <sub>IH</sub> =V <sub>DD</sub>                 | -1.0                   | 1.0                  | μA   |

| Low Level Input Current     | I <sub>IL</sub>  | CS, CP, BLINK,<br>DA, RESET           |                            | V <sub>IL</sub> =0.0V                            | -1.0                   | 1.0                  | μA   |

|                             | V <sub>OH1</sub> | COM1-16                               |                            | <sub>0H1</sub> =30mA                             | V <sub>DISP</sub> -1.5 |                      | V    |

| High Level Output           | V <sub>OH2</sub> | AD1-8                                 |                            | <sub>0H2</sub> =–10mA                            | V <sub>DISP</sub> -1.5 | _                    | V    |

| Voltage                     | V <sub>OH3</sub> | SEG1-35                               | I <sub>0H3</sub> =–5mA     |                                                  | V <sub>DISP</sub> -1.5 | —                    | V    |

|                             | V <sub>0H4</sub> | P1-4                                  |                            | I <sub>OH4</sub> =–1mA                           | V <sub>DD</sub> -1.0   | —                    | V    |

| Low Level Output<br>Voltage | V <sub>0L1</sub> | COM1-16<br>AD1-8<br>SEG1-35           |                            | _                                                | _                      | V <sub>FL</sub> +1.0 | V    |

|                             | V <sub>OL2</sub> | P1-4                                  |                            | I <sub>0L1</sub> =1mA                            | —                      | 1.0                  | V    |

| Current Concurrentian       | I <sub>DD1</sub> | N N                                   | f <sub>OSC</sub> =<br>2MHz | Duty=15/16<br>Digit=1–16<br>All output lights ON |                        | 3                    | mA   |

| Current Consumption         | I <sub>DD2</sub> | - V <sub>DD</sub> , V <sub>DISP</sub> | no load                    | Duty=8/16<br>Digit=1–9<br>All output lights OFF  |                        | 2                    | mA   |

#### **AC Characteristics-1**

(V\_DD, V\_DISP=5.0V $\pm$ 10%, V<sub>FL</sub>=-60V, Ta=-40 to +85°C, unless otherwise specified)

| Parameter                 | Symbol             | Cond                                        | dition                          | Min. | Max. | Unit |

|---------------------------|--------------------|---------------------------------------------|---------------------------------|------|------|------|

| CP Frequncy               | f <sub>C</sub>     | -                                           | _                               |      | 1.0  | MHz  |

| CP Pulse Width            | t <sub>CW</sub>    | -                                           | _                               | 300  |      | ns   |

| DA Setup Time             | t <sub>DS</sub>    | -                                           | _                               | 300  | —    | ns   |

| DA Hold Time              | t <sub>DH</sub>    | -                                           | _                               | 300  | —    | ns   |

| CS Setup Time             | t <sub>CSS</sub>   | -                                           | _                               | 300  |      | ns   |

| CS Hold Time              | t <sub>CSH</sub>   | R <sub>1</sub> =3.3kΩ, C <sub>1</sub> =47PF |                                 | 16   |      | μs   |

| CS Wait Time              | t <sub>CSW</sub>   |                                             |                                 | 300  |      | ns   |

| Data Processing Time      | t <sub>DOFF</sub>  | R <sub>1</sub> =3.3kΩ, C <sub>1</sub> =47PF |                                 | 8    |      | μs   |

| <b>RESET</b> Pulse Width  | t <sub>RSON</sub>  | When <b>RESET</b> sign                      | al is input externally          | 300  | —    | ns   |

| Waite DA Time             | t <sub>RSOFF</sub> | -                                           | _                               | 300  |      | μs   |

| All Output Clow Data      | t <sub>R</sub>     | 0 100 - 5                                   | t <sub>R</sub> =20% to 80%      |      | 4.0  | μs   |

| All Output Slow Rate      | t <sub>F</sub>     | C <sub>I</sub> =100pF                       | t <sub>F</sub> =80% to 20%      | —    | 4.0  | μs   |

| V <sub>DD</sub> Rise Time | t <sub>PRZ</sub>   | When mounted in the unit                    |                                 | _    | 100  | μs   |

| V <sub>DD</sub> Off Time  | t <sub>POF</sub>   | When mounted in                             | the unit, V <sub>DD</sub> =0.0V | 5.0  |      | ms   |

#### AC Characteristics-2

(V\_DD, V\_DISP=3.3V $\pm$ 10%, V<sub>FL</sub>=-60V, Ta=-40 to +85°C, unless otherwise specified)

| Parameter                 | Symbol             | Cond                                            | lition                     | Min. | Max. | Unit |

|---------------------------|--------------------|-------------------------------------------------|----------------------------|------|------|------|

| CP Frequncy               | f <sub>C</sub>     | -                                               | _                          | _    | 1.0  | MHz  |

| CP Pulse Width            | t <sub>CW</sub>    | -                                               | _                          | 300  | —    | ns   |

| DA Setup Time             | t <sub>DS</sub>    | -                                               | _                          | 300  | —    | ns   |

| DA Hold Time              | t <sub>DH</sub>    | -                                               | _                          | 300  | —    | ns   |

| CS Setup Time             | t <sub>CSS</sub>   | _                                               |                            | 300  | —    | ns   |

| CS Hold Time              | t <sub>CSH</sub>   | $R_1=3.3k\Omega$ , $C_1=39PF$                   |                            | 16   | —    | μs   |

| CS Wait Time              | t <sub>CSW</sub>   |                                                 |                            | 300  | —    | ns   |

| Data Processing Time      | t <sub>DOFF</sub>  | R <sub>1</sub> =3.3kΩ, C <sub>1</sub> =39PF     |                            | 8    | —    | μs   |

| <b>RESET</b> Pulse Width  | t <sub>WRES</sub>  | When <b>RESET</b> signal is input externally    |                            | 300  |      | ns   |

| DA Wait Time              | t <sub>RSOFF</sub> | -                                               | _                          | 300  |      | μs   |

| All Output Claw Data      | t <sub>R</sub>     | 0 100pF                                         | t <sub>R</sub> =20% to 80% |      | 4.0  | μs   |

| All Output Slew Rate      | t <sub>F</sub>     | C <sub>I</sub> =100pF                           | t <sub>F</sub> =80% to 20% | —    | 4.0  | μs   |

| V <sub>DD</sub> Rise Time | t <sub>PRZ</sub>   | When mounted in the unit                        |                            | _    | 100  | μs   |

| V <sub>DD</sub> Off Time  | t <sub>POF</sub>   | When mounted in the unit, V <sub>DD</sub> =0.0V |                            | 5.0  | _    | ms   |

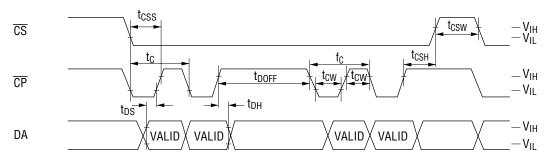

### TIMING DIAGRAM

#### • Data Timing

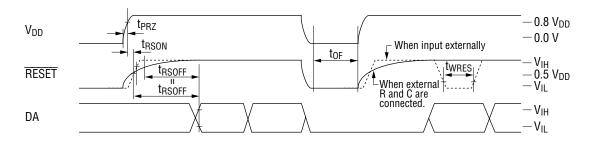

#### • Reset Timing

#### • Output Timing

| Symbol          | V <sub>DD</sub> =3.3V±10% | V <sub>DD</sub> =5.0V±10% |

|-----------------|---------------------------|---------------------------|

| V <sub>IH</sub> | 0.8 V <sub>DD</sub>       | 0.7 V <sub>DD</sub>       |

| VIL             | 0.2 V <sub>DD</sub>       | 0.3 V <sub>DD</sub>       |

# FUNCTIONAL DESCRIPTION

#### **Command List**

|            | Command                  | LSB |     |      | 1st | byte |    |    | MSB | LSB                                |                                                                      |                                                                                     | 2nd | byte    |       |         | MSB    |          |

|------------|--------------------------|-----|-----|------|-----|------|----|----|-----|------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----|---------|-------|---------|--------|----------|

|            | Commanu                  | B0  | B1  | B2   | B3  | B4   | B5 | B6 | B7  | B0                                 | B1                                                                   | B2                                                                                  | B3  | B4      | B5    | B6      | B7     |          |

| 1          | DCRAM data write 1       | X0  | X1  | X2   | Х3  | 1    | 0  | 0  | 0   | CO                                 | C1                                                                   | C1 C2 C3 C4 C5 C6 C7                                                                |     |         |       |         |        |          |

| 2          | DCRAM data write 2       | X0  | X1  | X2   | Х3  | 0    | 1  | 0  | 0   | C0                                 | C1         C2         C3         C4         C5         C6         C7 |                                                                                     |     |         |       |         |        |          |

| 3          | DCRAM data write 3       | X0  | X1  | X2   | Х3  | 1    | 1  | 0  | 0   | C0                                 | C1                                                                   | C2                                                                                  | C3  | C4      | C5    | C6      | C7     |          |

| 4          | DCRAM data write 4       | X0  | X1  | X2   | Х3  | 0    | 0  | 1  | 0   | C0                                 | C1                                                                   | C2                                                                                  | C3  | C4      | C5    | C6      | C7     |          |

|            |                          |     |     |      |     |      |    |    |     | C0                                 | C5                                                                   | C10                                                                                 | C15 | C20     | C25   | C30     | *      | 2nd byte |

|            |                          |     |     |      |     |      |    |    |     | C1                                 | C6                                                                   | C11                                                                                 | C16 | C21     | C26   | C31     | *      | 3rd byte |

| 5          | CGRAM data write 1       | X0  | X1  | X2   | Х3  | 1    | 0  | 1  | 0   | C2                                 | C7                                                                   | C12                                                                                 | C17 | C22     | C27   | C32     | *      | 4th byte |

|            |                          |     |     |      |     |      |    |    |     | C3                                 | C8                                                                   | C13                                                                                 | C18 | C23     | C28   | C33     | *      | 5th byte |

|            |                          |     |     |      |     |      |    |    |     | C4                                 | C9                                                                   | C14                                                                                 | C19 | C24     | C29   | C34     | *      | 6th byte |

|            |                          |     |     |      |     |      |    |    |     | C0                                 | C5                                                                   | C10                                                                                 | C15 | C20     | C25   | C30     | *      | 2nd byte |

|            |                          |     |     |      |     |      |    |    |     | C1                                 | C6                                                                   | C11                                                                                 | C16 | C21     | C26   | C31     | *      | 3rd byte |

| 6          | CGRAM data write 2       | X0  | X1  | X2   | X3  | 0    | 1  | 1  | 0   | C2                                 | C7                                                                   | C12 C17                                                                             |     | C22     | C27   | C32     | *      | 4th byte |

|            |                          |     |     |      |     |      |    |    |     | C3                                 | C8                                                                   | C13                                                                                 | C18 | C23     | C28   | C33     | *      | 5th byte |

|            |                          |     |     |      |     |      |    |    |     | C4                                 | C9                                                                   | C14                                                                                 | C19 | C24     | C29   | C34     | *      | 6th byte |

| 7          | ADRAM data write         | X0  | X1  | X2   | Х3  | 1    | 1  | 1  | 0   | CO                                 | C1                                                                   | C2                                                                                  | C3  | C4      | C5    | C6      | C7     |          |

| •          | Display blink position   | ~~~ | 4.5 | *    | *   | •    | •  | _  |     | G1                                 | G2                                                                   | G3                                                                                  | G4  | G5      | G6    | G7      | G8     | 2nd byte |

| 8          | set                      | SG  | AD  |      | ^   | 0    | 0  | 0  | 1   | G9                                 | G10                                                                  | G11                                                                                 | G12 | G13     | G14   | G15     | G16    | 3rd byte |

| 9          | DCRAM address shift      | S   | *   | *    | *   | 1    | 0  | 0  | 1   | *                                  |                                                                      |                                                                                     |     |         |       |         |        | -        |

| А          | DCRAM address reset      | *   | *   | *    | *   | 0    | 1  | 0  | 1   | Xn                                 |                                                                      | on't c                                                                              |     | ificati | on fo | r aa ah | DAM    | 1        |

| В          | General output port set  | P1  | P2  | P3   | P4  | 1    | 1  | 0  | 1   | Cn                                 |                                                                      | : Address specification for each RAM<br>: Character code specification for each RAM |     |         |       |         |        |          |

| С          | Display duty set         | D0  | D1  | D2   | D3  | 0    | 0  | 1  | 1   | SG                                 | -                                                                    |                                                                                     |     |         |       |         |        |          |

| D          | Number of digits set     | K0  | K1  | K2   | K3  | 1    | 0  | 1  | 1   | AD : AD display area specification |                                                                      |                                                                                     |     |         |       |         |        |          |

| Е          | All lights ON/OFF        | L   | Н   | *    | *   | 0    | 1  | 1  | 1   | Gn                                 |                                                                      | isplay                                                                              |     | •       |       |         |        |          |

|            | Test mode                |     |     |      |     |      |    |    |     | S                                  |                                                                      | eft and                                                                             | •   | •       |       | •       |        |          |

| A / I= = = | n data is written to RAM |     |     | 0004 |     |      |    |    |     | Pn<br>Dn                           |                                                                      | eneral<br>isplay                                                                    | •   | •       |       | •       | CIIICa | 11011    |

When data is written to RAM (DCRAM, CGRAM, ADRAM) continuously, addresses are internally incremented automatically.

Therefore it is not necessary to specify the 1st byte to write RAM data for the 2nd and later bytes.

Note: The test mode is used for inspection before shipment. It is not a user function. Kn : Number of digits specification

H : All lights ON instruction

L : All lights OFF instruction

|                                                                                                                                           | C0<br>AD1<br>C4<br>AD5          | C1<br>AD2<br>C5<br>AD6          | C2<br>AD3<br>C6<br>AD7          | C3<br>AD4<br>C7<br>AD8          | -                                | ——— Area for the AD<br>be output | RAM data to                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|----------------------------------|----------------------------------|----------------------------------------------------|

|                                                                                                                                           | C0<br>SEG1<br>C5<br>SEG6<br>C10 | C1<br>SEG2<br>C6<br>SEG7<br>C11 | C2<br>SEG3<br>C7<br>SEG8<br>C12 | C3<br>SEG4<br>C8<br>SEG9<br>C13 | C4<br>SEG5<br>C9<br>SEG10<br>C14 |                                  |                                                    |

|                                                                                                                                           | SEG11<br>C15<br>SEG16<br>C20    | SEG12<br>C16<br>SEG17<br>C21    | SEG13<br>C17<br>SEG18<br>C22    | SEG14<br>C18<br>SEG19<br>C23    | SEG15<br>C19<br>SEG20<br>C24     |                                  |                                                    |

|                                                                                                                                           | SEG21<br>C25<br>SEG26<br>C30    | SEG22<br>C26<br>SEG27<br>C31    | SEG23<br>C27<br>SEG28<br>C32    | SEG24<br>C28<br>SEG29<br>C33    | SEG25<br>C29<br>SEG30<br>C34     |                                  |                                                    |

| CGRAM written data. Corresponds to 2nd byte<br>CGRAM written data. Corresponds to 3rd byte<br>CGRAM written data. Corresponds to 4th byte | <u>  SEG31</u>                  | SEG32                           | SEG33                           | SEG34                           | SEG35                            |                                  | Corresponds to 6th byte<br>Corresponds to 5th byte |

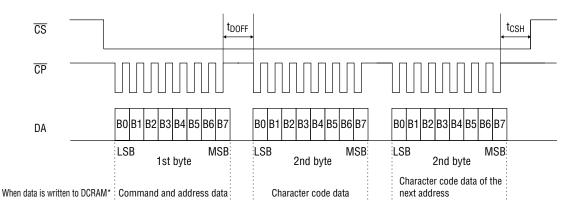

#### Data Transfer System and Command Write System

Display control command and data are written by an 8-bit serial transfer. Write timing is shown in the figure below.

Setting the  $\overline{\text{CS}}$  pin to "Low" level enables a data transfer.

Data is 8 bits and is sequentially input into the DA pin from LSB (LSB first). As shown in the figure below, data is read by the shift register at the rising edge of the shift clock, which is input into the  $\overline{CP}$  pin. If 8-bit data is input, internal load signals are automatically generated and data is written to each register and RAM.

Therefore it is not necessary to input load signals from the outside.

Setting the  $\overline{CS}$  pin to "High" disables data transfer. Data input from the point when the  $\overline{CS}$  pin changes from "High" to "Low" is recognized in 8-bit units.

\* When data is written to RAM (DCRAM, ADRAM, CGRAM) continuously, addresses are internally incremented automatically.

Therefore it is not necessary to specify the 1st byte to write RAM data for the 2nd and later bytes.

#### **Reset Function**

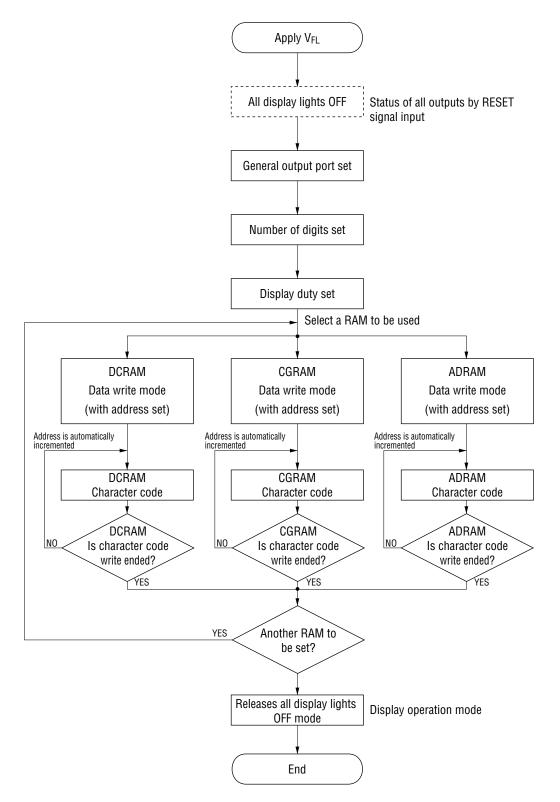

Reset is executed when the **RESET** pin is set to "L", (when turning power on, for example,) and initializes all functions.

Initial status is as follows.

- Address of each RAM ..... address "00"H

- Data of each RAM ..... All contents are undefined

- Display blink ...... Blinking is disabled for all outputs

- General output port ...... All general output ports go "Low"

- Display digit ..... 16 digits

- Contrast adjustment ..... 0/16

- All display lights ON or OFF ..... OFF mode

- Segment output ...... All segment outputs go "Low"

- AD output ...... All AD outputs go "Low"

Reset again according to "Initial Setting Flowchart" after reset.

#### **Description of Commands and Functions**

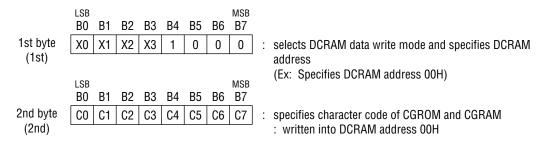

- 1. DCRAM data write 1 (Specifies the address (00H to 0FH) of DCRAM and writes the character code of CGROM and CGRAM.)

- 2. DCRAM data write 2 (Specifies the address (10H to 1FH) of DCRAM and writes the character code of CGROM and CGRAM.)

- 3. DCRAM data write 3 (Specifies the address (20H to 2FH) of DCRAM and writes the character code of CGROM and CGRAM.)

- 4. DCRAM data write 4 (Specifies the address (30H to 3FH) of DCRAM and writes the character code of CGROM and CGRAM.)

DCRAM (Data Control RAM) has a 6-bit address to store character code of CGROM and CGRAM. (4 bits can be set by the user and the 2 bits on the MSB side are automatically set.) The character code specified by DCRAM is converted to a 5×7 dot matrix character pattern via CGROM or CGRAM.

The capacity is  $64 \times 8$  bits, which can store 64 characters.

Note: The addresses 00H to 3FH of DCRAM are automatically incremented.

[Command format]

To specify the character code of CGROM and CGRAM continuously to the next address, specify only character code as follows.

The addresses of DCRAM are automatically incremented. Specification of an address is unnecessary.

| 2nd byte<br>(3rd)                        | LSB         MSB           B0         B1         B2         B3         B4         B5         B6         B7           C0         C1         C2         C3         C4         C5         C6         C7           LSB         B0         B1         B2         B3         B4         B5         B6         B7                                                                                                                                                                           | : specifies character code of CGROM and CGRAM<br>: written into DCRAM address 01H                                                                                                                    |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2nd byte<br>(4th)                        | C0         C1         C2         C3         C4         C5         C6         C7                                                                                                                                                                                                                                                                                                                                                                                                     | : specifies character code of CGROM and CGRAM<br>: written into DCRAM address 02H                                                                                                                    |

| 2nd byte<br>(17th)<br>2nd byte<br>(18th) | LSB<br>B0 B1 B2 B3 B4 B5 B6 B7<br>C0 C1 C2 C3 C4 C5 C6 C7<br>LSB<br>B0 B1 B2 B3 B4 B5 B6 B7<br>C0 C1 C2 C3 C4 C5 C6 C7<br>C0 C1 C2 C3 C4 C5 C6 C7                                                                                                                                                                                                                                                                                                                                   | <ul> <li>specifies character code of CGROM and CGRAM</li> <li>written into DCRAM address 0FH</li> <li>specifies character code of CGROM and CGRAM</li> <li>written into DCRAM address 10H</li> </ul> |

| 2nd byte<br>(65th)<br>2nd byte<br>(66th) | LSB       B2       B3       B4       B5       B6       B7         C0       C1       C2       C3       C4       C5       C6       C7         LSB       B0       B1       B2       B3       B4       B5       B6       B7         LSB       B0       B1       B2       C3       C4       C5       C6       C7         LSB       C0       C1       C2       C3       C4       C5       C6       C7         LSB       C0       C1       C2       C3       C4       C5       C6       C7 | <ul> <li>specifies character code of CGROM and CGRAM</li> <li>written into DCRAM address 3FH</li> <li>specifies character code of CGROM and CGRAM</li> <li>DCRAM address 00H is rewritten</li> </ul> |

X0 (LSB) to X3 (MSB): DCRAM addresses (4 bits: 16 characters) Note: A total of 64 characters for the four specifications C0 (LSB) to C7 (MSB): Character code of CGROM and CGRAM (8 bits: 256 character)

[COM positions and set DCRAM addresses]

The states when  $\overline{\text{RESET}}$  is input and DCRAM address reset commands are executed

| Command<br>No. | HEX            | к0 | К1 | К2        | КЗ | COM<br>position | Command<br>No. | HEX            | к0 | К1 | К2        | КЗ | COM<br>position |

|----------------|----------------|----|----|-----------|----|-----------------|----------------|----------------|----|----|-----------|----|-----------------|

|                | 00             | 0  | 0  | 0         | 0  | COM1            |                | 20             | 0  | 0  | 0         | 0  |                 |

|                | 01             | 1  | 0  | 0         | 0  | COM2            |                | 21             | 1  | 0  | 0         | 0  |                 |

| 1              | <br> <br> <br> |    |    | <br> <br> |    |                 | 3              | <br> <br> <br> |    |    | <br> <br> |    |                 |

|                | 0E             | 1  | 1  | 1         | 1  | COM15           |                | 2E             | 1  | 1  | 1         | 1  |                 |

|                | 0F             | 1  | 1  | 1         | 1  | COM16           |                | 2F             | 1  | 1  | 1         | 1  |                 |

|                | 10             | 0  | 0  | 0         | 0  |                 |                | 30             | 0  | 0  | 0         | 0  |                 |

|                | 11             | 1  | 0  | 0         | 0  |                 |                | 31             | 1  | 0  | 0         | 0  |                 |

| 2              | 1              |    |    | <br> <br> |    |                 | 4              | <br> <br> <br> |    |    | 1         |    | 1               |

|                | 1E             | 0  | 1  | 1         | 1  |                 |                | 3E             | 0  | 1  | 1         | 1  |                 |

|                | 1F             | 1  | 1  | 1         | 1  |                 |                | 3F             | 1  | 1  | 1         | 1  |                 |

5. CGRAM data write 1

(Specifies the addresses 00H to 0FH of CGRAM and writes character pattern data.)

CGRAM data write 2 (Specifies the addresses 10H to 1FH of CGRAM and writes character pattern data.)

CGRAM (Character Generator RAM) has a 5-bit address to store 5×7 dot matrix character patterns. (4 bits can be set by the user and the 1 bit on the MSB is automatically set.) A character pattern stored in CGRAM can be displayed by specifying the character code (address) by DCRAM. The address of CGRAM is assigned to 00H to 1FH. (All the other addresses are the CGROM addresses.)

Capacity is (16×2)×35×8 bits, which can store 32 types of character patterns.

Note: The addresses 00H to 1FH of CGRAM are automatically incremented.

[Command format]

LSB MSB B0 B1 B2 B3 Β4 B5 B6 Β7 1st byte X0 X1 X2 X3 1 0 1 0 selects CGRAM data write mode and specifies (1st) CGRAM address. (Ex: specifies CGRAM address 00H) MSB LSB B0 B1 B2 B3 Β4 Β5 B6 B7 2nd byte \* C0 C5 C10 C15 C20 C25 C30 specifies 1st column data (2nd) : rewritten into CGRAM address 00H LSB MSB B5 B0 B1 B2 B3 Β4 B6 **B**7 3rd byte \* C1 C6 C11 C16 C21 C26 C31 specifies 2nd column data (3rd) : rewritten into CGRAM address 00H LSB MSB B2 B3 B0 B1 Β4 B5 B6 Β7 4th byte \* C7 C12 C17 C22 C27 C32 C2 specifies 3rd column data (4th) : rewritten into CGRAM address 00H LSB MSB B0 B1 B2 B3 Β4 B5 B6 **B**7 5th byte C3 C8 C13 C18 C23 C28 C33 \* specifies 4th column data (5th) : rewritten into CGRAM address 00H LSB MSB B0 B1 B2 B3 Β4 B5 B6 B7 \* 6th byte C9 C14 C19 C24 C29 C34 specifies 5th column data C4 (6th) : rewritten into CGRAM address 00H

To specify character pattern data continuously to the next address, specify only character pattern data as follows.

The addresses of CGRAM are automatically incremented. Specification of an address is therefore unnecessary.

The 2nd to 6th byte (character pattern data) are regarded as one data item, so 300 ns is sufficient for t<sub>DOFF</sub> time between bytes.

| 2nd byte<br>(7th)   | LSB<br>B0 B1 B2 B3 B4 B5 B6 B7<br>C0 C5 C10 C15 C20 C25 C30 * :                                                                                                                                                                                                                                                                                                                                   | specifies 1st column data<br>: rewritten into CGRAM address 01H |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 6th byte<br>(11th)  | LSB         MSB           B0         B1         B2         B3         B4         B5         B6         B7           C4         C9         C14         C19         C24         C29         C34         *         :           LSB         MSB         MSB         MSB         MSB         MSB         MSB           B0         B1         B2         B3         B4         B5         B6         B7 | specifies 5th column data<br>: rewritten into CGRAM address 01H |

| 2nd byte<br>(12th)  | C0         C5         C10         C15         C20         C25         C30         *         :                                                                                                                                                                                                                                                                                                     | specifies 1st column data<br>: rewritten into CGRAM address 02H |

| 6th byte<br>(16th)  | LSB<br>B0 B1 B2 B3 B4 B5 B6 B7<br>C4 C9 C14 C19 C24 C29 C34 * :                                                                                                                                                                                                                                                                                                                                   | specifies 5th column data<br>: rewritten into CGRAM address 02H |

| 2nd byte<br>(77th)  | LSB<br>B0 B1 B2 B3 B4 B5 B6 B7<br>C0 C5 C10 C15 C20 C25 C30 * :                                                                                                                                                                                                                                                                                                                                   | specifies 1st column data<br>: rewritten into CGRAM address 0FH |

| 6th byte<br>(81th)  | LSB<br>B0 B1 B2 B3 B4 B5 B6 B7<br>C4 C9 C14 C19 C24 C29 C34 * :<br>LSB<br>B0 B1 B2 B3 B4 B5 B6 B7                                                                                                                                                                                                                                                                                                 | specifies 5th column data<br>: rewritten into CGRAM address 0FH |

| 2nd byte<br>(82th)  | C0         C5         C10         C15         C20         C25         C30         *         :                                                                                                                                                                                                                                                                                                     | specifies 1st column data<br>: rewritten into CGRAM address 10H |

| 6th byte<br>(86th)  | LSB<br>B0 B1 B2 B3 B4 B5 B6 B7<br>C4 C9 C14 C19 C24 C29 C34 * :                                                                                                                                                                                                                                                                                                                                   | specifies 5th column data<br>: rewritten into CGRAM address 10H |

| 2nd byte<br>(157th) | B0         B1         B2         B3         B4         B5         B6         B7           C0         C5         C10         C15         C20         C25         C30         *         :                                                                                                                                                                                                           | specifies 1st column data<br>: rewritten into CGRAM address 1FH |

| 6th byte<br>(161th) | LSB       MSB         B0       B1       B2       B3       B4       B5       B6       B7         C4       C9       C14       C19       C24       C29       C34       *       :         LSB       B0       B1       B2       B3       B4       B5       B6       B7                                                                                                                                 | specifies 5th column data<br>: rewritten into CGRAM address 1FH |

| 2nd byte<br>(162th) | C0         C5         C10         C15         C20         C25         C30         *         :                                                                                                                                                                                                                                                                                                     | specifies 1st column data<br>(CGRAM address 00H is rewritten)   |

| 6th byte<br>(167th) | LSB<br>B0 B1 B2 B3 B4 B5 B6 B7<br>C4 C9 C14 C19 C24 C29 C34 * :                                                                                                                                                                                                                                                                                                                                   | specifies 5th column data<br>(CGRAM address 00H is rewritten)   |

X0 (LSB) to X3 (MSB): CGRAM addresses (4 bits: 16 characters) Note: A total of 32 characters for the two specifications. C0 (LSB) to C34 (MSB): Character pattern data (35 bits: 35 outputs per digit)

#### Positional relationship between the output area of CGROM and that of CGRAM

|                                        | C0         C5         C10         C15         C20         C25         C30 | C1<br>C6<br>C11<br>C16<br>C21<br>C26<br>C31 | C2<br>C7<br>C12<br>C17<br>C22<br>C27<br>C32 | C3         C8         C13         C18         C23         C28         C33 | C4         C9         C14         C19         C24         C29         C34 |                                                                                                                                                    |

|----------------------------------------|---------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| byte (1st column)<br>byte (2nd column) |                                                                           |                                             |                                             |                                                                           | <u> </u>                                                                  | area that corresponds to 6th byte (5th column)<br>area that corresponds to 5th byte (4th column)<br>area that corresponds to 4th byte (3rd column) |

area that corresponds to 2nd byte (1st column) area that corresponds to 3rd byte (2nd column)

Note: CGROM (Character Generator ROM) has an 8-bit address to generate 5×7 dot matrix character patterns.

The capacity is 224×35×8 bits, which can store 224 types of character patterns.

2 types of general-purpose code are availble (see ROM CODE list) and custom codes are provided on customer's request.

#### [CGROM addresses and set CGRAM addresses]

| Command | HEX | к0 | <b>V</b> 4 | К2         | кз | CGROM            | Command | HEX | к0 | <b>V</b> 4 | К2         | <b>K</b> 2 | CGROM            |

|---------|-----|----|------------|------------|----|------------------|---------|-----|----|------------|------------|------------|------------------|

| No.     | ПЕХ | NU | <b>NI</b>  | <b>n</b> 2 | NЭ | address          | No.     | ПЕЛ | NU | <b>N</b> I | <b>n</b> 2 | NЭ         | address          |

|         | 00  | 0  | 0          | 0          | 0  | RAM00(0000000B)  |         | 10  | 0  | 0          | 0          | 0          | RAM10(00010000B) |

|         | 01  | 1  | 0          | 0          | 0  | RAM01(0000001B)  |         | 11  | 1  | 0          | 0          | 0          | RAM11(00010001B) |

|         | 02  | 0  | 1          | 0          | 0  | RAM02(00000010B) |         | 12  | 0  | 1          | 0          | 0          | RAM12(00010010B) |

|         | 03  | 1  | 1          | 0          | 0  | RAM03(00000011B) |         | 13  | 1  | 1          | 0          | 0          | RAM13(00010011B) |

|         | 04  | 0  | 0          | 1          | 0  | RAM04(00000100B) |         | 14  | 0  | 0          | 1          | 0          | RAM14(00010100B) |

|         | 05  | 1  | 0          | 1          | 0  | RAM05(00000101B) |         | 15  | 1  | 0          | 1          | 0          | RAM15(00010101B) |

|         | 06  | 0  | 1          | 1          | 0  | RAM06(00000110B) |         | 16  | 0  | 1          | 1          | 0          | RAM16(00010110B) |

| 2       | 07  | 1  | 1          | 1          | 0  | RAM07(00000111B) | 4       | 17  | 1  | 1          | 1          | 0          | RAM17(00010011B) |

| 2       | 08  | 0  | 0          | 0          | 1  | RAM08(00001000B) | 4       | 18  | 0  | 0          | 0          | 1          | RAM18(00011000B) |

|         | 09  | 1  | 0          | 0          | 1  | RAM09(00001001B) |         | 19  | 1  | 0          | 0          | 1          | RAM19(00011001B) |

|         | 0A  | 0  | 1          | 0          | 1  | RAM0A(00001010B) |         | 1A  | 0  | 1          | 0          | 1          | RAM1A(00011010B) |

|         | 0B  | 1  | 1          | 0          | 1  | RAM0B(00001011B) |         | 1B  | 1  | 1          | 0          | 1          | RAM1B(00011011B) |

|         | 00  | 0  | 0          | 1          | 1  | RAM0C(00001100B) |         | 10  | 0  | 0          | 1          | 1          | RAM1C(00011100B) |

|         | 0D  | 1  | 0          | 1          | 1  | RAM0D(00001101B) |         | 1D  | 1  | 0          | 1          | 1          | RAM1D(00011101B) |

|         | 0E  | 0  | 1          | 1          | 1  | RAM0E(00001110B) |         | 1E  | 0  | 1          | 1          | 1          | RAM1E(00011110B) |

|         | 0F  | 1  | 1          | 1          | 1  | RAM0F(00001111B) |         | 1F  | 1  | 1          | 1          | 1          | RAM1F(00011111B) |

Refer to ROMCODE table

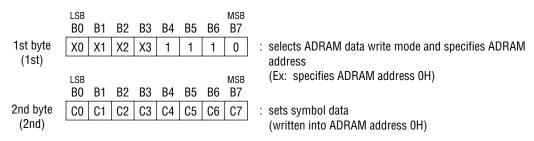

#### 7. ADRAM data write

(specifies address of ADRAM and writes symbol data)

ADRAM (Additional Data RAM) has a 4-bit address to store symbol data. Symbol data specified by ADRAM is directly output without CGROM and CGRAM. The capacity is 8×16 bits, which can store 8 types of symbol patterns for each digit. The terminal to which the contents of ADRAM are output can be used as a cursor.

[Command format]

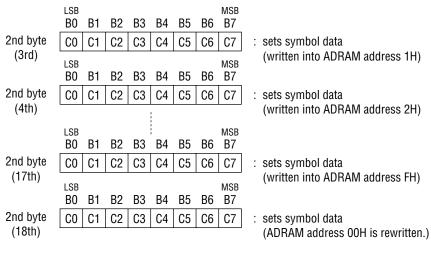

To specify symbol data continuously to the next address, specify only symbol data as follows. The address of ADRAM is automatically incremented. Specification of addresses is therefore unnecessary.

X0 (LSB) to X3 (MSB): ADRAM addresses (4 bits: 16 characters) C0 (LSB) to C7 (MSB): Symbol data (8-symbol data per digit)

| HEX | D0 | D1 | D2 | D3 | COM position | HEX | D0 | D1 | D2 | D3 | COM position |

|-----|----|----|----|----|--------------|-----|----|----|----|----|--------------|

| 0   | 0  | 0  | 0  | 0  | COM1         | 8   | 0  | 0  | 0  | 1  | COM9         |

| 1   | 1  | 0  | 0  | 0  | COM2         | 9   | 1  | 0  | 0  | 1  | COM10        |

| 2   | 0  | 1  | 0  | 0  | COM3         | А   | 0  | 1  | 0  | 1  | COM11        |

| 3   | 1  | 1  | 1  | 0  | COM4         | В   | 1  | 1  | 0  | 1  | COM12        |

| 4   | 0  | 0  | 1  | 0  | COM5         | С   | 0  | 0  | 1  | 1  | COM13        |

| 5   | 1  | 0  | 1  | 0  | COM6         | D   | 1  | 0  | 1  | 1  | COM14        |

| 6   | 0  | 1  | 1  | 0  | COM7         | Е   | 0  | 1  | 1  | 1  | COM15        |

| 7   | 1  | 1  | 1  | 0  | COM8         | F   | 1  | 1  | 1  | 1  | COM16        |

#### [COM positions and ADRAM addresses]

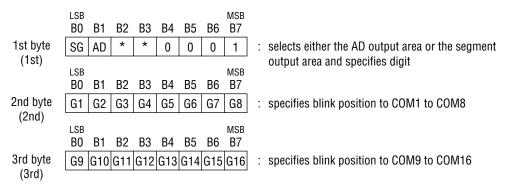

#### 8. Display blink position set

(sets the blink position for the SEG area or AD area in COMn.

Display blink position can be set separately for the SEG area and AD area. In this case, select by command in which COMn the SEG area or AD area is made blink.

The blink disabled state is entered for this setting when power is turned on or when a **RESET** signal is input. The display blink cycle is determined by the frequency to be input to the BLINK pin.

[Command format]

The 2nd and 3rd bytes (COM1 to COM16 position specification) are regarded as one data item, so 300 ns is sufficient for t<sub>DOFF</sub> time between bytes.

SG: Specifies SEG area AD: Specifies AD area Gn: Specifies blinks [SEG and AD display and set data]

| SG/AD | Gn | SEG and AD display               |                                                          |

|-------|----|----------------------------------|----------------------------------------------------------|

| 0     | 0  | Does not blink (current state)   | (The state when power is applied or when RESET is input) |

| 0     | 1  | Does not bilnk (current state)   |                                                          |

| 1     | 0  | Specified positions do not blink |                                                          |

| 1     | 1  | Specified positions blink        |                                                          |

Note: If both SG and AD are set to "1" by command, both the SEG area and the AD area are specified.

9. DCRAM address shift (Shifts SEG output left or right.)

${\rm DCRAM}$  address shift shifts SEG output 1 digit to the left or right using 1 bit data. AD output cannot be shifted.

[Command format]

|          | lsb<br>B0 | B1 | B2 | B3 | B4 | B5 | B6 | msb<br>B7 |  |

|----------|-----------|----|----|----|----|----|----|-----------|--|

| 1st byte | SG        | *  | *  | *  | 1  | 0  | 0  | 1         |  |

: selects DCRAM address shift and sets shift value (left, right)

S: Specifies the direction of shift

[Set data and shift direction of display]

| S | Shift direction of display |

|---|----------------------------|

| 0 | Shift to left              |

| 1 | Shift to right             |

# [DCRAM address shift and COM positions]

| Command<br>No. | HEX            | к0 | К1 | К2        | кз | COM<br>position | Command<br>No. | HEX              | ко | К1 | К2        | кз | COM<br>position |

|----------------|----------------|----|----|-----------|----|-----------------|----------------|------------------|----|----|-----------|----|-----------------|

|                | 00             | 0  | 0  | 0         | 0  | COM2            |                | 20               | 0  | 0  | 0         | 0  |                 |

|                | 01             | 1  | 0  | 0         | 0  | COM3            |                | 21               | 1  | 0  | 0         | 0  |                 |

| 1              | <br> <br> <br> |    |    | <br> <br> |    |                 | 3              | 1<br>1<br>1<br>1 |    |    | <br> <br> |    |                 |

|                | 0E             | 0  | 1  | 1         | 1  | COM16           |                | 2E               | 0  | 1  | 1         | 1  |                 |

|                | 0F             | 1  | 1  | 1         | 1  |                 |                | 2F               | 1  | 1  | 1         | 1  |                 |

|                | 10             | 0  | 0  | 0         | 0  |                 |                | 30               | 0  | 0  | 0         | 0  |                 |

|                | 11             | 1  | 0  | 0         | 0  |                 |                | 31               | 1  | 0  | 0         | 0  |                 |

| 2              | <br> <br>      |    |    | <br> <br> |    |                 | 4              | <br> <br> <br>   |    |    | <br> <br> |    |                 |

|                | 1E             | 0  | 1  | 1         | 1  |                 |                | 3E               | 0  | 1  | 1         | 1  |                 |

|                | 1F             | 1  | 1  | 1         | 1  |                 |                | 3F               | 1  | 1  | 1         | 1  | COM1            |

When S=0 (shift to left) is performed from the initial state.

When S=1 (shift to right) is performed from the initial state.

| Command<br>No. | HEX | к0 | К1 | К2        | КЗ | COM<br>position | Command<br>No. | HEX | к0 | К1 | К2        | КЗ | COM<br>position |

|----------------|-----|----|----|-----------|----|-----------------|----------------|-----|----|----|-----------|----|-----------------|

|                | 00  | 0  | 0  | 0         | 0  |                 |                | 20  | 0  | 0  | 0         | 0  |                 |

|                | 01  | 1  | 0  | 0         | 0  | COM1            |                | 21  | 1  | 0  | 0         | 0  |                 |

| 1              | 1   |    |    | <br> <br> |    |                 | 3              | 1   |    |    | <br> <br> |    |                 |

|                | 0E  | 0  | 1  | 1         | 1  | COM14           |                | 2E  | 0  | 1  | 1         | 1  |                 |

|                | 0F  | 1  | 1  | 1         | 1  | COM15           |                | 2F  | 1  | 1  | 1         | 1  |                 |

|                | 10  | 0  | 0  | 0         | 0  | COM16           |                | 30  | 0  | 0  | 0         | 0  |                 |

|                | 11  | 1  | 0  | 0         | 0  |                 |                | 31  | 1  | 0  | 0         | 0  |                 |

| 2              | 1   |    |    | <br> <br> |    |                 | 4              |     |    |    | 1         |    |                 |

|                | 1E  | 0  | 1  | 1         | 1  |                 |                | 3E  | 0  | 1  | 1         | 1  |                 |

|                | 1F  | 1  | 1  | 1         | 1  |                 |                | 3F  | 1  | 1  | 1         | 1  |                 |

#### A. DCRAM address reset

(returns display status to initial setting status)

The DCRAM address reset returns the status where a DCRAM address shift is executed to initial status.

[Command format]

|          | LSB |    |    |    |    |    |    | MSB |                               |

|----------|-----|----|----|----|----|----|----|-----|-------------------------------|

|          | B0  | B1 | B2 | B3 | B4 | B5 | B6 | B7  |                               |

| 1st byte | *   | *  | *  | *  | 0  | 1  | 0  | 1   | : selects DCRAM address reset |

Relation between the DCRAM address shifts and the COM outputs

Initial status or the status where display address reset executed (DCRAM address is 00H)

| COM output          | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|---------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| DCRAM address (HEX) | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F |

When left shift is executed in the initial status

| COM output          | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|---------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|