# **OKI** Semiconductor

This version: Nov. 1999

# **MSM7664**

**NTSC/PAL Digital Video Decoder**

#### **GENERAL DESCRIPTION**

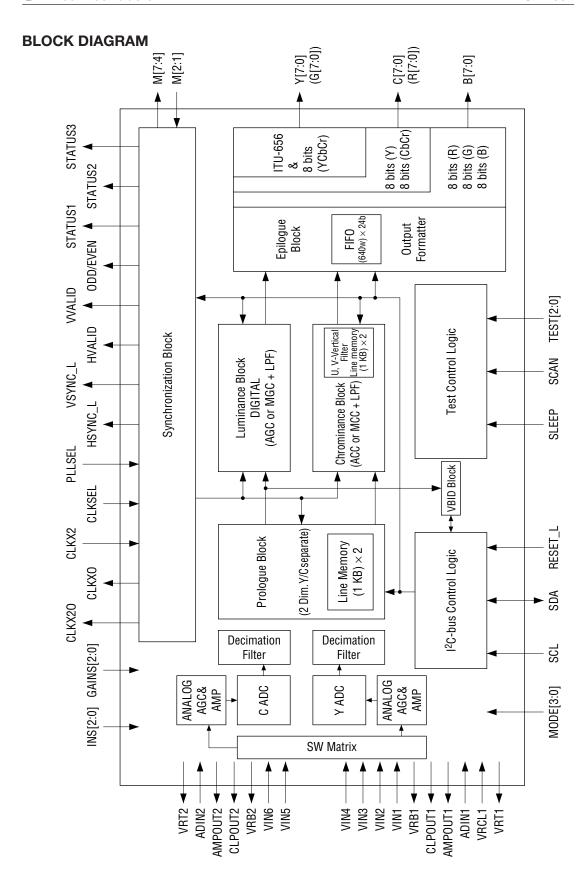

The MSM7664 is an LSI device that decodes NTSC or PAL analog video signals into YCbCr and RGB digital data based on ITU-RBT.601.

The device has built-in two channels of A/D converters and can accept composite video and S video signals for the input video signals. Composite video signals are converted to YCbCr and RGB digital data via the 2-dimensional Y/C separation circuit with an adaptive filter.

Analog video signals can be sampled by a clock at the pixel frequency or at twice the pixel frequency. A decimation filter is built-in for sampling at twice the pixel frequency.

Input signals are synchronized internally and high-speed locking for color burst is possible. Because a FIFO buffer is built into the output format circuit, jitter-free output can be obtained even for non-standard signals.

The MSM7664 is an improved version of the MSM7662, and is particularly superior in the picture quality and stabilization of synchronization in the PAL decoder as well as the stabilization of synchronization in the decoder under weak electric fields.

Further, although a part of the registers have been added, the electrical characteristics of both products are almost identical and their pin compatibility makes it possible to use the MSM7664 instead of the MSM7662.

### **APPLICATION EXAMPLES**

Since the synchronization of input signals and high-speed locking for color burst are possible, the device is optimized for applications used by switching multiple cameras.

It is also used for various image processing applications because of jitter-free output data through a built-in FIFO buffer.

Even in the PAL mode, a YC separation characteristics equivalent to the NTSC mode has been achieved thereby making this LSI ideally suitable for PAL mode applications.

8-bit (YCbCr), 16-bit (8-bit (Y) + 8-bit (CbCr)), and 24-bit (RGB) output interfaces can be selected as an output mode so that various devices such as monitoring system, digital video memory, digital TV, video processing unit and video communication unit can be selected on the receiving side.

## FEATURES (• new feature not found on MSM7662)

- Input analog signal

- NTSC/PAL composite video signal or S-video signal

- Maximum 5 composite or 2 S-video + 2 composite analog inputs can be connected (switchable by external pins or internal registers)

- Built-in clamp circuits and video amps

- Built-in 8-bit A/D converters (2 channels)

- 4 selectable output interfaces

ITU-RBT.656 (conditional)

8-bit (YCbCr) : 8-bit (YCbCr) : 4:2:2/YCbCr = 4:1:1 (limit)

16-bit (YCbCr) : 8-bit (Y) + 8-bit (CbCr) YCbCr = 4 : 2 : 2/YCbCr = 4 : 1 : 1 (limit)

24-bit RGB : 8-bit (R) + 8-bit (G) + 8-bit (B)

- High speed of burst locking has been realized.

- 2-dimensional Y/C separation using adaptive comb filter (this filter is bypassed for S-video signal input)

NTSC format: 3 lines or 2 lines, PAL format: 2 lines (adaptive transition method)

- Built-in vertical chrominance filter (straight output without using the filter is possible)

- Selectable data I/O signal synchronization

- 4 synchronization modes: internal FIFO modes (FIFO-1, FIFO-2) and external field memory modes (FM-1, FM-2) are selectable (FIFO-1 is normally selected).

- Compatible pixel frequencies (normal/twice the pixel frequency)

13.5 MHz (13.5/27 MHz) : NTSC/PAL ITU-RBT.601

12.272727 MHz (12.272727/24.545454 MHz) : NTSC Square pixel

14.31818 MHz (14.31818/28.63636 MHz) : NTSC 4fsc

14.75 MHz (14.75/29.5 MHz) : PAL Square Pixel

- Recognition of data in the VBI period (closed caption, CGMS, WSS, macrovision AGC and pseudo pulse) and function of reading from I<sup>2</sup>C-bus (only for ITU-RBT.601 mode).

- Built-in AGC/ACC circuits, compatible with a wide range of input levels Input level range: –8 dB to +3.5 dB (0.4 V to 1.5 V)

Switchable between AGC/MGC (fixed gain) and ACC/MCC (fixed gain)

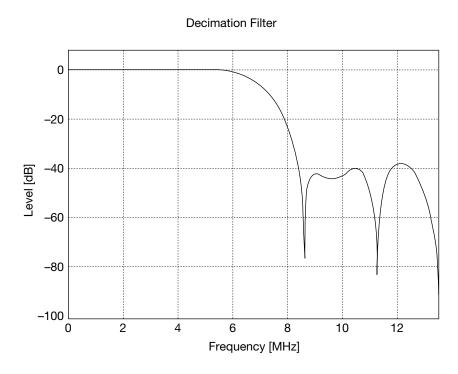

- Decimation filter built into input stage, allows easy configuration of filter prior to A/D converter (when input at twice the pixel frequency)

- Automatic NTSC/PAL recognition (only for ITU-RBT.601)

- o Sleep mode

- Hi-Z mode for output pins

- Multiplex signal recognition (closed caption)

During vertical blanking interval, data is output as 8-bit data.

- I2C-bus interface

- 3.3 V single power supply (I/O 5 V tolerance)

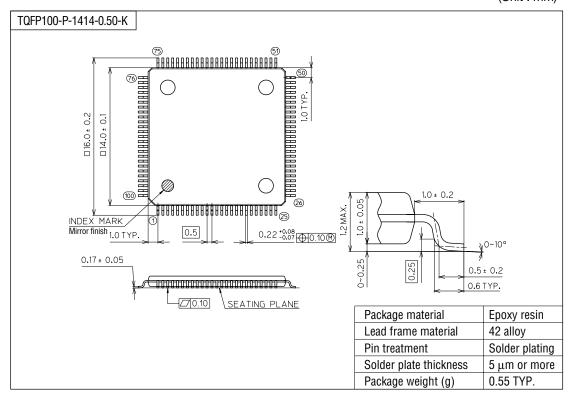

- Package:

100-pin plastic TQFP (TQFP100-P-1414-0.50-K) (Product name: MSM7664TB)

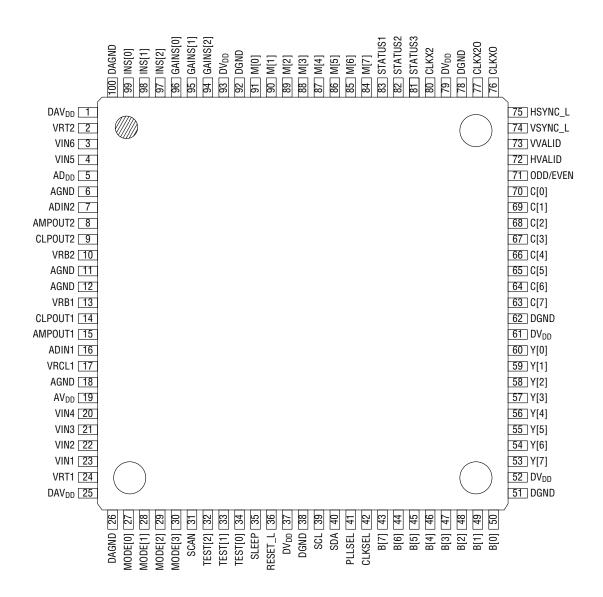

## **PIN CONFIGURATION (TOP VIEW)**

100-Pin Plastic TQFP

## **PIN DESCRIPTIONS**

| Pin | Symbol            | Туре | Description                                                           |

|-----|-------------------|------|-----------------------------------------------------------------------|

| 1   | DAV <sub>DD</sub> | _    | Digital power supply in A/D converter                                 |

| 2   | VRT2              | 0    | A/D converter reference voltage (high side) for S-video chroma signal |

| 3   | VINC              | ,    | S-video 2 chroma signal (C-2) input pin                               |

| 3   | VIN6              | I    | (leave open or connect to AGND when not used)                         |

| 4   | VINE              |      | Composite-5 or S-video 1 chroma signal (C-1) input pin                |

| 4   | VIN5              | I    | (leave open or connect to AGND when not used)                         |

| 5   | AV <sub>DD</sub>  | _    | Analog power supply                                                   |

| 6   | AGND              | _    | Analog ground                                                         |

| 7   | ADIN2             | I    | A/D converter input pin for S-video chroma signal                     |

| 8   | AMPOUT2           | 0    | S-video chroma signal amp output                                      |

| 9   | CLPOUT2           | 0    | S-video chroma signal clamp voltage output                            |

| 10  | VRB2              | 0    | A/D converter reference voltage (low side) for S-video chroma signal  |

| 11  | AGND              | _    | Analog ground                                                         |

| 12  | AGND              | _    | Analog ground                                                         |

| 10  | \/DD4             | ı    | A/D converter reference voltage (low side) for composite/S-video      |

| 13  | 13 VRB1           |      | (luminance signal)                                                    |

| 14  | CLPOUT1           | 0    | Composite/S-video (luminance signal) clamp voltage output             |

| 15  | AMPOUT1           | 0    | Composite/S-video (luminance signal) amp output                       |

| 16  | ADIN1             | ı    | A/D converter input pin for composite/S-video (luminance signal)      |

| 17  | VRCL1             | I    | S-video (luminance signal) clamp voltage input                        |

| 18  | AGND              | _    | Analog ground                                                         |

| 19  | AV <sub>DD</sub>  | _    | Analog power supply                                                   |

| 20  | VIN4              | ı    | Composite-4 input (leave open or connect to AGND when not used)       |

| 21  | VIN3              | ı    | Composite-3 input (leave open or connect to AGND when not used)       |

| 00  | VINO              | ١,   | Composite-2 S-video 2 luminance signal (Y-2) input                    |

| 22  | VIN2              | I    | (leave open or connect to AGND when not used)                         |

| 00  | 7//8/4            |      | Composite-1 S-video 1 luminance signal (Y-1) input                    |

| 23  | VIN1              | I    | (leave open or connect to AGND when not used)                         |

| 0.4 | \/DT/             |      | A/D converter reference voltage (high side) for composite/S-video     |

| 24  | VRT1              | 0    | (luminance signal)                                                    |

| 25  | DAV <sub>DD</sub> | _    | Digital power supply in A/D converter                                 |

| 26  | DAGND             | _    | Digital ground in A/D converter                                       |

| Pin      | Symbol           | Туре     | Description                                                                       |

|----------|------------------|----------|-----------------------------------------------------------------------------------|

| 27       | MODE[0]          | ı        | I/O switching input during external setting mode                                  |

| 28       | MODE[1]          | I        | (pulled-down by internal resistors)                                               |

| 29       | MODE[2]          | I        | Internal/external pins are switched by register MRA[0]                            |

| 30       | MODE[3]          | I        | The default of register MRA[0] is external pin mode.                              |

|          |                  |          | MODE [3:2] Output mode selection                                                  |

|          |                  |          | 00: ITU-RBT.656 (with 8-bit YCbCr SAV, EAV, blank processing)                     |

|          |                  |          | 01: 8-bit (YCbCr)                                                                 |

|          |                  |          | 10: 16-bit (YCbCr) (ITU-RBT.601)                                                  |

|          |                  |          | 11: 24-bit RGB                                                                    |

|          |                  |          | MODE [1] Input mode selection                                                     |

|          |                  |          | 0: NTSC 1: PAL                                                                    |

|          |                  |          | Invalid if an ITU-RBT.601 signal is input while the register MRC[7] is set        |

|          |                  |          | to automatic NTSC/PAL recognition.                                                |

|          |                  |          | MODE [0] Input mode calcation                                                     |

|          |                  |          | MODE [0] Input mode selection  0: ITU-RBT.601 1: Square Pixel                     |

|          |                  |          | NTSC 4fsc can be set by register MRA [3:1] only.                                  |

|          | 00481            |          | 7 7 1 7                                                                           |

| 31       | SCAN             | l        | Not used. Be left open or fixed at "0" (pulled down by internal resistor).        |

| 32       | TEST[2]          | I        | Not used. Be left open or fixed at "0" (pulled down by internal resistor).        |

| 33       | TEST[1]          | l        | Not used. Be left open or fixed at "0" (pulled down by internal resistor).        |

| 34       | TEST[0]          | l        | Not used. Be left open or fixed at "0" (pulled down by internal resistor).        |

| 35       | SLEEP            | <u> </u> | 0: normal operation, 1: sleep operation                                           |

| 36       | RESET_L          | l        | Reset input pin (active "L"). After powering ON, be sure to reset.                |

| 37       | DV <sub>DD</sub> | _        | Digital power supply                                                              |

| 38       | DGND             |          | Digital ground                                                                    |

| 39       | SCL              |          | I <sup>2</sup> C-bus clock input                                                  |

| 40       | SDA              | 1/0      | I <sup>2</sup> C-bus data I/O pin                                                 |

| 41       | PLLSEL           | l        | Not used. Be left open or fixed at "0" (pulled down by internal resistor).        |

|          |                  |          | Clock select input pin (pulled down by internal resistor).                        |

| 42       | CLKSEL           | I        | 0: double-speed input mode 1: normal input mode                                   |

| -        |                  |          | When a double-speed input mode is used, input a double frequency to system clock. |

|          |                  |          | Data output B[7]: MSB, B[0]: LSB                                                  |

| 43 to 50 | B[7] to B[0]     | 0        | During RGB output mode: B 8-bit data output                                       |

|          |                  |          | Other than RGB output mode: Hi-Z                                                  |

|          |                  |          | Output mode is set by pin 27 or 28, or register MRA [7:6].                        |

| 51       | DGND             | _        | Digital ground                                                                    |

| 52       | $DV_DD$          | _        | Digital power supply                                                              |

| Pin      | Symbol           | Туре | Description                                                           |  |  |  |  |

|----------|------------------|------|-----------------------------------------------------------------------|--|--|--|--|

|          |                  |      | Data output Y[7]: MSB, Y[0]: LSB                                      |  |  |  |  |

|          |                  |      | During ITU-RBT.656 output mode: YCbCr 8-bit data output               |  |  |  |  |

| E0 to 60 | V[7] to V[0]     | _    | During 8-bit (YCbCr) output mode: YCbCr 8-bit data output             |  |  |  |  |

| 53 to 60 | Y[7] to Y[0]     | 0    | During 16-bit (YCbCr) output mode: Y 8-bit data output                |  |  |  |  |

|          |                  |      | During 24-bit RGB output mode: G 8-bit data output                    |  |  |  |  |

|          |                  |      | Output mode is set by pin 27 or 28, or register MRA [7:6].            |  |  |  |  |

| 61       | DV <sub>DD</sub> | _    | Digital power supply                                                  |  |  |  |  |

| 62       | DGND             | _    | Digital ground                                                        |  |  |  |  |

|          |                  |      | Data output C[7]: MSB, C[0]: LSB                                      |  |  |  |  |

|          |                  |      | During ITU-RBT.656 output mode: Hi-Z                                  |  |  |  |  |

| CO += 70 | 0171 +- 0101     |      | During 8-bit (YCbCr) output mode: Hi-Z                                |  |  |  |  |

| 63 to 70 | C[7] to C[0]     | 0    | During 16-bit (YCbCr) output mode: CbCr 8-bit data output             |  |  |  |  |

|          |                  |      | During 24-bit RGB output mode: R 8-bit data output                    |  |  |  |  |

|          |                  |      | Output mode is set by pin 27 or 28, or register MRA [7:6].            |  |  |  |  |

| 74       | ODD/EVEN         | 0    | Field display output                                                  |  |  |  |  |

| 71       | ODD/EVEN         | 0    | If field is odd, "H" is output.                                       |  |  |  |  |

| 70       | LIVALID          |      | Horizontal valid pixel timing output pin                              |  |  |  |  |

| 72       | HVALID           | 0    | If section is valid, "H" is output.                                   |  |  |  |  |

| 70       | \/\/ALID         |      | Vertical valid line timing output pin                                 |  |  |  |  |

| 73       | VVALID           | 0    | If section is valid, "H" is output.                                   |  |  |  |  |

| 74       | VSYNC_L          | 0    | Vertical sync signal (V sync) output pin                              |  |  |  |  |

| 75       | HSYNC_L          | 0    | Horizontal sync signal (H sync) output pin                            |  |  |  |  |

|          |                  |      | Pixel clock output                                                    |  |  |  |  |

|          |                  |      | During double-speed input mode (pin 42 = 0): One half of system clock |  |  |  |  |

| 76       | CLKX0            | 0    | frequency is output.                                                  |  |  |  |  |

|          |                  |      | During normal input mode (pin 42 = 1): The same frequency as system   |  |  |  |  |

|          |                  |      | clock frequency is output.                                            |  |  |  |  |

| 77       | CLKX20           | 0    | System clock output                                                   |  |  |  |  |

| 11       | OLKAZO           | U    | System clock input is directly output.                                |  |  |  |  |

| 78       | DGND             | _    | Digital ground                                                        |  |  |  |  |

| 79       | DV <sub>DD</sub> | _    | Digital power supply                                                  |  |  |  |  |

|          |                  |      | System clock input (selected by operation mode)                       |  |  |  |  |

|          |                  |      | Normal input mode Double-speed input mode                             |  |  |  |  |

|          |                  |      | NTSC ITU-RBT.601 13.5 MHz 27 MHz                                      |  |  |  |  |

| 80       | CLKX2            | I    | NTSC Square Pixel 12.272727 MHz 24.545454 MHz                         |  |  |  |  |

|          |                  |      | NTSC 4fsc 14.31818 MHz 28.63636 MHz                                   |  |  |  |  |

|          |                  |      | PAL ITU-RBT.601 13.5 MHz 27 MHz                                       |  |  |  |  |

|          |                  |      | PAL Square Pixel 14.75 MHz 29.5 MHz                                   |  |  |  |  |

| Pin | Symbol           | Туре | Description                                                                    |  |  |  |

|-----|------------------|------|--------------------------------------------------------------------------------|--|--|--|

|     |                  |      | Status signal output                                                           |  |  |  |

|     |                  |      | Selected by internal register OMR[0]                                           |  |  |  |

| 81  | STATUS[3]        | 0    | OMR[0]: 0 FIFO overflow detection (default)                                    |  |  |  |

|     |                  |      | 0: non-detection, 1: detection                                                 |  |  |  |

|     |                  |      | OMR[0]: 1 CSYNC output                                                         |  |  |  |

|     |                  |      | Status signal output                                                           |  |  |  |

|     |                  |      | Selected by internal register OMR[1]                                           |  |  |  |

| 82  | [CIQUITATO       | 0    | OMR[1]: 0 NTSC-PAL recognition (default)                                       |  |  |  |

| 02  | STATUS[2]        | U    | 0: NTSC, 1: PAL                                                                |  |  |  |

|     |                  |      | OMR[1]: 1 HLOCK sync detection output                                          |  |  |  |

|     |                  |      | 0: non-detection, 1: detection                                                 |  |  |  |

| 83  | STATUS[1]        | 0    | VBI interval multiplex signal detection output                                 |  |  |  |

|     | STATUS[1]        | U    | 0: non-detection, 1: detection                                                 |  |  |  |

| 84  | M[7]             | 0    | Field memory control signal; RE output                                         |  |  |  |

| 85  | M[6]             | 0    | Field memory control signal; WE output                                         |  |  |  |

| 86  | M[5]             | 0    | Field memory control signal; RSTR output                                       |  |  |  |

| 87  | M[4]             | 0    | Field memory control signal; RSTW output                                       |  |  |  |

| 88  | M[3]             | 0    | Test output pin, normally "L" output                                           |  |  |  |

|     |                  |      | I <sup>2</sup> C-bus slave address select                                      |  |  |  |

| 89  | M[2]             | I    | 0: 1000001X                                                                    |  |  |  |

|     |                  |      | 1: 1000011X (no internal pull-up or pull-down resistor)                        |  |  |  |

|     |                  |      | Pin for setting by either external pin or internal register in order to select |  |  |  |

|     |                  |      | analog unit gain value (MGC) and video signal input pin.                       |  |  |  |

|     |                  |      | (no internal pull-up or pull-down resistor)                                    |  |  |  |

|     |                  |      | 0: external pin mode                                                           |  |  |  |

| 90  | M[1]             | ı    | Gain value setting: pins 94 to 96 (GAINS[2:0]) are used                        |  |  |  |

| 00  | [.]              | '    | Input pin setting: pins 97 to 99 (INS[2:0]) are used                           |  |  |  |

|     |                  |      | 1: register mode                                                               |  |  |  |

|     |                  |      | Gain value setting: register ADC2[6:4]                                         |  |  |  |

|     |                  |      | Input pin setting: register ADC1[2:0]                                          |  |  |  |

|     |                  |      | Internal register setting is invalid when external pin mode is set.            |  |  |  |

|     |                  |      | Selection of external field memory control signal output                       |  |  |  |

| 91  | M[0]             | ı    | If field memory is not used, set M[0] to 0.                                    |  |  |  |

| 31  | Wi[O]            | '    | 0: M[7:4] outputs are invalid                                                  |  |  |  |

|     |                  |      | 1: M[7:4] outputs are valid                                                    |  |  |  |

| 92  | DGND             | _    | Digital ground                                                                 |  |  |  |

| 93  | DV <sub>DD</sub> | _    | Digital power supply                                                           |  |  |  |

| Pin | Symbol   | Туре |                   | Description                                                          |  |  |  |  |

|-----|----------|------|-------------------|----------------------------------------------------------------------|--|--|--|--|

| 94  | GAINS[2] | ı    | Inputs for ampli  | nputs for amplifier gain switch setting during external setting mode |  |  |  |  |

| 95  | GAINS[1] | I    | External pin mo   | External pin mode: pin 90 (M[1]) = 0                                 |  |  |  |  |

| 96  | GAINS[0] | I    | (pulled down by   | internal resistors)                                                  |  |  |  |  |

|     |          |      | GAINS[2:0]        | Gain value (x times)                                                 |  |  |  |  |

|     |          |      | [000]             | 1.00                                                                 |  |  |  |  |

|     |          |      | [001]             | 1.35                                                                 |  |  |  |  |

|     |          |      | [010]             | 1.75                                                                 |  |  |  |  |

|     |          |      | [011]             | 2.30                                                                 |  |  |  |  |

|     |          |      | [100]             | 3.00                                                                 |  |  |  |  |

|     |          |      | [101]             | 3.80                                                                 |  |  |  |  |

|     |          |      | [110]             | 5.00                                                                 |  |  |  |  |

|     |          |      | [111]             | Undefined                                                            |  |  |  |  |

| 97  | INS[2]   | I    | Inputs for signa  | I input pin switch setting during external setting mode              |  |  |  |  |

| 98  | INS[1]   | I    | External pin mo   | de: pin 90 (M[1]) = 0                                                |  |  |  |  |

| 99  | INS[0]   | I    | (pulled down by   | internal resistors)                                                  |  |  |  |  |

|     |          |      | INS[2:0]          | Input pin                                                            |  |  |  |  |

|     |          |      | [000]             | VIN1 (pin 23) Composite-1                                            |  |  |  |  |

|     |          |      | [001]             | VIN2 (pin 22) Composite-2                                            |  |  |  |  |

|     |          |      | [010]             | VIN3 (pin 21) Composite-3                                            |  |  |  |  |

|     |          |      | [011]             | VIN4 (pin 20) Composite-4                                            |  |  |  |  |

|     |          |      | [100]             | VIN5 (pin 4) Composite-5                                             |  |  |  |  |

|     |          |      | [101]             | VIN1 (pin 23) Y-1                                                    |  |  |  |  |

|     |          |      |                   | VIN5 (pin 4) C-1                                                     |  |  |  |  |

|     |          |      | [110]             | VIN2 (pin 22) Y-2                                                    |  |  |  |  |

|     |          |      |                   | VIN6 (pin 3) C-2                                                     |  |  |  |  |

|     |          |      | [111]             | Prohibited setting (ADC enters sleep state)                          |  |  |  |  |

| 100 | DAGND    | _    | Digital ground in | n A/D converter                                                      |  |  |  |  |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter            | Symbol           | Condition               | Rating       | Unit |

|----------------------|------------------|-------------------------|--------------|------|

| Power Supply Voltage | $V_{DD}$         | Ta = 25°C               | -0.3 to +4.5 | V    |

| Input Voltage        | VI               | V <sub>DD</sub> = 3.3 V | −0.3 to +5.5 | V    |

| Power Consumption    | PW               | _                       | 1            | W    |

| Storage Temperature  | T <sub>STG</sub> | _                       | −55 to +150  | °C   |

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter                       | Symbol                | Condition                    | Min.                | Тур. | Max.                 | Unit             |

|---------------------------------|-----------------------|------------------------------|---------------------|------|----------------------|------------------|

| Power Supply Voltage            | $V_{DD}$              | _                            | 3.0                 | 3.3  | 3.45                 | ٧                |

| Power Supply Voltage            | GND                   |                              | _                   | 0    | _                    | V                |

| Digital "H" Lovel Input Voltage | V <sub>IH1</sub>      | _                            | 2.2                 | _    | V <sub>DD</sub> (*2) | V                |

| Digital "H" Level Input Voltage | V <sub>IH2</sub> (*1) | _                            | $0.8 \times V_{DD}$ | _    | V <sub>DD</sub> (*2) | ٧                |

| Digital "L" Level Input Voltage | V <sub>IL</sub>       | _                            | 0                   | _    | 0.8                  | ٧                |

| Analog Video Signal Input       | V <sub>AIN</sub>      | SYNC tip to white peak level | 0.8                 | _    | 1.1                  | V <sub>P-P</sub> |

| Operating Temperature           | Та                    | _                            | 0                   | _    | 60                   | °C               |

<sup>\*1:</sup> CLKSEL, SDA, CLKXO

<sup>\*2:</sup> Since the inputs have a tolerance of up to 5.5 V, it is possible to apply 5 V to the inputs.

## **ELECTRICAL CHARACTERISTICS**

#### **DC** Characteristics

$(Ta = 0 \text{ to } +70^{\circ}\text{C}, V_{DD} (DV_{DD}, ADV_{DD}, AV_{DD}) = 3.0 \text{ to } 3.45 \text{ V})$

| Parameter                   | Symbol            | Condition                      | Min.                  | Тур. | Max.     | Unit |

|-----------------------------|-------------------|--------------------------------|-----------------------|------|----------|------|

| IIIII I aval Outaut Valtaga | V                 | $I_{OH} = -4 \text{ mA (*1)}$  | 0.7 × V <sub>DD</sub> |      | W        | V    |

| "H" Level Output Voltage    | V <sub>OH</sub>   | $I_{OH} = -6 \text{ mA (*2)}$  | U.7 × VDD             | _    | $V_{DD}$ | V    |

| "I " Laval Output Valtaga   | Va                | $I_{0L} = 4 \text{ mA (*1)}$   | 0                     |      | 0.4      | V    |

| "L" Level Output Voltage    | V <sub>OL</sub>   | $I_{0L} = 6 \text{ mA (*2)}$   | U                     | _    | 0.4      | V    |

|                             |                   | $V_I = GND \text{ to } V_{DD}$ | -10                   | _    | +10      | μА   |

| Input Leakage Current       | II                | R <sub>pull_down</sub> =       | 20                    | _    | 250      |      |

|                             |                   | 50 kΩ (*3)                     |                       |      |          | μΑ   |

| Output Leakage Current      | I <sub>0</sub>    | $V_I = GND \text{ to } V_{DD}$ | -10                   | _    | +10      | μА   |

| SDA Output Voltage          | SDAV <sub>L</sub> | I <sub>OL</sub> = 4 mA         | 0                     | _    | 0.4      | V    |

| SDA Output Current          | SDAI <sub>0</sub> | _                              | 3                     | _    | _        | mA   |

<sup>\*1:</sup> HSYNC\_L, VSYNC\_L, SYSSEL, C[7:0], B[7:0], ODD, VVALID, HVALID, CLKXO, HSY, M[7:0]

## **DC Characteristics (Analog Unit)**

$(Ta = 0 \text{ to } +70^{\circ}\text{C}, V_{DD} \text{ } (DV_{DD}, ADV_{DD}, AV_{DD}) = 3.0 \text{ to } 3.45 \text{ V}, \text{ } GND = 0 \text{ V})$

| Parameter             | Symbol             | Condition                 | Min.     | Тур. | Max.            | Unit             |

|-----------------------|--------------------|---------------------------|----------|------|-----------------|------------------|

| AMPOUT Output Voltage | V <sub>OAMP</sub>  | $R_0 = 300 \Omega$        | 0.3      | _    | 2.4             | V                |

| CLPOUT Output Voltage | V <sub>OCLP</sub>  | $R_0 = 5 \text{ k}\Omega$ | 0.2      | _    | 1.6             | V                |

| VRT Output Voltage    | V <sub>RT</sub>    | (*)                       | 1.95     | 2.3  | 2.5             | V                |

| VRB Output Voltage    | $V_{RB}$           | (*)                       | 0.15     | 0.3  | 0.4             | V                |

| ADIN                  | V <sub>IADIN</sub> | _                         | $V_{RB}$ | _    | V <sub>RT</sub> | V                |

| VIN                   | V <sub>IVIN</sub>  | Capacitive coupling       | 0.4      | _    | 1.3             | V <sub>P-P</sub> |

| Input Current         | I <sub>IVIN</sub>  | V <sub>I</sub> = 1.5 V    | 5        | _    | 30              | μА               |

<sup>\*:</sup>  $10 \text{ k}\Omega$  connected between  $V_{RT}$  and  $V_{RB}$

#### **DC** Characteristics

$(Ta = 0 \text{ to } +70^{\circ}\text{C}, V_{DD} \text{ } (DV_{DD}, ADV_{DD}, AV_{DD}) = 3.0 \text{ to } 3.45 \text{ V}, GND = 0 \text{ V})$

| Parameter                        | Symbol            | Condition              | Min. | Тур. | Max. | Unit |

|----------------------------------|-------------------|------------------------|------|------|------|------|

|                                  |                   | AD1 on                 |      |      |      |      |

| Power Supply Current (Operating) | $I_{D1}$          | AD2 off                | 120  | 190  | 260  | mA   |

|                                  |                   | CLKX2 = 27 MHz         |      |      |      |      |

|                                  |                   | AD1 on                 |      |      |      |      |

| Power Supply Current (Operating) | $I_{D2}$          | AD2 on                 | 120  | 200  | 275  | mA   |

|                                  |                   | CLKX2 = 27 MHz         |      |      |      |      |

| Power Supply Current (Sleep)     | I <sub>DOFF</sub> | V <sub>I</sub> = 1.5 V | 0    | _    | 5    | mA   |

<sup>\*2:</sup> Y[7:0], CLKX2O

<sup>\*3:</sup> MODE[3:0], SCAN, TEST[2:0], PLLSEL, CLKSEL, GAINS[2:0], INS[2:0]

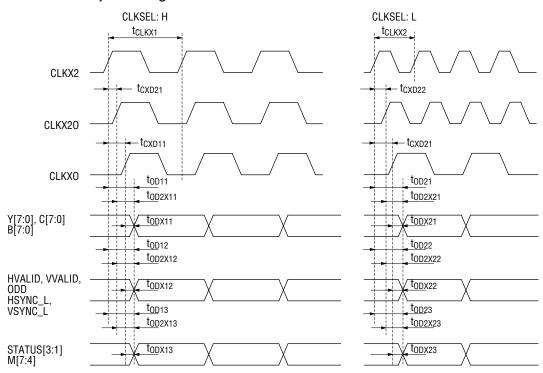

## **AC Characteristics (Double Speed Mode)**

$(Ta = 0 \text{ to } +70^{\circ}\text{C}, V_{DD} \text{ } (DV_{DD}, ADV_{DD}, AV_{DD}) = 3.0 \text{ to } 3.45 \text{ V}, GND = 0 \text{ V})$

| Parameter                                     | Symbol               | Condition                            | Min.  | Тур.      | Max.    | Unit |

|-----------------------------------------------|----------------------|--------------------------------------|-------|-----------|---------|------|

|                                               |                      | ITU-RS601                            | _     | 27.0      | _       | MHz  |

| CLIVVO Cuela Fraguenou                        | 1/4                  | NTSC 4fsc                            | _     | 28.63636  | _       | MHz  |

| CLKX2 Cycle Frequency                         | 1/t <sub>CLKX2</sub> | NTSC Square Pixel                    | _     | 24.545454 | _       | MHz  |

|                                               |                      | PAL Square Pixel                     | _     | 29.5      | _       | MHz  |

| CLKX2 Duty                                    | t <sub>D_D2</sub>    | _                                    | 45    | _         | 55      | %    |

| Output Data Delay Time 1 (*)                  | t <sub>OD21</sub>    | CLKSEL : L                           | 7 (5) | _         | 26 (24) | ns   |

| Output Data Delay Time 2 (*)                  | t <sub>OD22</sub>    | CLKSEL : L                           | 6 (4) | _         | 22 (20) | ns   |

| Output Data Delay Time 3 (*)                  | t <sub>OD23</sub>    | CLKSEL : L                           | 7 (5) | _         | 30 (28) | ns   |

| Output Data Delay Time 1X1 (*)                | t <sub>ODX21</sub>   | CLKSEL : L                           | 2     | _         | 8       | ns   |

| Output Data Delay Time 1X2 (*)                | t <sub>ODX22</sub>   | CLKSEL : L                           | 1     | _         | 5       | ns   |

| Output Data Delay Time 1X3 (*)                | t <sub>ODX23</sub>   | CLKSEL : L                           | 2     | _         | 10      | ns   |

| Output Data Delay Time 2X1 (*)                | t <sub>OD2X21</sub>  | CLKSEL : L                           | 3 (1) | _         | 11 (9)  | ns   |

| Output Data Delay Time 2X2 (*)                | t <sub>OD2X22</sub>  | CLKSEL : L                           | 2 (1) | _         | 9 (7)   | ns   |

| Output Data Delay Time 2X3 (*)                | t <sub>OD2X23</sub>  | CLKSEL : L                           | 3 (1) | _         | 13 (11) | ns   |

| Output Clock Delay Time (*)<br>(CLKX2-CLKXO)  | t <sub>CXD21</sub>   | CLKSEL : L                           | 5     | _         | 20      | ns   |

| Output Clock Delay Time (*)<br>(CLKX2-CLKX20) | t <sub>CXD22</sub>   | CLKSEL : L                           | 4     | _         | 17      | ns   |

| SCL Clock Cycle Time                          | t <sub>C_SCL</sub>   | $R_{pull\_up} = 4.7 \text{ k}\Omega$ | 200   | _         | _       | ns   |

| SCL Low Level Cycle                           | t <sub>L_SCL</sub>   | $R_{pull\_up} = 4.7 \text{ k}\Omega$ | 100   |           |         | ns   |

| RESET_L Width                                 | t <sub>RST_W</sub>   |                                      | 200   | _         | _       | ns   |

<sup>(\*)</sup> Output load: 40 pF

Values in the parentheses indicate the delay time when 8-bit YCbCr format data is output from the Y pin. The clock frequency accuracy is within ±100 ppm.

## **AC Characteristics (Single Speed Mode)**

(Ta = 0 to +70°C,  $V_{DD}$  (D $V_{DD}$ , AD $V_{DD}$ , AV $_{DD}$ ) = 3.0 to 3.45 V, GND = 0 V)

| Parameter                      | Symbol               | Condition                            | Min. | Тур.      | Max. | Unit |

|--------------------------------|----------------------|--------------------------------------|------|-----------|------|------|

|                                |                      | ITU-RS601                            | _    | 13.5      | _    | MHz  |

| CLIVVO Cycle Fraguency         | 4 /4                 | NTSC 4fsc                            | _    | 14.31818  | _    | MHz  |

| CLKX2 Cycle Frequency          | 1/t <sub>CLKX2</sub> | NTSC Square Pixel                    | _    | 12.272727 | _    | MHz  |

|                                |                      | PAL Square Pixel                     | _    | 14.75     | _    | MHz  |

| CLKX2 Duty                     | t <sub>D_D1</sub>    | CLKSEL : H                           | 40   |           | 60   | %    |

| Output Data Delay Time 1 (*)   | t <sub>OD11</sub>    | CLKSEL : H                           | 8    | _         | 26   | ns   |

| Output Data Delay Time 2 (*)   | t <sub>OD12</sub>    | CLKSEL : H                           | 7    | _         | 22   | ns   |

| Output Data Delay Time 3 (*)   | t <sub>OD13</sub>    | CLKSEL : H                           | 8    | _         | 30   | ns   |

| Output Data Delay Time 1X1 (*) | t <sub>ODX11</sub>   | CLKSEL : H                           | 2    | _         | 8    | ns   |

| Output Data Delay Time 1X2 (*) | t <sub>ODX12</sub>   | CLKSEL : H                           | 1    | _         | 5    | ns   |

| Output Data Delay Time 1X3 (*) | t <sub>ODX13</sub>   | CLKSEL : H                           | 2    | _         | 12   | ns   |

| Output Data Delay Time 2X1 (*) | t <sub>OD2X11</sub>  | CLKSEL : H                           | 3    | _         | 11   | ns   |

| Output Data Delay Time 2X2 (*) | t <sub>OD2X12</sub>  | CLKSEL : H                           | 2    | _         | 8    | ns   |

| Output Data Delay Time 2X3 (*) | t <sub>OD2X13</sub>  | CLKSEL : H                           | 3    | _         | 15   | ns   |

| Output Clock Delay Time (*)    | +                    | CLKSEL : H                           | 6    |           | 20   | no   |

| (CLKX2-CLKX0)                  | t <sub>CXD11</sub>   | ULNOEL . II                          | 0    | _         | 20   | ns   |

| Output Clock Delay Time (*)    | +.                   | CLKSEL : H                           | 5    |           | 17   | no   |

| (CLKX2-CLKX20)                 | t <sub>CXD12</sub>   | ULKSEL . H                           | 3    | _         | 17   | ns   |

| SCL Clock Cycle Time           | t <sub>C_SCL</sub>   | $R_{pull\_up} = 4.7 \text{ k}\Omega$ | 200  | _         | _    | ns   |

| SCL Low Level Cycle            | t <sub>L_SCL</sub>   | $R_{pull\_up} = 4.7 \text{ k}\Omega$ | 100  |           |      | ns   |

| RESET_L Width                  | t <sub>RST_W</sub>   |                                      | 200  |           |      | ns   |

<sup>(\*)</sup> Output load: 40 pF

The clock frequency accuracy is within ±100 ppm.

## INPUT AND OUTPUT TIMING

## **Clock and Output Timing**

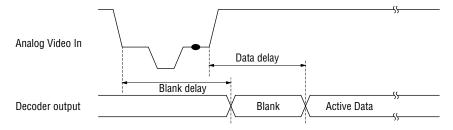

### Data Delay (when a standard signal is input)

T = 1 pixel rate,  $\alpha$  = absorption difference

| Video Mode | Input Signal | FIFO/FM Mode | Amount of Delay |  |  |  |  |  |

|------------|--------------|--------------|-----------------|--|--|--|--|--|

| NTSC       | Composite    | FIFO-1       | 1H + 358T ±α    |  |  |  |  |  |

| NTSC       | Composite    | FM           | 1H + 358T       |  |  |  |  |  |

| PAL        | Composite    | FIFO-1       | 1H + 358T ±α    |  |  |  |  |  |

| PAL        | Composite    | FM           | 1H + 358T       |  |  |  |  |  |

| NTSC, PAL  | S-Video      | FIFO-1       | 358T ±α         |  |  |  |  |  |

| NTSC, PAL  | S-Video      | FM           | 358T            |  |  |  |  |  |

The data delay is equal to the blank delay. 1H depends on the sampling mode. The numeric value (T value) may be changed according to a signal state. Since the output period is fixed during FIFO mode, the amount of delay is changed. If Y/C separation is performed using TRAP filter during PAL mode, 1H is not added.

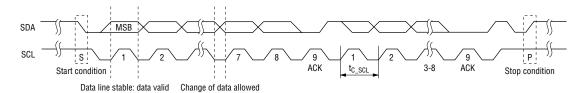

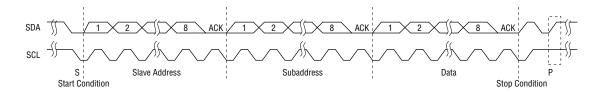

## I<sup>2</sup>C-bus Interface Input/Output Timing

The basic input/output timing of the I<sup>2</sup>C-bus is indicated below.

## I<sup>2</sup>C-bus Timing

| Symbol               | Parameter                  | Min. | Max. | Unit |

|----------------------|----------------------------|------|------|------|

| f <sub>SCL</sub>     | SCL Frequency              | 0    | 100  | kHz  |

| t <sub>BUF</sub>     | Bus Open Period            | 4.7  |      | μs   |

| t <sub>HD: STA</sub> | Start Condition Hold Time  | 4.0  |      | μs   |

| $t_{LOW}$            | Clock Low Period           | 4.7  |      | μs   |

| t <sub>HIGH</sub>    | Clock High Period          | 4.0  |      | μs   |

| t <sub>SU: STA</sub> | Start Condition Setup Time | 4.7  |      | μs   |

| t <sub>HD: DAT</sub> | Data Hold Time             | 300  |      | ns   |

| t <sub>SU: DAT</sub> | Data Setup Time            | 250  |      | ns   |

| t <sub>R</sub>       | Line Rise Time             |      | 1    | μs   |

| t <sub>F</sub>       | Line Fall Time             |      | 300  | ns   |

| tsu: sto             | Stop Condition Setup Time  | 4.7  |      | μs   |

The I<sup>2</sup>C-bus timing conforms to this table. However, the I<sup>2</sup>C-bus can operate faster than at the speeds, specified above. Actually, the SCL frequency is up to about 5 MHz. The hold time and setup time in that case must conform to the ratio described in the above table.

## **FUNCTIONAL DESCRIPTION**

### **Analog Unit**

1) Analog input select: Compatible with composite video signals and S-video signals. Input

selection can be switched by register control via the I2C-bus or by

external pins. (See the below chart for pin combinations.)

When the LSI is used in Composite video mode, input clocks or do resetting after setting S-video mode (101), (110) before setting Composite

video mode.

2) Clamp function: An analog clamp and a digital pulse clamp can be used.

Analog clamp

Analog clamp → Digital clamp (hybrid clamp)

Digital clamp

Only the digital clamp can be set as the pedestal clamp.

# Related register MRB[3:2]

3) AGC amp: The AGC function operates depending upon the input level.

Manual gain setting is also possible. This AGC function operates at 2 stages, the analog unit and digital unit. Digital decoded data is output

in conformance with ITU-RBT.601.

Refer to the explanation of M[1] pin (pin 90).

# Related register ADC2[6:4]

4) A/D converter: Two internal 8-bit A/D converters sample at twice the pixel frequency.

(Sampling at the pixel frequency is possible by changing the register

setting.)

# Related register ADC1[2:0]

## List of Analog Input Conditions

| Input Signal       | Control Pin | Register  |           | Input Pin   |           |           |           |        |    |     |  |

|--------------------|-------------|-----------|-----------|-------------|-----------|-----------|-----------|--------|----|-----|--|

|                    | INS[2:0]    | ADC1[2:0] | VIN1      | VIN2        | VIN3      | VIN4      | VIN5      | VIN6   | ON | OFF |  |

| Composite-1 Input* | [000]       | [000]     | Composite |             |           |           |           |        | ON | OFF |  |

| Composite-2 Input  | [001]       | [001]     |           | Composite   |           |           |           |        | ON | OFF |  |

| Composite-3 Input  | [010]       | [010]     |           |             | Composite |           |           |        | ON | OFF |  |

| Composite-4 Input  | [011]       | [011]     |           |             |           | Composite |           |        | ON | OFF |  |

| Composite-5 Input  | [100]       | [100]     |           |             |           |           | Composite |        | ON | OFF |  |

| S-video-1 Input    | [101]       | [101]     | Luminance |             |           |           | Chroma    |        | ON | ON  |  |

| S-video-2 Input    | [110]       | [110]     |           | Luminance   |           |           |           | Chroma | ON | ON  |  |

| All inputs Off     | [111]       | [111]     |           | OFF (Sleep) |           |           |           |        |    |     |  |

Blank spaces: non-selectable, \*: register default setting after LSI reset

M[1] pin setting, 0: external mode, 1: internal register mode

## Manual Gain Control (analog AMP gain)

| Gain Setting Pins | Register  | Set Gain Value                     |

|-------------------|-----------|------------------------------------|

| <b>GAINS[2:0]</b> | ADC2[6:4] | Typ. Value (multiplication factor) |

| [000]             | [000]     | 1.0                                |

| [001]             | [001]     | 1.35                               |

| [010]             | [010]     | 1.75                               |

| [011]             | [011]     | 2.3                                |

| [100]             | [100]     | 3.0                                |

| [101]             | [101]     | 3.8                                |

| [110]             | [110]     | 5.0                                |

| [111]             | [111]     | Undefined                          |

#### **Decoder Unit**

## 1. Prologue Block

The prologue block inputs data and performs Y/C separation.

Data can be input at either the pixel frequency (ITU-RBT.601: 13.5 MHz) or at twice the pixel frequency (ITU-RBT.601: 27 MHz). If input at twice the pixel frequency, data is processed after passing through a decimator circuit to convert it to the pixel frequency. The decimator circuit may be bypassed by changing the register setting, regardless of whether data is input at the normal pixel frequency or at twice the pixel frequency.

If a composite signal (CVBS) is input, the default setting performs Y/C separation using a 2-dimensional adaptive comb filter.

The following operating modes can be selected via the I<sup>2</sup>C-bus. Default settings are indicated by an asterisk (\*). The default state is selected at reset.

1) Video input mode selection (related register MRC[7])

NTSC/PAL auto-select\* (only for ITU-RBT.601)

Dependent upon operating mode selected

When ITU-RBT.601 is selected, the video input mode is automatically set depending upon the number of lines per field.

2) Operating mode selection (related register MRA[3:1])

NTSC ITU-RBT.601 13.5 MHz\*

NTSC Square Pixel 12.272727 MHz

NTSC 4fsc 14.31818 MHz

PAL ITU-RBT.601 13.5 MHz

PAL Square Pixel 14.75 MHz

Even if input at twice the pixel frequency, the internal processing is performed at the pixel frequency.

3) Decimator circuit pass/bypass selection (related register MRC[4])

Pass through decimator circuit\*

Bypass decimator circuit

Compatible only when input at twice the pixel frequency.

4) Y/C separation mode selection (related register MRB[1:0])

Use adaptive comb filter\*

Use non-adaptive comb filter

Do not use comb filter (use trap filter)

The adaptive comb filter for a NTSC signal makes the correlation between up to 3 consecutive lines, and Y/C separation is performed by the 3-line or 2-line comb filter according to the format of correlation.

The adaptive comb filter for a PAL signal makes the correlation between only 2 lines and performs Y/C separation by switching between the 2-line comb filter and trap filter.

At that time, the adaptive transition method is employed in which the filter is gradually switched depending on the level of correlation.

The non-adaptive comb filter performs Y/C separation by removing the luminance component based on the average of preceding and following lines (when there is correlation between 3 lines). (the average of 2 lines in the case of a PAL signal)

When a comb filter is not used, Y/C separation is performed by a trap filter.

If an S-video signal is input, these Y/C separation circuits are bypassed.

The functions of this block only operate when lines are valid as image information. During the V blanking interval, CVBS signals are not processed.

#### 2. Luminance Block

The luminance block removes synchronous signals from signals containing luminance components after Y/C separation. The signals are compensated and then output as luminance signals. Two modes of gain control functions can be selected for the luminance signal output level: AGC (Auto Gain Control) and MGC (Manual Gain Control).

In the AGC mode, luminance level amplification is determined by comparing the SYNC depth with a reference value. The default is 40IRE and can be changed by the register setting. The input has a sync tip clamp.

In the MGC mode, the signal amplification and black level can be changed by register settings. This block can select the follwing operating modes.

1) Selection of luminance level limiter usage (related register LUMC[7])

Do not use\*

Use

When a limiter is used, the luminance level is limited to 16 to 235.

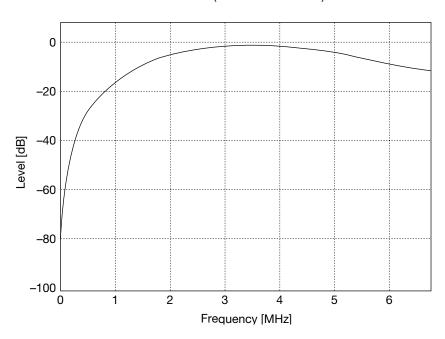

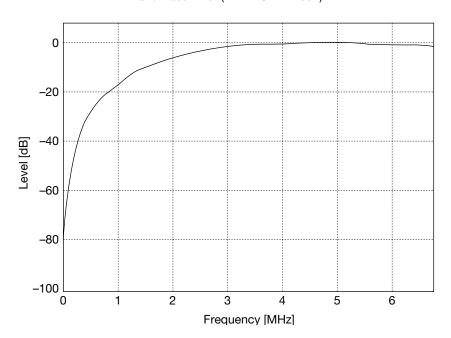

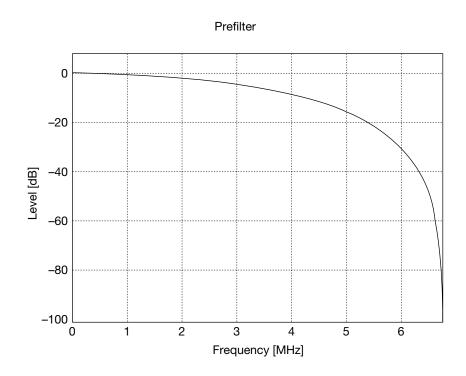

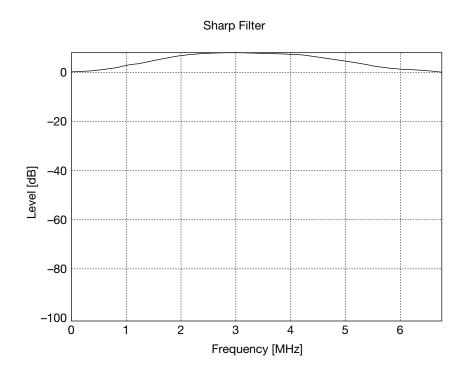

2) Selection of prefilter and sharp filter usage (related register LUMC[6])

Do not use\*

Use

These filters are used to enhance the edges of luminance component signals.

Two filters operate in pairs. For their characteristics, refer to Filter Characteristics described later

3) Selection of aperture bandpass filter coefficient (related register LUMC[5:4])

Middle range\*

High range

4) Coring range selection (related register LUMC[3:2])

Off\*

±4LBS

±5LBS

±7LBS

5) Aperture weighting coefficient selection (related register LUMC[1:0])

0\*

0.25

0.75

1.50

Both coring and aperture compensation processes perform contour compensation.

6) Selection of pixel position compensating circuit usage (related register MRC[6])

Use\*

Do not use

OKI Semiconductor MSM7664

7) AGC loop filter time constant selection (related register AGCLF[7:6])

Slow convergence time 903 ms

Medium 225 ms\*

Fast 56 ms

MGC mode 0

These are designed times from the input gain being rapidly lowered to 50% (–6 dB) of the value at a stable state when normal signals are input till the output being returned to –1 dB (actually these times differ depending on the signal state).

MGC mode: manual gain setting is possible by register AGCLF[5:0]

Set the SSEPL[7] value to a 0 when the MGC mode is used.

- 8) Parameter for fine adjustment of AGC sync depth (related register AGCLF[5:0]) AGC reference level is changed.

- 9) Parameter for fine adjustment of sync removal level (related register SSEPL[6:0])

The black level is adjusted. The default setting outputs the pedestal position as a black level (=16)

- 10) Pedestal clamp selection (related register SSEPL[7])

Do not use pedestal clamp\*

Use pedestal clamp (at this time, AGC does not operate, MGC operates)

#### 3. Chrominance Block

This block processes the chroma signals.

The following operating modes can be selected.

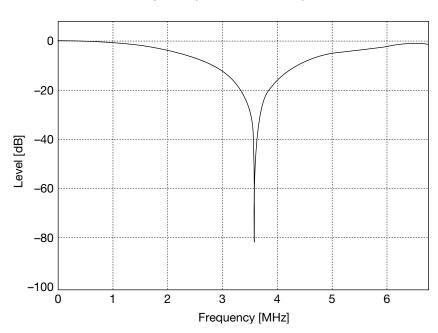

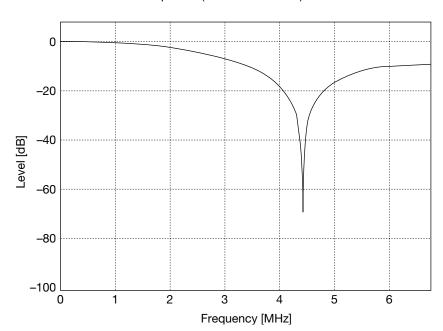

1) Selection of chroma bandpass filter usage (related register CHRC[2])

Do not use\*

Use

2) ACC loop filter time constant selection (related register ACCLF[6:5])

Fast2 convergence time 27 ms

Medium 424 ms\*

Fast 106 ms

MCC mode 0

These are designed times from the input gain being rapidly lowered to 50% (–6 dB) of the value at a stable state when normal signals are input till the output being returned to –1 dB (actually these times differ depending on the signal state).

MCC mode: manual gain setting is possible by register ACCLF[4:0]

3) ACC reference level fine adjustment (related register ACCLF[4:0])

ACC reference level is changed.

4) Parameter for burst level fine adjustment (related register CHRC[1:0])

Threshold level at which chroma amplitude becomes valid is selected based upon color burst ratio.

0.5

0.25\*

0.125

Off

Off: The color killer function is turned off. If decoloration occurs while decoding a still picture, setting the threshold level to "off" will reduce the decoloration.

5) Color killer mode selection (related register MRB[5])

Auto color killer mode\*

Forced color killer

6) Parameter for fine adjustment of color subcarrier phase (related register HUE[7:0]) HUE control function

7) Vertical color filter (related register CHRC[6:4])

Averaging computation is made for the lines before and after the U, V demodulated signal. This is likely to make the image appear smooth.

Using a register, it is possible to select the modes of either to carry out or not carry out the averaging operation based on the correlation between the previous and next lines, or not to carry out the averaging operation at all. In addition, it is also possible to change the level of judging the correlation using a register setting.

In this block, chroma signals pass through a bandpass filter to cut out unnecessary band.

To maintain a constant chroma level, these signals then pass through an ACC compensating circuit and are UV demodulated. (The filter can be bypassed.)

If the demodulated result does not reach a constant level, color killer signals are generated to fix the ACC gain. This functions as an auto color killer control circuit.

The UV demodulated results pass through a low-pass filter and are output as chrominance signals.

## 4. Synchronization Block

This block processes the sync signals. Synchronous signals are generated for chip output and for internal use. Various signals are output from this block and the following operating modes can be selected.

- 1) Adjustment of SYNC threshold level (internal sync) (related register STHR[7:0]) SYNC detection level is set.

- 2) Fine adjustment of HSY (Horizontal Sync Clamp) signal (related registers HSYT[7:4], HSYT[3:0], MRB[3:2])

- 2-1) Fine adjustment of HSY signal (start side)

- 2-2) Fine adjustment of HSY signal (stop side)

The HSY signal provides the sync-tip and clamp timing to the A/D converter.

This signal is used for digital clamp, but can not be observed from outside.

- 3) Fine adjustment of HSYNC\_L signal (related register HSDL[7:0]) HSYNC\_L signal output position is adjusted.

- 4) HVALID control (related registers HVALT[7:4], HVALT[3:0])

- 4-1) Fine adjustment of HVALID signal (start side)

- 4-2) Fine adjustment of HVALID signal (stop side)

Data signals are transferred at the rising edge of the HVALID signal.

- 5) VVALID control (related registers VVALT[7:4], VVALT[3:0])

- 5-1) Fine adjustment of VVALID signal (start side)

- 5-2) Fine adjustment of VVALID signal (stop side)

- 6) FIFO and Field Memory mode selection (related register MRB[7:6])

FIFO-1 mode\*: Sets and outputs a standard value for the number of pixels per 1H from the internal FIFO.

This mode is also compatible (to a degree) with non-standard VTR signals.

FIFO-2 mode: Sets and outputs a constant pixel number corresponding to the input H interval for the number of pixels per 1H from the internal FIFO.

FM-1 mode: This mode outputs the decoded results according to the SYNC signal.

Usage of external field memory is required to manage the number of pixels

and to absorb jitter.

Memory control signals are to be generated externally.

FM-2 mode: This mode is compatible with considerably distorted non-standard VTR

signals. Jitter is absorbed by using external field memory (2 Mb  $\times$  2) and the

standard value is set as the pixel number.

Field memory control signals are output simultaneously from M[7:4].

7) Field memory control signals

If the FM-2 mode uses external field memory (2 Mb  $\times$  2) instead of the internal FIFO, field memory control signals are supplied from pins M[7:4]. At this time, pin M[0] requires to be set to "H".

### 5. Epilogue Block

The Epilogue Block outputs the UV signal from the Chrominance block and the Y signal from the Luminance block in a format based on a signal obtained from the control register setting. This block can select the following modes.

1) Output mode selection (related register MRA[7:6])

1-1) ITU-RBT.656 (SAV, EAV, blank processing)

1-2) \* 8-bit (YCbCr) output (2x pixel clock) synchronization with HSYNC\_L, VSYNC\_L synchronization with HSYNC\_L, VSYNC\_L synchronization with HSYNC\_L, VSYNC\_L synchronization with HSYNC\_L, VSYNC\_L

2) Enable Blue Back display when synchronization fails (related register MRB[4])

OFF

ON\*

3) Selection of YCbCr signal output format (related register MRC[5])

YCbCr 4:2:2\* YCbCr 4:1:1

The chrominance signal (U, V component) outputs Cb and Cr data to the C pin in an output format to be described later.

4) Output pin enable selection (related registers OMR[2], MISC[1:0])

High-impedance

Output enable\*

Pins that become high impedance are determined by setting. See "Output Pin Control Table" described later.

5) Various mode detection (related register OMR[1:0])

NTSC/PAL detection

Multiplex signal detection

HSYNC synchronization detection

Internal FIFO overflow detection

6) Output signal phase control (related registers OPCY[1:0], OPCC[1:0])

Y and C phases can each be adjusted in the range of -2 to +1 pixels.

MSM7664

#### 6. VBID Block

The VBID Block detects AGC, CC, WSS and CGMS data from the input luminance signal and holds them. The VBID module consists of the following four modules.

The detection line and detection level can be changed by setting of the register.

#### 1) AGC module

This module detects whether the macrovision AGC pulse (NTSC/PAL) is included in the specified line. If the AGC pulse has been detected in the specified lines, the flag is set.

NTSC-specified lines: 12 to 19 odd-numbered lines

275 to 282 even-numbered lines

PAL-specified lines: 9 to 18 odd-numbered lines

321 to 330 even-numbered lines

## 2) C.C. (Closed Caption) module

This module detects whether the closed caption data (NTSC/PAL) is included in the specified lines. If it has been detected in the specified lines, character data on the odd number lines and character data on the even number lines are individually held and flags are set for each data separately.

NTSC-specified lines: 21 odd-numbered lines

284 even-numbered lines

PAL-specified lines: 22 odd-numbered lines

3350 even-numbered lines

#### 3) WSS (Wide Screen Signalling) module

This module detects WSS data on the lines specified by NTSC. If it has been detected, the flag is set.

(PAL only)

PAL-specified lines: 23 lines

#### 4) CGMS module

This module detects CGMS data on the lines specified by IEC61880.

If is has been detected, the flag is set (NTSC only)

NTSC-specified lines: 20 odd-numbered lines

283 even-numbered lines

#### 7. I<sup>2</sup>C Control Block

This serial interface block is based on the I<sup>2</sup>C standard of the Phillips Corporation.

The registers at up to subaddress Hex14 are write-only registers and the register at subaddress Hex20 is a read-only register.

The license to use the LSI chip for I<sup>2</sup>C systems is granted on the basis of the I<sup>2</sup>C patent of the Phillips Corporation by purchasing the LSI chip.

#### 8. Test Control Block

This block is used to test the LSI chip. Normally this block is not used.

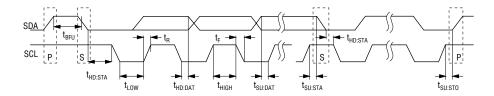

## **Input Signal Level**

The figure below shows the recommended range of the input signal, received in an 8-bit straight binary format.

The above input conditions are ideal. Because analog signals are normally input at different levels, the exact settings described above are difficult to achieve. While maintaining the ratio of White Peak (100%)/SYNC = 100IRE/40IRE (NTSC), if the input signal is set within the A/D converter's voltage range/the Y digital output will be output by digital AGC operation with the pedestal position set at the black level (16) and the white peak position (100%) set at the peak level (235) even if the peak level does not reach 196 (200-4).

## **Output format**

ITU-RBT.656 output, 8-bit (YCbCr) output, and 16-bit (8-bit Y/8-bit CbCr) output have the following formats.

The YCbCr 4:2:2 format and 4:1:1 format are shown below.

The output format can be changed by register settings.

| Output   | F   | Pixel | Byte | Seq | uenc | е   |

|----------|-----|-------|------|-----|------|-----|

| Y7 (MSB) | Y7  | Y7    | Y7   | Y7  | Y7   | Y7  |

| Y6 ` ´   | Y6  | Y6    | Y6   | Y6  | Y6   | Y6  |

| Y5       | Y5  | Y5    | Y5   | Y5  | Y5   | Y5  |

| Y4       | Y4  | Y4    | Y4   | Y4  | Y4   | Y4  |

| Y3       | Y3  | Y3    | Y3   | Y3  | Y3   | Y3  |

| Y2       | Y2  | Y2    | Y2   | Y2  | Y2   | Y2  |

| Y1       | Y1  | Y1    | Y1   | Y1  | Y1   | Y1  |

| Y0 (LSB) | Y0  | Y0    | Y0   | Y0  | Y0   | Y0  |

| C7 (MSB) | Cb7 | Cr7   | Cb7  | Cr7 | Cb7  | Cr7 |

| C6       | Cb6 | Cr6   | Cb6  | Cr6 | Cb6  | Cr6 |

| C5       | Cb5 | Cr5   | Cb5  | Cr5 | Cb5  | Cr5 |

| C4       | Cb4 | Cr4   | Cb4  | Cr4 | Cb4  | Cr4 |

| C3       | Cb3 | Cr3   | Cb3  | Cr3 | Cb3  | Cr3 |

| C2       | Cb2 | Cr2   | Cb2  | Cr2 | Cb2  | Cr2 |

| C1       | Cb1 | Cr1   | Cb1  | Cr1 | Cb1  | Cr1 |

| C0 (LSB) | Cb0 | Cr0   | Cb0  | Cr0 | Cb0  | Cr0 |

| Y point  | 0   | 1     | 2    | 3   | 4    | 5   |

| C point  | 0   |       | 2    | 2   | 4    | 1   |

| Output   |     | Pixel Byte Sequence |     |     |     |     |     |     |  |  |

|----------|-----|---------------------|-----|-----|-----|-----|-----|-----|--|--|

| Y7 (MSB) | Y7  | Y7                  | Y7  | Y7  | Y7  | Y7  | Y7  | Y7  |  |  |

| Y6 `     | Y6  | Y6                  | Y6  | Y6  | Y6  | Y6  | Y6  | Y6  |  |  |

| Y5       | Y5  | Y5                  | Y5  | Y5  | Y5  | Y5  | Y5  | Y5  |  |  |

| Y4       | Y4  | Y4                  | Y4  | Y4  | Y4  | Y4  | Y4  | Y4  |  |  |

| Y3       | Y3  | Y3                  | Y3  | Y3  | Y3  | Y3  | Y3  | Y3  |  |  |

| Y2       | Y2  | Y2                  | Y2  | Y2  | Y2  | Y2  | Y2  | Y2  |  |  |

| Y1       | Y1  | Y1                  | Y1  | Y1  | Y1  | Y1  | Y1  | Y1  |  |  |

| Y0 (LSB) | Y0  | Y0                  | Y0  | Y0  | Y0  | Y0  | Y0  | Y0  |  |  |

| C7 (MSB) | Cb7 | Cb5                 | Cb3 | Cb1 | Cb7 | Cb5 | Cb3 | Cb1 |  |  |

| C6       | Cb6 | Cb4                 | Cb2 | Cb0 | Cb6 | Cb4 | Cb2 | Cb0 |  |  |

| C5       | Cr7 | Cr5                 | Cr3 | Cr1 | Cr7 | Cr5 | Cr3 | Cr1 |  |  |

| C4       | Cr6 | Cr4                 | Cr2 | Cr0 | Cr6 | Cr4 | Cr2 | Cr0 |  |  |

| C3       | 0   | 0                   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| C2       | 0   | 0                   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| C1       | 0   | 0                   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| C0 (LSB) | 0   | 0                   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| Y point  | 0   | 1                   | 2   | 3   | 4   | 5   | 6   | 7   |  |  |

| C point  |     | (                   | )   |     |     | 4   | 4   |     |  |  |

YCbCr 4:2:2 format

YCbCr 4:1:1 format

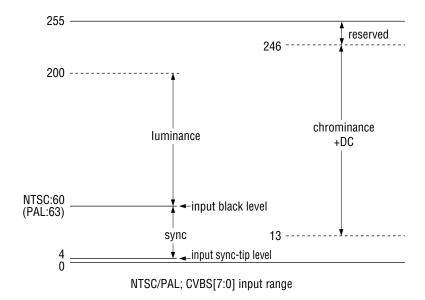

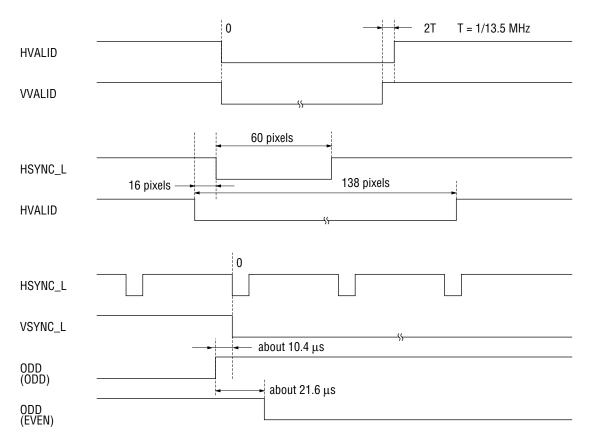

## **TIMING DESCRIPTION**

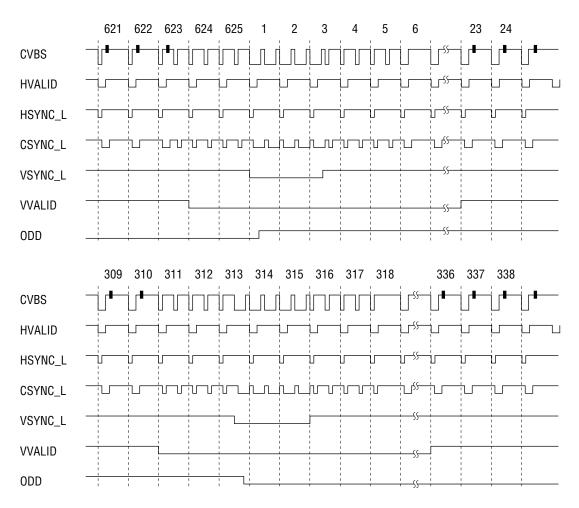

## **Vertical Synchronizing Signal**

The vertical synchronizing signal timing is as follows. The default output is as shown below, but the internal processing of the synchronizing signal is performed before 1H.

**Vertical Synchronizing Signal (60 Hz)**

**Vertical Synchronizing Signal (50 Hz)**

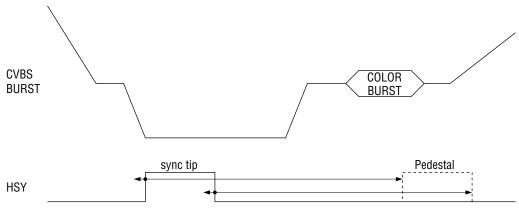

## A/D Converter Support Signal

The waveform of the HSY signal, shown below, provides clamp timing to the A/D converter when HSY clamp (digital clamp) is selected. The start and end edges of the clamp pulse have a variable range from the sync tip to the pedestal position. (HSY is an internal signal.)

A/D Converter Support Signal

## **Output Timing**

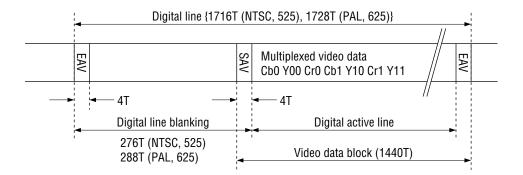

• ITU-RBT.656 output

T : clock periods 37 ns normal (1/27 MHz) SAV: start of active video timing reference code EAV: end of active video timing reference code

ITU-RBT.656 Output (Data in one line in which video data presents)

During the blanking interval, data is output with the Y value.

Note: Digital line 1716T (NTSC, 525) and 1728T (PAL, 625) are not maintained at the next line. Digital active line 1440T of the line immediately after VVALID falls and the 10th or 11th line after VSYNC\_L rises will fluctuate due to pixel compensation. Especially when a non-standard signal is input, the line immediately after VVALID falls will fluctuate largely due to instability of the input signal. Due to phenomena such as an increase in the number of lines for a standard signal and a decrease in the number of lines for a non-standard signal, it may not be possible to guarantee correct EAV and SAV functionality.

#### Contents of SAV and EAV

Both SAV and EAV consist of 4 words. Their configuration is shown below.

| Word   |         |   |   | Bit | No. |    |    |         |                          |

|--------|---------|---|---|-----|-----|----|----|---------|--------------------------|

| word   | 7 (MSB) | 6 | 5 | 4   | 3   | 2  | 1  | 0 (LSB) | F = 0: during field 1    |

| First  | 1       | 1 | 1 | 1   | 1   | 1  | 1  | 1       | 1: during field 2        |

| Second | 0       | 0 | 0 | 0   | 0   | 0  | 0  | 0       | V = 0: elsewhere         |

| Third  | 0       | 0 | 0 | 0   | 0   | 0  | 0  | 0       | 1: during field blanking |

| Fourth | 1       | F | V | Н   | P3  | P2 | P1 | P0      | H = 0: SAV H = 1: EAV    |

P3, P2, P1, P0: Protection bit

### The 4th word of SAV and EAV

The relationship between the F, V, H and Protection bits in the 4th word of SAV and EAV is shown below.

| Bit No.  | 7 (MSB) | 6 | 5 | 4 | 3  | 2  | 1  | 0  |

|----------|---------|---|---|---|----|----|----|----|

| Function | Fixed 1 | F | V | Н | P3 | P2 | P1 | P0 |

| 0        | 1       | 0 | 0 | 0 | 0  | 0  | 0  | 0  |

| 1        | 1       | 0 | 0 | 1 | 1  | 1  | 0  | 1  |

| 2        | 1       | 0 | 1 | 0 | 1  | 0  | 1  | 1  |

| 3        | 1       | 0 | 1 | 1 | 0  | 1  | 1  | 0  |

| 4        | 1       | 1 | 0 | 0 | 0  | 1  | 1  | 1  |

| 5        | 1       | 1 | 0 | 1 | 1  | 0  | 1  | 0  |

| 6        | 1       | 1 | 1 | 0 | 1  | 1  | 0  | 0  |

| 7        | 1       | 1 | 1 | 1 | 0  | 0  | 0  | 1  |

Usually, V = 1 during blanking, however when VBI data is detected and V = 0 is the desired output, set the MRC[3] SAV, EAV V-status of Mode Register C (MRC) to "1".

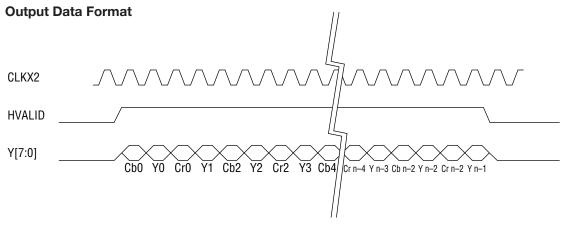

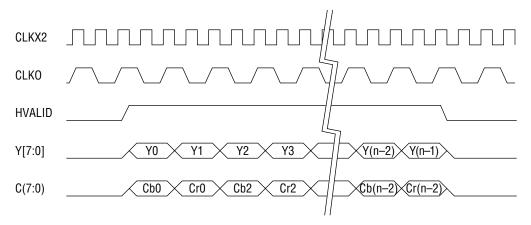

8-bit (YCbCr: 2x clock) Output

16-bit (Y: 8-bit, CbCr: 8-bit) Output

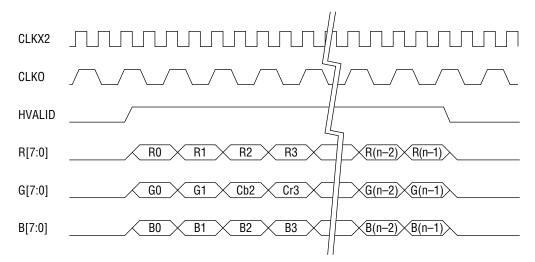

24-bit (R: 8-bit, G: 8-bit, B: 8-bit) Output

Note: When a single-speed clock (13.5 MHz, etc.) is input in 16-bit or 24-bit (RGB) output mode, the waveform of CLKX2 changes to a single speed waveform, but the format after that is not changed.

MSM7664

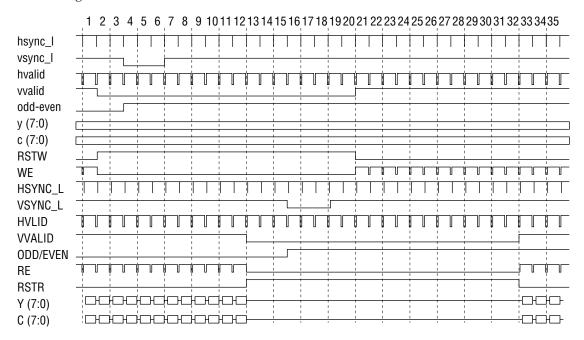

• Timing when using external field memory

Field memory timing in the FM-2 mode, using control signals from the decoder

Field memory: MSM51V8222, 2 units are used (Y and C)

Four memory control signals are supplied from the decoder, M[4]: RSTW, M[5]: RSTR, M[6]:

WE:, and M[7]: RE.

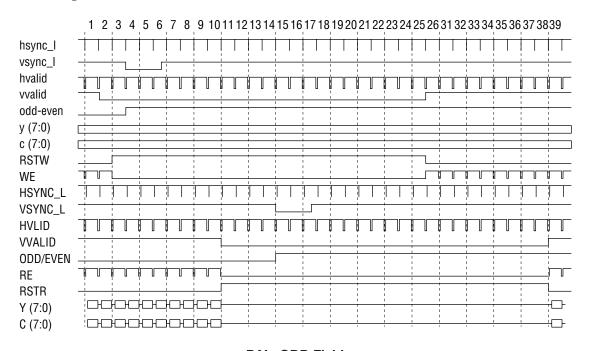

#### NTSC Signal (13.5 MHz)

**NTSC: ODD Field**

**NTSC: EVEN Field**

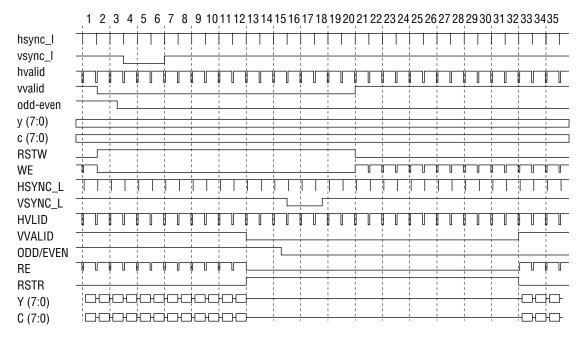

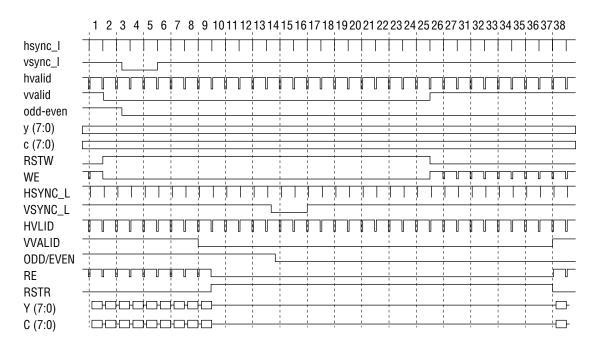

PAL Signal (13.5 MHz)

**PAL: ODD Field**

**PAL: EVEN Field**

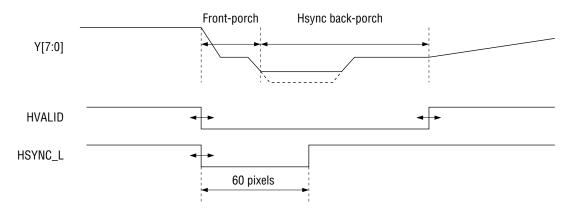

## **Horizontal Synchronizing Signal**

The horizontal synchronizing signal timing is shown below.

**Horizontal Timing**

## Relation between Video Mode and Pixel Number (default settings when standard signal is input)

| Video | Pixel        | Pixel Rate | Total  | Active | Front- | Hsync Back- | HBLK  |

|-------|--------------|------------|--------|--------|--------|-------------|-------|

| Mode  | Туре         | (MHz)      | Pixels | Pixels | Porch  | Porch       | Total |

|       | ITURBT.601   | 13.5       | 858    | 720    | 16     | 122         | 138   |

| NTSC  | Square pixel | 12.272727  | 780    | 640    | 28     | 112         | 140   |

|       | 4fsc         | 14.31818   | 910    | 768    | 8      | 134         | 142   |

| DAI   | ITURBT.601   | 13.5       | 864    | 720    | 12     | 132         | 144   |

| PAL   | Square pixel | 14.75      | 944    | 768    | 34     | 142         | 176   |

## Synchronizing Signal Timing (default timing when standard signal is input)

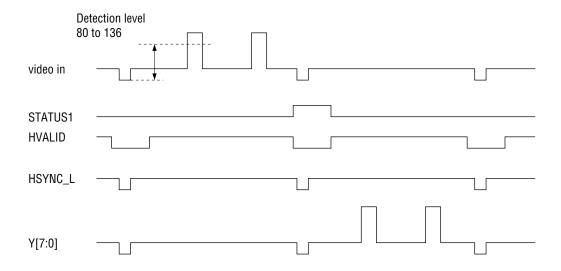

## VBI Data Detection (when a Composite signal is input): STATUS1 Timing

VBI data detection results are output from the STATUS1 pin. Results of individual data detection are read from the register.

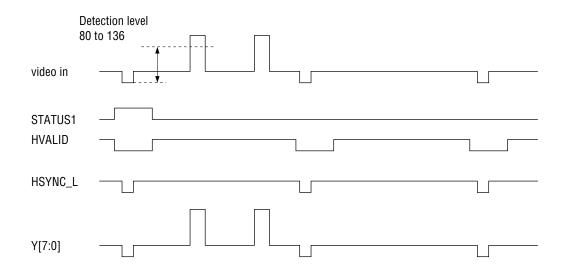

## VBI Data Detection (when an S-Video signal is input): STATUS1 Timing

VBI data detection results are output from the STATUS1 pin. Results of individual data detection are read from the register.

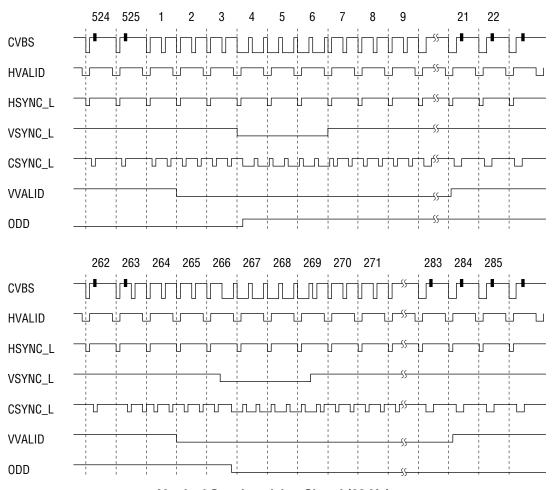

## **I2C BUS FORMAT**

The I<sup>2</sup>C-bus interface input format is shown below.

| Wr           | ite Mode          |    |                 |   |   |               |     |     |         |   |    |

|--------------|-------------------|----|-----------------|---|---|---------------|-----|-----|---------|---|----|

| S            | Slave Address (W) | Α  | Subaddress      | Α |   | Data 0        | Α   |     | Data n  | Α | Р  |

| Rea          | ad Mode           |    |                 |   |   |               |     |     |         |   |    |

| S            | Slave Address (W) | Α  | Subaddress      | Α | S | Slave Address | (R) | ) A | Data 20 |   | A' |

| $\downarrow$ |                   |    |                 |   |   |               |     |     |         |   |    |

|              |                   |    | Data m A' P     |   |   |               |     |     |         |   |    |

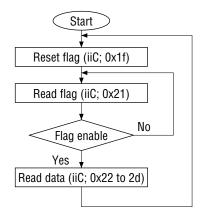

| Rea          | ad Mode 2 (VBID   | RE | AD)             |   |   |               |     |     |         |   |    |

| S            | Slave Address (W) | Α  | Subaddress (1f) | Α |   | Reset Data    |     | А   | Р       |   |    |

| $\downarrow$ |                   |    |                 |   |   |               |     |     |         |   |    |

| S            | Slave Address (W) | Α  | Subaddress (21) | Α | S | Slave Address | (R) | ) A | Data 21 |   | A' |

| $\downarrow$ |                   |    |                 |   |   |               |     |     |         |   |    |

|              |                   |    | А               |   |   | Data m        | Α   | Р   |         |   |    |

Hereafter the above operations are repeated.

| Symbol        | Description                                                                |  |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------|--|--|--|--|--|--|

| S             | Start condition                                                            |  |  |  |  |  |  |

| Clave Address | Slave address 1000001X, 8th bit is write signal ["0"] or read signal ["1"] |  |  |  |  |  |  |

| Slave Address | Slave address is set at M[2] pin (pin 89).                                 |  |  |  |  |  |  |

| A, A'         | Acknowledge. Generated by slave                                            |  |  |  |  |  |  |

| Subaddress    | Subaddress byte                                                            |  |  |  |  |  |  |

| Data n        | Data to write to address designated by subaddress.                         |  |  |  |  |  |  |

| Data m        | Data to read from address designated by subaddress                         |  |  |  |  |  |  |

| Р             | Stop condition                                                             |  |  |  |  |  |  |

As mentioned above, the write/read operation can be executed from subaddress to subaddress continuously. When the write/read operation is executed at subaddresses discontinuously, the Acknowledge and Stop condition formats are input repeatedly after Data 0. Data can be read at subaddress 0x20 only.

The content of read register (VBID-related data) is held unless reset is instructed by the register at address 1f. The input format is shown in "READ MODE2".

The equipment should return an acknowledge signal for read data.

If one of the following matters occurs, the decoder will not return "A" (Acknowledge).

- The slave address does not match.

- A non-existent subaddress is specified.

- The write attribute of a register does not match "X" (read ["1"]/write ["0"] control bit).

The input timing is shown below.

#### **OPERATING MODE SETTING**

There are two types of video mode settings.

- 1. External pin mode: direct setting from dedicated pins

- 2. Register setting mode: specification by internal register settings

These modes can be switched by the mode register MRA[0].

The reset state (default) is the external pin mode.

The following registers can be set in the external pin mode.

MRA[7:6] Output mode 00: ITU-RBT.656 (SAV, EAV, blank processing)

\*01: 8 bit (YCbCr)

HSYNC\_L and VSYNC\_L used for synchronization

10: ITU-RBT.601 16 bit (8 bit Y, 8 bit CbCr)

11: RGB (8 bit R, 8 bit G, 8 bit B)

MRA[3:1] Sampling mode \*000: NTSC ITU-RBT.601 13.5 MHz (27.0 MHz)

001: NTSC Square Pixel

12.272727 MHz (24.545454 MHz)

010: NTSC 4fsc

14.31818 MHz (28.63636 MHz)

100: PAL ITU-RBT.601

13.5 MHz (27.0 MHz)

101: PAL Square Pixel

14.75 MHz (29.5 MHz)

Note: 010: NTSC 4fsc cannot be set externally.

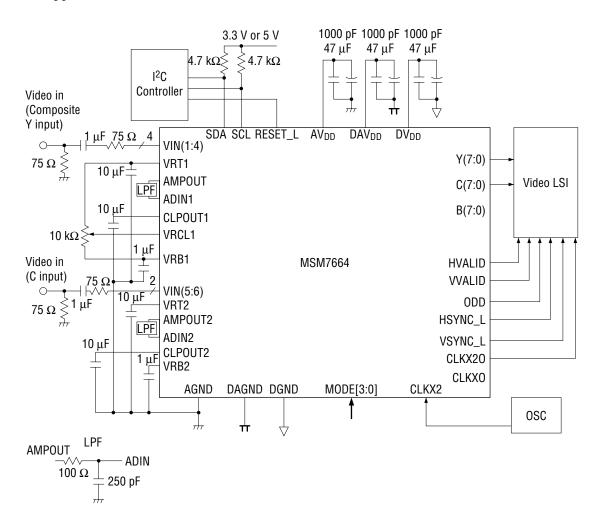

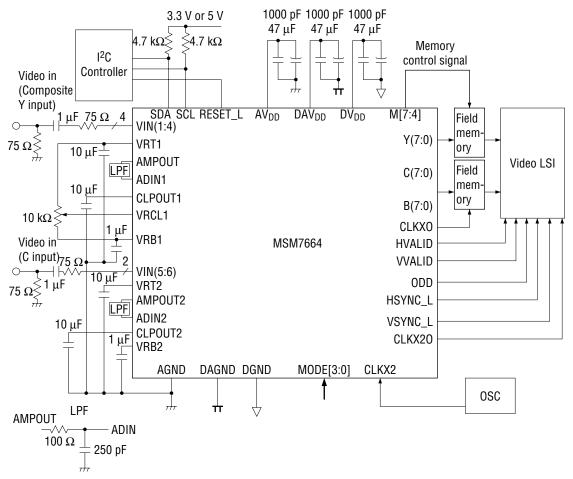

## **Pin Setting Example**

NTSC, 27 MHz (ITU-RBT.601), Composite input, 8-bit (YCbCr) Output

| Pin Name   | Condition | Notes                                             |

|------------|-----------|---------------------------------------------------|

| MODE[3]    | = low     | 0: ITU-RBT.656 01: 8-bit (YCbCr)                  |

| MODE[2]    | = high    | 10:16-bit (Y + CbCr) 11: RGB                      |

| MODE[1]    | = low     | 0: NTSC 1: PAL                                    |

| MODE[0]    | = low     | 0: ITU-RBT.601 1: Square Pixel                    |

| CLKSEL     | = low     | 0 : twice the pixel frequency 1 : pixel frequency |

| PLLSEL     | = low     |                                                   |

| INS[2:0]   | = low     |                                                   |

| GAINS[2:0] | = low     | Normally set to a low level                       |

| TEST[2:0]  | = low     |                                                   |

| SCAN       | = low     |                                                   |

| M[2]       | = low     | : low = 1000001, : high = 1000011                 |

| M[1]       | = low     | Normally act to a low level                       |

| M[0]       | = low     | Normally set to a low level                       |

| SLEEP      | = low     | 0 : normal operation 1 : sleep                    |

# **INTERNAL REGISTERS**

# **Register List**

| Dogistor Function                        | Write    | Sub-    |         |         |         | Data    | byte    |         |         |         |

|------------------------------------------|----------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| Register Function                        | /Read    | address | D7      | D6      | D5      | D4      | D3      | D2      | D1      | D0      |