# **OKI** Semiconductor

This version: Nov. 2001 Previous version: Feb. 1999

# MSM7617

2-Channel Echo Canceler

### **GENERAL DESCRIPTION**

The MSM7617 cancels echoes (acoustic or line echoes) generated in voice channels. It is a low-power CMOS LSI device with two channels.

MSM7617 echo canceling is performed by digital signal processing. It negates echoes by estimating the echo channel and then generating a pseudo-echo signal.

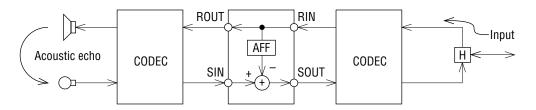

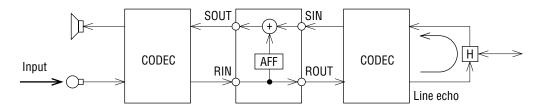

When used as an acoustic echo canceler, the MSM7617 can cancel acoustic echoes between speaker and microphone that occur during hands-free speaking with car phones, conferencing system phones, etc. When used as a line echo canceler, the MSM7617 can cancel line echoes returned by hybrid impedance mismatches.

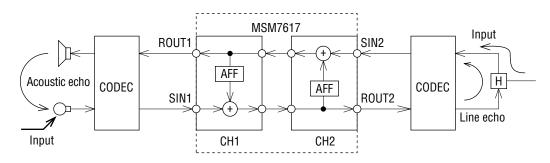

By setting its mode for use as a single cross-connected channel, the MSM7617 can cancel both acoustic and line echoes.

Also, the MSM7617 can improve voice communication by using its howling detection, double-talk detection, attenuation, and gain control functions to prevent and suppress howling levels, and by using its center clipping function to suppress low level noise.

Furthermore, the MSM7617 can disable echo canceling during data communication with its 2100 Hz tone detector and 2100 Hz phase reversal detector. It also provides the ability to attenuate SIN levels, to amplify SOUT levels, and to adjust input/output levels.

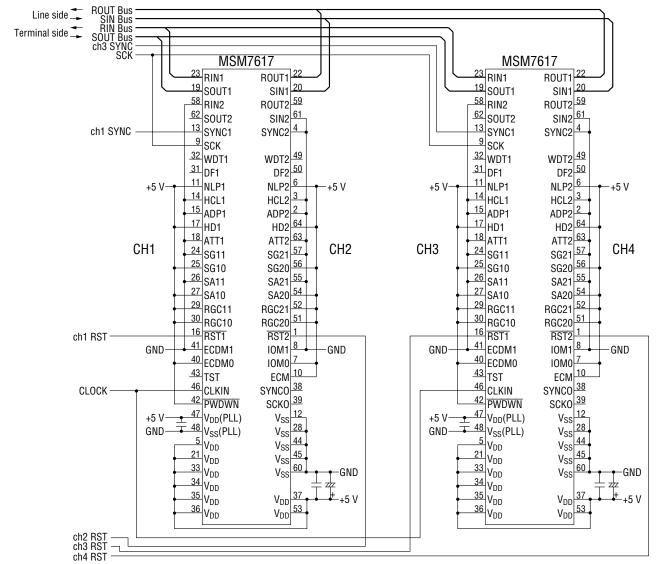

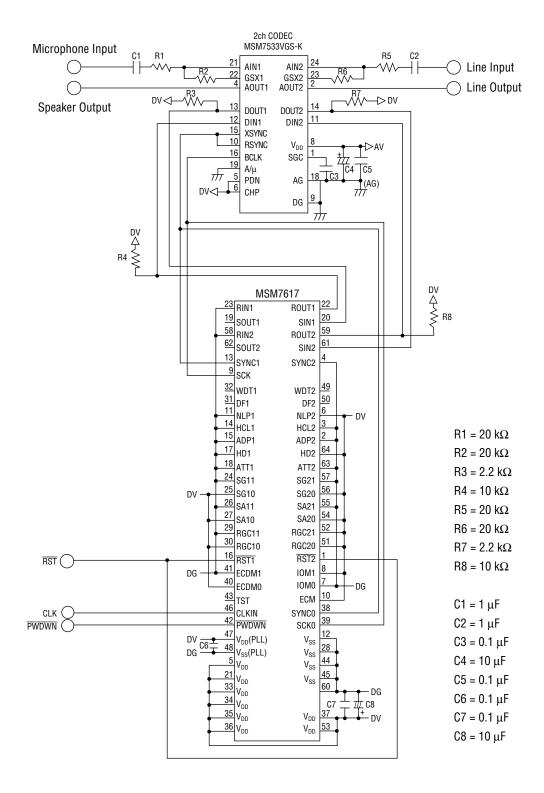

An economical and highly efficient echo canceler unit can be constructed by using a 2-channel single-chip CODEC like the MSM7533 together with the MSM7617.

### **FEATURES**

- Echo canceler has two channels, which can be used for acoustic and line echoes. Set as a single cross-connected channel, it can be used for both acoustic and line echoes.

- •ITU-T G164/G165 standard tone disabler.

- PCM line level adjustment possible with SIN level attenuator (SA pin) and SOUT level amplifier (SG pin). Can also be used for ERL amplification with the SIN level attenuator (SA pin).

- RGC pin provides input/output adjustment mode (±6LR mode) that can prevent malfunction due to excessive inputs without changing the RIN-ROUT input/output levels.

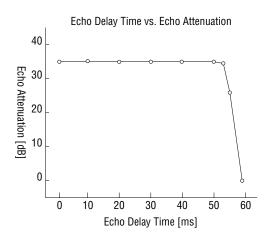

•Cancelable echo delay time: 55 ms (max.)

•Echo attenuation: 30 dB (typ.)

•Clock frequency: 18 to 20 MHz

19.2 MHz if using internal clock signal

•Power supply voltage: 4.5 to 5.5 V

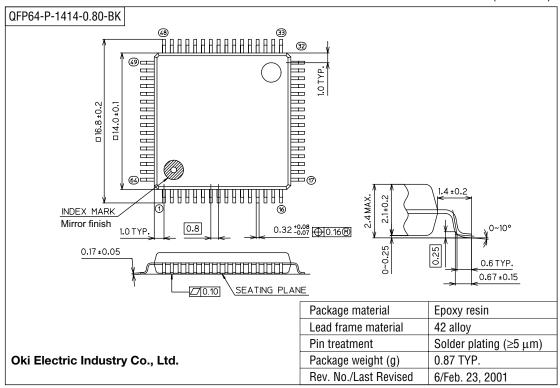

• Package: 64-pin plastic QFP (QFP64-P-1414-0.80-BK)

•Product name: MSM7617-001GS-BK (μ-law)

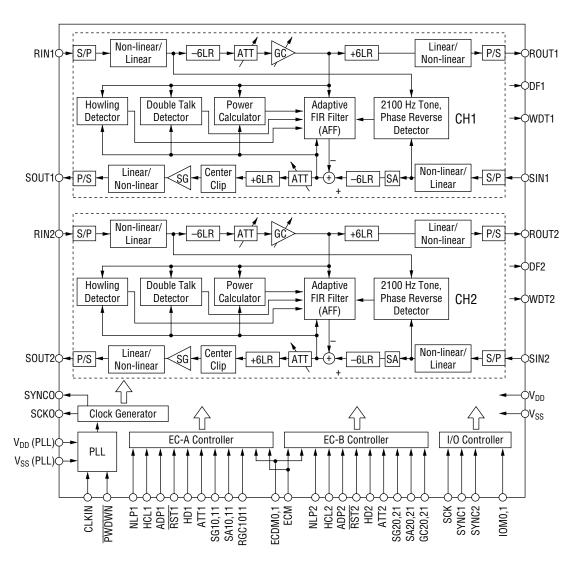

### **BLOCK DIAGRAM**

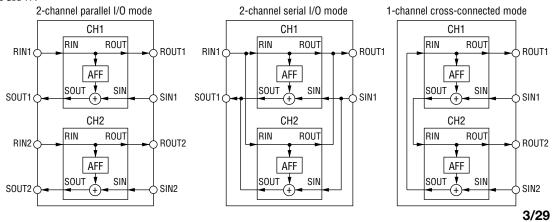

The above diagram shows internal connections for 2-channel parallel mode. The internal connections for 2-channel serial I/O mode and 1-channel cross-connected mode are shown below.

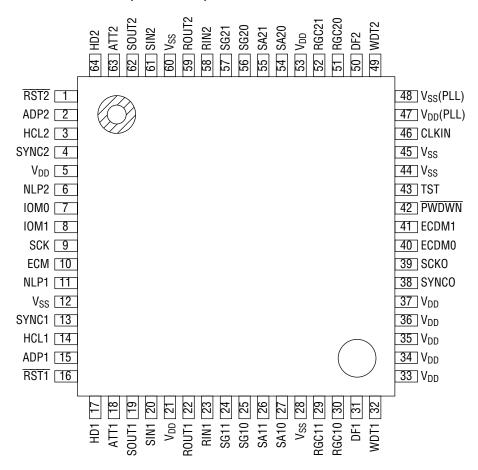

### PIN CONFIGURATION (TOP VIEW)

64-Pin Plastic QFP

### **PIN DESCRIPTIONS**

| Pin | Symbol  | Туре | Description                                                                          |

|-----|---------|------|--------------------------------------------------------------------------------------|

| 1   | RST2    |      | Reset signal input pin for channel 2.                                                |

|     |         |      | "L": Reset                                                                           |

|     |         |      | "H": Normal operation                                                                |

|     |         |      | Input signals are invalid for 100 µs after reset (after RST returns to "H"           |

|     |         |      | from "L") for setting initial values.                                                |

|     |         |      | Input the basic clock during reset. Output pins will be placed in the                |

|     |         |      | following states during reset.                                                       |

|     |         |      | Hi-Z: ROUT2, SOUT2                                                                   |

|     |         |      | No effect: SYNCO, SCKO, ROUT1, SOUT1, DF1, WDT1                                      |

|     |         |      | Previous state: DF2, WDT2                                                            |

|     |         |      | After the power is turned on, initialize the LSI's internal registers by your        |

|     |         |      | execution of $H \rightarrow L$ sequence $1 \mu s$ later than the master clock starts |

|     |         |      | normal oscilation.                                                                   |

|     |         |      | This LSI starts a normal operation by releasing this pin to H after the              |

|     |         |      | H→L sequence above.                                                                  |

|     |         |      | Here, this pin must stay L for 1µs or longer.                                        |

| 2   | ADP2    | I    | AFF coefficient control pin for channel 2.                                           |

|     |         |      | This pin stops coefficient variation of the adaptive FIR filter (AFF), fixing the    |

|     |         |      | coefficients. It allows once acquired AFF coefficients to be saved.                  |

|     |         |      | "H": Fixed coefficient mode                                                          |

|     |         |      | "L": Normal mode (variable coefficients)                                             |

| 3   | HCL2    | I    | Echo canceler disable pin for channel 2.                                             |

|     |         |      | This pin disables the echo canceler and enables data from SIN to SOUT to be outpu    |

|     |         |      | in "through mode". The input and output levels of SIN and SOUT are changed by the    |

|     |         |      | setting of the SG and SA pins; therefore, to output data from SIN to SOUT in         |

|     |         |      | "through mode", set the SA and SG pins to "0 dB".                                    |

|     |         |      | It simultaneously clears the adaptive FIR filter coefficients.                       |

|     |         |      | "H": Disable mode                                                                    |

|     | 0)/8100 |      | "L": Normal mode (echo canceller enabled)                                            |

| 4   | SYNC2   | I    | Sync signal input pin for channel 2 transmit/receive PCM data while in               |

|     |         |      | parallel I/O mode.                                                                   |

|     |         |      | Input the transmit/receive sync signal (8 kHz) of the PCM CODEC connecte             |

|     | NII DO  |      | to channel 2. Input "L" if not in parallel I/O mode.                                 |

| 6   | NLP2    | I    | NLP control pin for channel 2.                                                       |

|     |         |      | This pin controls center clipping, forcing SOUT2 output to the minimum               |

|     |         |      | positive value when it is below –54 dBm0. It is effective for reducing               |

|     |         |      | uncanceled echoes and low-level noise.                                               |

|     |         |      | "H": Center clipping on "L": Center clipping off                                     |

|     |         |      | L. Oditici clipping on                                                               |

| Pin | Symbol | Туре |                                                                                   | Description                                                               |                                                                     |  |  |  |  |  |

|-----|--------|------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|--|

| 7   | IOM0   | ı    | Sets I/0                                                                          | O mode                                                                    | of PCM data.                                                        |  |  |  |  |  |

| 8   | IOM1   |      | IOM1                                                                              | IOM0                                                                      | Mode Setting                                                        |  |  |  |  |  |

|     |        |      | 0                                                                                 | 0                                                                         | 2-channel parallel I/O mode                                         |  |  |  |  |  |

|     |        |      | 0                                                                                 | 1                                                                         | 2-channel serial I/O mode                                           |  |  |  |  |  |

|     |        |      | 1                                                                                 | 0                                                                         | 1-channel cross-connected mode                                      |  |  |  |  |  |

|     |        |      | 1 1 Inhibited                                                                     |                                                                           |                                                                     |  |  |  |  |  |

| 9   | SCK    | I    | Common pin for channel 1 and channel 2. Clock input pin for PCM data              |                                                                           |                                                                     |  |  |  |  |  |

|     |        |      | transmission.                                                                     |                                                                           |                                                                     |  |  |  |  |  |

|     |        |      | Input tl                                                                          | he same                                                                   | clock as the transmit/receive clock of the PCM CODEC.               |  |  |  |  |  |

|     |        |      | Freque                                                                            | ncies be                                                                  | low 128 kHz cannot be used in serial mode.                          |  |  |  |  |  |

| 10  | ECM    | I    | Not use                                                                           | ed. Fix i                                                                 | nput to "H".                                                        |  |  |  |  |  |

| 11  | NLP1   | I    | NLP co                                                                            | ntrol pir                                                                 | n for channel 1.                                                    |  |  |  |  |  |

|     |        |      | This pi                                                                           | n contro                                                                  | ls center clipping, forcing SOUT1 output to the minimum             |  |  |  |  |  |

|     |        |      | positive                                                                          | e value v                                                                 | vhen it is below -54 dBm0. It is effective for reducing             |  |  |  |  |  |

|     |        |      | uncand                                                                            | elled ec                                                                  | hoes and low-level noise.                                           |  |  |  |  |  |

|     |        |      | "H": C                                                                            | Center cl                                                                 | ipping on                                                           |  |  |  |  |  |

|     |        |      | "L": C                                                                            | "L": Center clipping off                                                  |                                                                     |  |  |  |  |  |

| 13  | SYNC1  | I    | Sync si                                                                           | Sync signal input pin for channel 1 transmit/receive PCM data while in 2- |                                                                     |  |  |  |  |  |

|     |        |      | channe                                                                            | channel parallel I/O mode, 2-channel serial I/O mode, or 1-channel cross- |                                                                     |  |  |  |  |  |

|     |        |      |                                                                                   | connected mode.                                                           |                                                                     |  |  |  |  |  |

|     |        |      |                                                                                   | Input the transmit/receive sync signal (8 kHz) of the PCM CODEC.          |                                                                     |  |  |  |  |  |

| 14  | HCL1   | I    |                                                                                   | Echo canceler disable control pin for channel 1.                          |                                                                     |  |  |  |  |  |

|     |        |      |                                                                                   |                                                                           | the echo canceler and enables data from SIN to SOUT to be output    |  |  |  |  |  |

|     |        |      |                                                                                   | -                                                                         | ". The input and output levels of SIN and SOUT are changed by the   |  |  |  |  |  |

|     |        |      | 1                                                                                 |                                                                           | and SA pins; therefore, to output data from SIN to SOUT in "through |  |  |  |  |  |

|     |        |      |                                                                                   |                                                                           | A and SG pins to "0 dB".                                            |  |  |  |  |  |

|     |        |      |                                                                                   |                                                                           | sly clears the adaptive FIR filter coefficients.                    |  |  |  |  |  |

|     |        |      |                                                                                   | "H": Disable mode                                                         |                                                                     |  |  |  |  |  |

|     |        |      |                                                                                   | "L": Normal mode (echo canceler enabled)                                  |                                                                     |  |  |  |  |  |

| 15  | ADP1   | I    | AFF coefficient control pin for channel 1.                                        |                                                                           |                                                                     |  |  |  |  |  |

|     |        |      | This pin stops coefficient variation of the adaptive FIR filter (AFF), fixing the |                                                                           |                                                                     |  |  |  |  |  |

|     |        |      |                                                                                   |                                                                           | allows once acquired AFF coefficients to be saved.                  |  |  |  |  |  |

|     |        |      |                                                                                   |                                                                           | fficient mode                                                       |  |  |  |  |  |

|     |        |      | "L":_N                                                                            | iormal m                                                                  | node (variable coefficients)                                        |  |  |  |  |  |

| Pin | Symbol | Туре | Description                                                                                       |

|-----|--------|------|---------------------------------------------------------------------------------------------------|

| 16  | RST1   | I    | Reset signal input pin for channel 1.                                                             |

|     |        |      | "L": Reset                                                                                        |

|     |        |      | "H": Normal operation                                                                             |

|     |        |      | Input signals are invalid for 100 $\mu s$ after reset (after $\overline{RST}$ returns to "H" from |

|     |        |      | "L") for setting initial values.                                                                  |

|     |        |      | Input the base clock during reset. Output pins will be placed in the following                    |

|     |        |      | states during reset.                                                                              |

|     |        |      | Hi-Z: ROUT1, SOUT1                                                                                |

|     |        |      | No effect: SYNCO, SCKO, ROUT2, SOUT2, DF2, WDT2                                                   |

|     |        |      | Previous state: DF1, WDT1                                                                         |

|     |        |      | After the power is turned on, initialize the LSI's internal registers by your                     |

|     |        |      | execution of $H{ ightarrow}L$ sequence $1\mu s$ later than the master clock starts                |

|     |        |      | normal oscilation.                                                                                |

|     |        |      | This LSI starts a normal operation by releasing this pin to H after the                           |

|     |        |      | H→L sequence above.                                                                               |

|     |        |      | Here, this pin must stay L for 1µs or longer.                                                     |

| 17  | HD1    | I    | Howling detection control pin for channel 1.                                                      |

|     |        |      | This pin controls detection and canceling of howling generated by the                             |

|     |        |      | acoustics of handsfree telephones.                                                                |

|     |        |      | "L": Howling detector on                                                                          |

|     |        |      | "H": Howling detector off                                                                         |

| 18  | ATT1   | I    | ATT control pin for channel 1.                                                                    |

|     |        |      | This pin controls the ATT function for preventing howling with the                                |

|     |        |      | attenuators (ATT) provided on RIN and SOUT. When input is only on RIN,                            |

|     |        |      | the SOUT attenuator is activated. When there is no input on RIN or there is                       |

|     |        |      | input on both SIN and RIN, the RIN input attenuator is activated. Either the                      |

|     |        |      | ATT for the RIN output or the ATT for the SOUT is always activated in all                         |

|     |        |      | cases, and the attenuation of ATT is 6 dB.                                                        |

|     |        |      | "H": Attenuator off                                                                               |

|     |        |      | "L": Attenuator on                                                                                |

|     |        |      | Because the attenuator is inserted opposite the speaker, it is effective for                      |

|     |        |      | further reducing echo.                                                                            |

| 19  | SOUT1  | 0    | PCM data output pin. Output signal changes depending on the setting of                            |

|     |        |      | the IOM pins (refer to the block diagram).                                                        |

|     |        |      | Data is always output on the rising edge of SCK. This pin is put in high                          |

|     |        |      | impedance state while there is no data or during reset.                                           |

|     |        |      | In 2-channel parallel I/O mode, this pin becomes SOUT for channel 1 and                           |

|     |        |      | outputs the PCM signal synchronous with SYNC1. In 2-channel serial I/O                            |

|     |        |      | mode, this pin outputs the SOUT signal as a multiplexed PCM signal of                             |

|     |        |      | SOUT signal for channel 1 and channel 2 synchronous with SYNC1.                                   |

|     |        |      | In 1-channel cross-connected mode, this pin becomes high impedance.                               |

| Pin | Symbol | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20  | SIN1   | ı    | PCM data input pin. Pin use changes depending on the setting of the IOM pins (refer to the block diagram).  In 2-channel parallel I/O mode, this pin becomes SIN for channel 1 and inputs the PCM signal synchronous with SYNC1. In 2-channel serial I/O mode, this pin sequentially inputs SIN as a multiplexed PCM signal from channel 1 and channel 2 synchronous with SYNC1. In 1-channel cross-connected mode, this pin becomes the cross-connected SIN pin for channel 1, and inputs the PCM signal synchronous with SYNC1.  Data is captured on the falling edge of SCK.                                                                                                        |

| 22  | ROUT1  | 0    | PCM data output pin. Output signal changes depending on the setting of the IOM pins (refer to the block diagram).  Data is always output on the rising edge of SCK. This pin becomes high impedance while there is no data or during reset.  In 2-channel parallel I/O mode, this pin becomes ROUT for channel 1 and outputs the PCM signal synchronous with SYNC1. In 2-channel serial I/O mode, this pin outputs the ROUT signal as a multiplexed PCM signal of ROUT signals for channel 1 and channel 2 synchronous with SYNC1.  In 1-channel cross-connected mode, this pin becomes the cross-connected ROUT pin for channel 1, and outputs the PCM signal synchronous with SYNC1. |

| 23  | RIN1   | I    | PCM data input pin. Pin use changes depending on the setting of the IOM pins (refer to the block diagram).  In 2-channel parallel I/O mode, this pin becomes RIN for channel 1 and inputs the PCM signal synchronous with SYNC1. In 2-channel serial I/O mode, this pin sequentially inputs RIN as a multiplexed PCM signal from channel 1 and channel 2 synchronous with SYNC1. In 1-channel cross-connected mode, this pin is not used, and should be fixed at "L".  Data is captured on the falling edge of SCK.                                                                                                                                                                    |

| Pin | Symbol | Туре |                                                                             | Description                                                                 |                                                                |  |  |  |  |

|-----|--------|------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| 24  | SG11   | I    | S outpu                                                                     | ıt gain co                                                                  | ntrol pins for channel 1 (refer to the block diagram).         |  |  |  |  |

| 25  | SG10   |      | These pins amplify the output level of SOUT. The gain level can be set even |                                                                             |                                                                |  |  |  |  |

|     |        |      | during                                                                      | during the echo canceler disable mode.                                      |                                                                |  |  |  |  |

|     |        |      | SG11                                                                        | SG10                                                                        | Gain Level                                                     |  |  |  |  |

|     |        |      | 0                                                                           | 0                                                                           | 0 dB                                                           |  |  |  |  |

|     |        |      | 0                                                                           | 1                                                                           | +6 dB                                                          |  |  |  |  |

|     |        |      | 1                                                                           | 0                                                                           | +12 dB                                                         |  |  |  |  |

|     |        |      | 1                                                                           | 1                                                                           | Not used                                                       |  |  |  |  |

| 26  | SA11   | I    | S input                                                                     | S input attenuator control pins for channel 1 (refer to the block diagram). |                                                                |  |  |  |  |

| 27  | SA10   |      | These p                                                                     | ins atten                                                                   | uate the input level of SIN. Use them if ERL is large.         |  |  |  |  |

|     |        |      | The atte                                                                    | enuation                                                                    | level can be set even during the echo canceler disable mode    |  |  |  |  |

|     |        |      | SA11                                                                        | SA10                                                                        | Attenuation Level                                              |  |  |  |  |

|     |        |      | 0                                                                           | 0                                                                           | 0 dB                                                           |  |  |  |  |

|     |        |      | 0                                                                           | 1                                                                           | −6 dB                                                          |  |  |  |  |

|     |        |      | 1                                                                           | 0                                                                           | −12 dB                                                         |  |  |  |  |

|     |        |      | 1                                                                           | 1                                                                           | Not used                                                       |  |  |  |  |

| 29  | RGC11  | I    | R input                                                                     | R input level control pins for channel 1 (refer to the block diagram).      |                                                                |  |  |  |  |

| 30  | RGC10  |      | Excessi                                                                     | ve input (                                                                  | PCM level is at maximum value) causes a malfanction.           |  |  |  |  |

|     |        |      | Use the                                                                     | se pins w                                                                   | hen there is a possibility of excessive input.                 |  |  |  |  |

|     |        |      | RGC11                                                                       | RGC10                                                                       | Level Control Mode                                             |  |  |  |  |

|     |        |      | 0                                                                           | 0                                                                           | Off                                                            |  |  |  |  |

|     |        |      | 0                                                                           | 1                                                                           | GC: On (control level = -20 dBm0)                              |  |  |  |  |

|     |        |      |                                                                             |                                                                             | By the R gain controller, levels from -20 to -11.5 dBm0 will   |  |  |  |  |

|     |        |      |                                                                             |                                                                             | be suppressed to –20 dBm0 and those above –11.5 dBm0 wil       |  |  |  |  |

|     |        |      |                                                                             |                                                                             | always be attenuated by 8.5 dB. This is effective to prevent   |  |  |  |  |

|     |        |      |                                                                             |                                                                             | excessive input and howling for hands-free applications.       |  |  |  |  |

|     |        |      | 1                                                                           | 0                                                                           | Inhibited                                                      |  |  |  |  |

|     |        |      | 1                                                                           | 1                                                                           | ±6LR: On                                                       |  |  |  |  |

|     |        |      |                                                                             |                                                                             | Applies –6 dB to excessive inputs using the level adjuster     |  |  |  |  |

|     |        |      |                                                                             |                                                                             | provided on R and S I/O. Since +6 dB also is applied at the    |  |  |  |  |

|     |        |      |                                                                             |                                                                             | output, the total level will not change, making this effective |  |  |  |  |

|     |        |      |                                                                             |                                                                             | against line echo.                                             |  |  |  |  |

| Pin | Symbol | Туре |                                                                      |             | Description                                                  |  |  |  |  |

|-----|--------|------|----------------------------------------------------------------------|-------------|--------------------------------------------------------------|--|--|--|--|

| 31  | DF1    | 0    | Tone dis                                                             | abler flag  | output pin for channel 1.                                    |  |  |  |  |

|     |        |      | This pin                                                             | outputs a   | disable flag when the ECDM pins are used for tone disabler   |  |  |  |  |

|     |        |      | mode.                                                                |             |                                                              |  |  |  |  |

|     |        |      | "H": Echo canceler disabled                                          |             |                                                              |  |  |  |  |

|     |        |      | "L": Echo canceler enabled                                           |             |                                                              |  |  |  |  |

| 32  | WDT1   | 0    | Not used                                                             | d. Leave t  | his pin open.                                                |  |  |  |  |

| 38  | SYNCO  | 0    | Output p                                                             | in for inte | rnal SYNC signal (8 kHz).                                    |  |  |  |  |

|     |        |      | This pin                                                             | is used as  | the transmit/receive synchronization signal for PCM signals. |  |  |  |  |

|     |        |      |                                                                      |             | YNC pin and PCM CODEC's synchronization signal pin. Leave    |  |  |  |  |

|     |        |      | this pin                                                             | open if usi | ng an external SYNC.                                         |  |  |  |  |

| 39  | SCKO   | 0    | Output p                                                             | in for inte | rnal SCK signal (256 kHz).                                   |  |  |  |  |

|     |        |      | This pin                                                             | is used fo  | r the transfer clock of PCM signals. Connect it to the PCM   |  |  |  |  |

|     |        |      | CODEC's                                                              | s synchror  | nization signal pin. Leave open if using an external SYNC.   |  |  |  |  |

| 40  | ECDM0  | I    | Tone dis                                                             | sabler cor  | itrol pin common to channel 1 and channel 2.                 |  |  |  |  |

| 41  | ECDM1  |      | These p                                                              | ins detect  | answer tones generated by modems (2100 Hz), and then         |  |  |  |  |

|     |        |      |                                                                      | the echo d  | canceler.                                                    |  |  |  |  |

|     |        |      | ECDM1                                                                | ECDM0       | Tone Disabler Mode                                           |  |  |  |  |

|     |        |      | 0                                                                    | 0           | Off                                                          |  |  |  |  |

|     |        |      | 0                                                                    | 1           | 2100 Hz tone detection: On                                   |  |  |  |  |

|     |        |      | 1                                                                    | 0           | 2100 Hz and phase reversal detection: On                     |  |  |  |  |

|     |        |      | 1                                                                    | 1           | Inhibited                                                    |  |  |  |  |

| 42  | PWDWN  | I    |                                                                      | •           | channel 1 and channel 2.                                     |  |  |  |  |

|     |        |      |                                                                      |             | the power-down mode to reduce current consumption            |  |  |  |  |

|     |        |      |                                                                      |             | s not being used.                                            |  |  |  |  |

|     |        |      |                                                                      | wer dowi    |                                                              |  |  |  |  |

|     |        |      |                                                                      | ormal ope   |                                                              |  |  |  |  |

|     |        |      | During power-down mode all input pins are invalid, and output pins w |             |                                                              |  |  |  |  |

|     |        |      |                                                                      | wing stat   |                                                              |  |  |  |  |

|     |        |      |                                                                      |             | OUT2, ROUT1, ROUT2                                           |  |  |  |  |

|     |        |      |                                                                      | /NCO, SC    |                                                              |  |  |  |  |

|     |        |      |                                                                      |             | F1, WDT1, DF2, WDT2                                          |  |  |  |  |

|     |        |      | Reset th                                                             | ie device a | after power-down mode is released.                           |  |  |  |  |

| Pin | Symbol          | Туре |                                                                        |                                                                               | Description                                             |  |  |  |  |

|-----|-----------------|------|------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|--|

| 43  | TST             | 0    | Not used                                                               | . Leave th                                                                    | nis pin open.                                           |  |  |  |  |

| 46  | CLKIN           | I    | Basic clo                                                              | Basic clock input pin.                                                        |                                                         |  |  |  |  |

|     |                 |      | Input a c                                                              | Input a clock 18 to 20 MHz. Use 19.2 MHz if using internal synchronization $$ |                                                         |  |  |  |  |

|     |                 |      | signals (SYNCO, SCKO).                                                 |                                                                               |                                                         |  |  |  |  |

| 47  | $V_{DD}$        | - 1  | Power s                                                                | upply for                                                                     | PLL circuit that uses the basic clock.                  |  |  |  |  |

|     | (PLL)           |      | Insert a                                                               | 0.1μF cap                                                                     | pacitor with excellent high frequency characteristics   |  |  |  |  |

|     |                 |      | between                                                                | V <sub>DD</sub> (PLL                                                          | .) and V <sub>SS</sub> (PLL).                           |  |  |  |  |

| 48  | V <sub>SS</sub> | I    | Ground                                                                 | for PLL ci                                                                    | rcuit that uses the basic clock.                        |  |  |  |  |

|     | (PLL)           |      | Insert a                                                               | 0.1μF cap                                                                     | acitor with excellent high frequency characteristics    |  |  |  |  |

|     |                 |      | between                                                                | V <sub>DD</sub> (PLL                                                          | .) and V <sub>SS</sub> (PLL).                           |  |  |  |  |

| 49  | WDT2            | 0    | Not used                                                               | d. Leave t                                                                    | this pin open.                                          |  |  |  |  |

| 50  | DF2             | 0    | Tone dis                                                               | abler flag                                                                    | output pin for channel 2.                               |  |  |  |  |

|     |                 |      | This pin                                                               | outputs a                                                                     | disable flag when the ECDM pins are used for tone       |  |  |  |  |

|     |                 |      | disabler.                                                              |                                                                               |                                                         |  |  |  |  |

|     |                 |      |                                                                        | "H": Echo canceler disabled                                                   |                                                         |  |  |  |  |

|     |                 |      |                                                                        |                                                                               | er enabled                                              |  |  |  |  |

| 51  | RGC20           | I    | R input level control pins for channel 2 (refer to the block diagram). |                                                                               |                                                         |  |  |  |  |

| 52  | RGC21           |      |                                                                        |                                                                               | PCM level is at maximum value) causes a malfunction.    |  |  |  |  |

|     |                 |      |                                                                        |                                                                               | nen there is a possibility of excessive input.          |  |  |  |  |

|     |                 |      | RGC21                                                                  | RGC20                                                                         | Level Control Mode                                      |  |  |  |  |

|     |                 |      | 0                                                                      | 0                                                                             | Off                                                     |  |  |  |  |

|     |                 |      | 0                                                                      | 1                                                                             | GC: On (control level = -20 dBm0)                       |  |  |  |  |

|     |                 |      |                                                                        |                                                                               | By the R gain controller, levels from -20 to -11.5 dBm0 |  |  |  |  |

|     |                 |      |                                                                        |                                                                               | will be suppressed to -20 dBm0 and those above -11.5    |  |  |  |  |

|     |                 |      |                                                                        |                                                                               | dBm0 will always be attenuated by 8.5 dB. This is       |  |  |  |  |

|     |                 |      |                                                                        |                                                                               | effective to prevent excessive input and howling for    |  |  |  |  |

|     |                 |      |                                                                        | _                                                                             | hands-free applications.                                |  |  |  |  |

|     |                 |      | 1                                                                      | 0                                                                             | Inhibited                                               |  |  |  |  |

|     |                 |      | 1                                                                      | 1                                                                             | ±6LR: On                                                |  |  |  |  |

|     |                 |      |                                                                        |                                                                               | Apply –6 dB to excessive inputs using the level         |  |  |  |  |

|     |                 |      |                                                                        |                                                                               | adjuster provided on R and S I/O. Since +6 dB also      |  |  |  |  |

|     |                 |      |                                                                        |                                                                               | is applied at the output, the total level will not      |  |  |  |  |

|     |                 |      |                                                                        |                                                                               | change, making this effective against line echo.        |  |  |  |  |

| Pin | Symbol | Туре |                                                                         |                                                                              | Description                                                |  |  |  |

|-----|--------|------|-------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|

| 54  | SA20   | ı    | S input a                                                               | attenuator                                                                   | control pins for channel 2 (refer to the block diagram).   |  |  |  |

| 55  | SA21   |      | These pi                                                                | ns attenu                                                                    | ate the input level of SIN. Use them if ERL is large.      |  |  |  |

|     |        |      | The atte                                                                | The attenuation level can be set even during the echo canceler disable mode. |                                                            |  |  |  |

|     |        |      | SA21                                                                    | SG20                                                                         | Attenuation Level                                          |  |  |  |

|     |        |      | 0                                                                       | 0                                                                            | 0 dB                                                       |  |  |  |

|     |        |      | 0                                                                       | 1                                                                            | −6 dB                                                      |  |  |  |

|     |        |      | 1                                                                       | 0                                                                            | −12 dB                                                     |  |  |  |

|     |        |      | 1                                                                       | 1                                                                            | Not used                                                   |  |  |  |

| 56  | SG20   | I    | S output gain control pins for channel 2 (refer to the block diagram).  |                                                                              |                                                            |  |  |  |

| 57  | SG21   |      | These pi                                                                | ns amplif                                                                    | y the output level of SOUT. The gain level can be set even |  |  |  |

|     |        |      | during th                                                               | ne echo ca                                                                   | anceler disable mode.                                      |  |  |  |

|     |        |      | SG21                                                                    | SG20                                                                         | Gain Level                                                 |  |  |  |

|     |        |      | 0                                                                       | 0                                                                            | 0 dB                                                       |  |  |  |

|     |        |      | 0                                                                       | 1                                                                            | +6 dB                                                      |  |  |  |

|     |        |      | 1                                                                       | 0                                                                            | +12 dB                                                     |  |  |  |

|     |        |      | 1                                                                       | 1                                                                            | Not used                                                   |  |  |  |

| 58  | RIN2   | 1    | PCM data input pin. Pin use changes depending on the setting of the IOM |                                                                              |                                                            |  |  |  |

|     |        |      | pins (ref                                                               | er to the l                                                                  | block diagram).                                            |  |  |  |

|     |        |      | In 2-cha                                                                | nnel para                                                                    | llel I/O mode, this pin becomes RIN for channel 2 and      |  |  |  |

|     |        |      | inputs th                                                               | ne PCM si                                                                    | gnal synchronous with SYNC2. Data is captured on the       |  |  |  |

|     |        |      | falling ed                                                              | dge of SC                                                                    | K. In other modes, this pin is not used, and should be     |  |  |  |

|     |        |      | fixed at '                                                              | fixed at "L".                                                                |                                                            |  |  |  |

| 59  | ROUT2  | 0    | PCM dat                                                                 | a output                                                                     | pin. Output signal changes depending on the setting of     |  |  |  |

|     |        |      | the IOM                                                                 | pins (refe                                                                   | er to the block diagram).                                  |  |  |  |

|     |        |      | Data is a                                                               | ılways ou                                                                    | tput on the rising edge of SCK. This pin becomes high      |  |  |  |

|     |        |      | impedan                                                                 | ice while t                                                                  | there is no data.                                          |  |  |  |

|     |        |      | In 2-cha                                                                | nnel para                                                                    | llel I/O mode, this pin becomes ROUT for channel 2 and     |  |  |  |

|     |        |      |                                                                         |                                                                              | signal synchronous with SYNC2. In 2-channel serial I/O     |  |  |  |

|     |        |      | mode, th                                                                | nis pin is ı                                                                 | not used and should be left open. In 1-channel cross-      |  |  |  |

|     |        |      |                                                                         |                                                                              | this pin becomes the cross-connected ROUT pin for          |  |  |  |

|     |        |      | channel                                                                 | 2, and ou                                                                    | tputs the PCM signal synchronous with SYNC1.               |  |  |  |

| Pin | Symbol | Туре | Description                                                                     |

|-----|--------|------|---------------------------------------------------------------------------------|

| 61  | SIN2   | I    | PCM data input pin. Pin use changes depending on the setting of the IOM         |

|     |        |      | pins (refer to the block diagram). Data is captured on the falling edge of SCK. |

|     |        |      | In 2-channel parallel I/O mode, this pin becomes SIN for channel 2 and          |

|     |        |      | inputs the PCM signal synchronous with SYNC2. In 2-channel serial I/O           |

|     |        |      | mode, this pin is not used and should be fixed at "L". In 1-channel cross-      |

|     |        |      | connected mode, this pin becomes the cross-connected SIN pin for channel        |

|     |        |      | 2, and inputs the PCM signal synchronous with SYNC1.                            |

| 62  | SOUT2  | 0    | PCM data output pin. Output signal changes depending on the setting of          |

|     |        |      | the IOM pins (refer to the block diagram).                                      |

|     |        |      | Data is always output on the rising edge of SCK. This pin becomes high          |

|     |        |      | impedance while there is no data.                                               |

|     |        |      | In 2-channel parallel I/O mode, this pin becomes SOUT for channel 2 and         |

|     |        |      | outputs the PCM signal synchronous with SYNC2. In other modes, this pin         |

|     |        |      | is not used and should be left open.                                            |

| 63  | ATT2   | I    | ATT control pin for channel 2.                                                  |

|     |        |      | This pin controls the ATT function for preventing howling with the              |

|     |        |      | attenuators (ATT) provided on RIN and SOUT. When input is only on RIN,          |

|     |        |      | the SOUT attenuator is activated. When there is no input on SIN or there is     |

|     |        |      | input on both SIN and RIN, the RIN input attenuator is activated. Either the    |

|     |        |      | ATT for the RIN output or the ATT for the SOUT is always activated in all       |

|     |        |      | cases, and the attenuation of ATT is 6 dB.                                      |

|     |        |      | "H": Attenuator off                                                             |

|     |        |      | "L": Attenuator on                                                              |

|     |        |      | Because the attenuator is activated opposite the speaker, it is effective for   |

|     |        |      | further reducing echo.                                                          |

| 64  | HD2    | I    | Howling detection control pin for channel 2.                                    |

|     |        |      | This pin controls detection and canceling of howling generated by the           |

|     |        |      | acoustics of handsfree telephones.                                              |

|     |        |      | "L": Howling detector on                                                        |

|     |        |      | "H": Howling detector off                                                       |

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter            | Symbol           | Condition | Rating                        | Unit |

|----------------------|------------------|-----------|-------------------------------|------|

| Power Supply Voltage | V <sub>DD</sub>  |           | -0.3 to + 7                   | V    |

| Input Voltage        | V <sub>IN</sub>  | Ta = 25°C | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Power Dissipation    | P <sub>D</sub>   |           | 1                             | W    |

| Storage Temperature  | T <sub>STG</sub> | _         | -55 to +150                   | °C   |

### RECOMMENDED OPERATING CONDITIONS

$(V_{DD} = 4.5 \text{ V to } 5.5 \text{ V})$

| Parameter                | Symbol          | Condition | Min. | Тур. | Max.     | Unit |

|--------------------------|-----------------|-----------|------|------|----------|------|

| Power Supply Voltage     | V <sub>DD</sub> | _         | 4.5  | 5    | 5.5      | V    |

| Power Supply Voltage     | V <sub>SS</sub> | _         | _    | 0    | _        | V    |

| High Level Input Voltage | V <sub>IH</sub> | _         | 2.4  | _    | $V_{DD}$ | V    |

| Low Level Input Voltage  | V <sub>IL</sub> | _         | 0    | _    | 0.8      | V    |

| Operating Temperature    | Та              | _         | -40  | +25  | +85      | °C   |

### **ELECTRICAL CHARACTERISTICS**

### **DC Characteristics**

$(V_{DD} = 4.5 \text{ V to } 5.5 \text{ V}, Ta = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                              | Symbol            | Condition                 | Min. | Тур. | Max.     | Unit |

|----------------------------------------|-------------------|---------------------------|------|------|----------|------|

| High Level Output Voltage              | V <sub>OH</sub>   | $I_{OH} = 40 \mu A$       | 4.2  | _    | $V_{DD}$ | V    |

| Low Level Output Voltage               | V <sub>OL</sub>   | $I_{0L} = 1.6 \text{ mA}$ | 0    | _    | 0.4      | V    |

| High Level Input Current               | l <sub>IH</sub>   | $V_{IH} = V_{DD}$         | _    | 0.1  | 10       | μА   |

| Low Level Input Current                | I <sub>IL</sub>   | $V_{IL} = V_{SS}$         | -10  | -0.1 | _        | μА   |

| High Level Output Leakage Current      | I <sub>OZH</sub>  | $V_{OH} = V_{DD}$         | _    | 0.1  | 10       | μА   |

| Low Level Output Leakage Current       | I <sub>OZL</sub>  | $V_{OL} = V_{SS}$         | -10  | -0.1 | _        | μА   |

| Power Supply Current (operation mode)  | I <sub>DDO</sub>  |                           | _    | 80   | 130      | mA   |

| Power Supply Current (power-down mode) | I <sub>DDS</sub>  | PWDWN = "L"               | _    | 0.5  | 2        | mA   |

| Input Capacitance                      | Cı                | _                         | _    | _    | 15       | pF   |

| Output Load Capacitance                | C <sub>LOAD</sub> | <u> </u>                  | _    | _    | 20       | pF   |

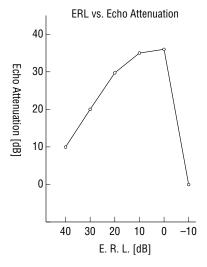

## Echo Canceler Characteristics (refer to characteristics diagram)

| Parameter                                                | Symbol           | Condition                   | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------|------------------|-----------------------------|------|------|------|------|

| Echo Reduction<br>(Common to Channel 1 and<br>Channel 2) |                  | $R_{IN} = -10 \text{ dBm0}$ |      | 30   | _    | dB   |

|                                                          |                  | (5 kHz white noise band)    |      |      |      |      |

|                                                          | L <sub>RES</sub> | E. R. L. = 6 dB             | _    |      |      |      |

|                                                          |                  | $T_D = 50 \text{ ms}$       |      |      |      |      |

|                                                          |                  | ATT, GC, NLP: OFF           |      |      |      |      |

| Cancelable Echo Delay Time                               |                  | R <sub>IN</sub> = −10 dBm0  |      | _    | 55   | ms   |

|                                                          | _                | (5 kHz white noise band)    |      |      |      |      |

| (Common to Channel 1 and                                 | T <sub>D</sub>   | E. R. L. = 6 dB             | _    |      |      |      |

| Channel 2)                                               |                  | ATT, GC, NLP: OFF           |      |      |      |      |

### **Tone Disabler Characteristics**

| Parameter                |                     | Min.                                                          | Тур. | Max. | Unit |  |  |

|--------------------------|---------------------|---------------------------------------------------------------|------|------|------|--|--|

| Tone Detection           | Detection frequency | 2075                                                          | 2100 | 2125 | Hz   |  |  |

|                          | Detection level     | -32                                                           | _    | _    | dBm0 |  |  |

|                          | Detection time      | 380                                                           | _    | _    | ms   |  |  |

| Phase Reversal Detection | Detection condition | 2100Hz. 180° out-of-phase detected before and after 450±25ms. |      |      |      |  |  |

|                          | Detection frequency | 2075                                                          | 2100 | 2125 | Hz   |  |  |

|                          | Detection level     | -32                                                           | _    | _    | dBm0 |  |  |

|                          | Phase reversal      | 135                                                           | 180  | 225  | 0    |  |  |

| Release                  | Detection level     | _                                                             | _    | -32  | dBm0 |  |  |

|                          | Release time        | _                                                             | 250  | _    | ms   |  |  |

### **AC Characteristics**

$(V_{DD} = 4.5 \text{ V to } 5.5 \text{ V}, Ta = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                              | Symbol           | Min.                   | 1                  | Max.                               | Unit  |

|----------------------------------------|------------------|------------------------|--------------------|------------------------------------|-------|

|                                        | Syllibol         | IVIIII.                | Typ.               | IVIAX.                             | Offic |

| Clock Frequency                        | f <sub>C</sub>   |                        | 19.2               | _                                  | MHz   |

| If Used Without Internal Sync Signal   |                  | 18                     |                    | 20                                 |       |

| Clock Cycle Time                       | t <sub>MCK</sub> | _                      | 52.08              |                                    | ns    |

| If Used Without Internal Sync Signal   | -IVIOIC          | 50                     | _                  | 55.56                              |       |

| Clock Duty Cycle                       | t <sub>DMC</sub> | 40                     |                    | 60                                 | %     |

| Clock High Level Pulse Width           | t <sub>MCH</sub> | $t_{MCK} \times 0.4$   | _                  | $t_{MCK} \times 0.6$               | ns    |

| Clock Low Level Pulse Width            | t <sub>MCL</sub> | $t_{MCK}\!\times\!0.4$ |                    | $t_{MCK} \times 0.6$               | ns    |

| Clock Rise Time                        | t <sub>r</sub>   | _                      |                    | 5                                  | ns    |

| Clock Fall Time                        | t <sub>f</sub>   | _                      | _                  | 5                                  | ns    |

| Internal Sync Clock Output Time        | t <sub>DCM</sub> | _                      | _                  | 40                                 | ns    |

| Internal Sync Clock Frequency          | fco              | _                      | 256                | _                                  | kHz   |

| Internal Sync Clock Cycle Time         | t <sub>CO</sub>  | _                      | 3.9                | _                                  | μS    |

| Internal Sync Clock Duty Cycle         | t <sub>DCO</sub> | _                      | 50                 | _                                  | %     |

| Internal Sync Signal Output Time       | t <sub>DCC</sub> | _                      | _                  | 5                                  | ns    |

| Internal Sync Signal Period            | t <sub>CYO</sub> |                        | 125                | _                                  | μs    |

| Internal Sync Signal Pulse Width       | twso             | 1                      | t <sub>CO</sub>    | _                                  | μs    |

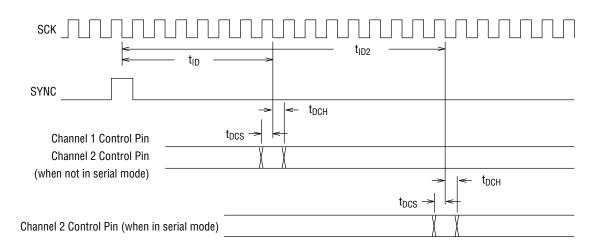

| Transmit/Receive Sync Clock Frequency  | faarr            | 64                     |                    | 2048                               | kHz   |

| In Serial I/O Mode                     | f <sub>SCK</sub> | 128                    | _                  | 2048                               |       |

| Transmit/Receive Sync Clock Cycle Time |                  | 0.488                  | _                  | 15.62                              | μs    |

| In Serial I/O Mode                     | t <sub>SCK</sub> | 0.488                  | _                  | 7.81                               |       |

| Transmit/Receive Sync Clock Duty Cycle | t <sub>DSC</sub> | 40                     | 50                 | 60                                 | %     |

| Transmit/Receive Sync Signal Period    | t <sub>CYC</sub> | _                      | 125                | _                                  | μS    |

| Sync Timing                            | t <sub>XS</sub>  | 45                     | _                  | _                                  | ns    |

|                                        | t <sub>SX</sub>  | 45                     | _                  | _                                  | ns    |

| Sync Signal Width                      | t <sub>WSY</sub> | t <sub>SCK</sub>       | _                  | t <sub>CYC</sub> -t <sub>SCK</sub> | μS    |

| Receive Signal Setup Time              | t <sub>DS</sub>  | 45                     | _                  | _                                  | ns    |

| Receive Signal Hold Time               | t <sub>DH</sub>  | 45                     | _                  | _                                  | ns    |

| Receive Signal Input Time              | t <sub>ID</sub>  | _                      | 7t <sub>SCK</sub>  | _                                  | μS    |

| In 2-Channel Serial Mode               | t <sub>ID2</sub> | _                      | 15t <sub>SCK</sub> | _                                  | μS    |

|                                        |                  |                        |                    |                                    | _     |

# **AC Characteristics (Continued)**

$(V_{DD} = 4.5 \text{ V to } 5.5 \text{ V}, \text{ Ta} = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                    | Symbol           | Min. | Тур. | Max. | Unit |

|------------------------------|------------------|------|------|------|------|

| Serial Output Delay Time     | t <sub>SD</sub>  | _    | _    | 90   | ns   |

|                              | t <sub>XD</sub>  | _    | _    | 90   | ns   |

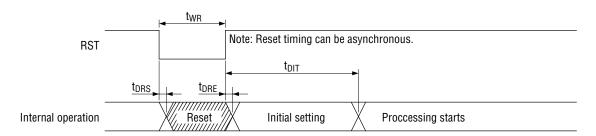

| Reset Signal Input Width     | t <sub>WR</sub>  | 1    | _    | _    | μs   |

| Reset Start Time             | t <sub>DRS</sub> | 5    | _    | _    | ns   |

| Reset End Time               | t <sub>DRE</sub> | _    | _    | 52   | ns   |

| Process Operation Start Time | t <sub>DIT</sub> | 100  | _    | _    | μs   |

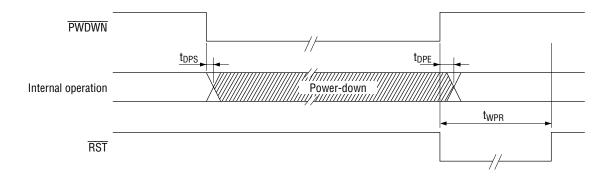

| Power-Down Start Time        | t <sub>DPS</sub> | _    | _    | 111  | ns   |

| Power-Down End Time          | t <sub>DPE</sub> | _    | _    | 15   | ns   |

| RST Width After Power-Down   | t <sub>WPR</sub> | 10   | _    | _    | μS   |

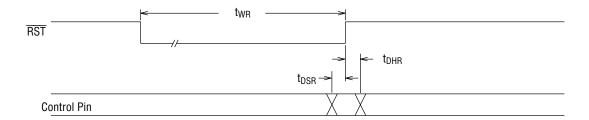

| RST Control Pin Setup Time   | t <sub>DSR</sub> | 20   | _    | _    | ns   |

| RST Control Pin Hold Time    | t <sub>DHR</sub> | 20   | _    | _    | ns   |

| SCK Control Pin Setup Time   | t <sub>DCS</sub> | 120  | _    | _    | ns   |

| SCK Control Pin Hold Time    | t <sub>DCH</sub> | 120  | _    | _    | ns   |

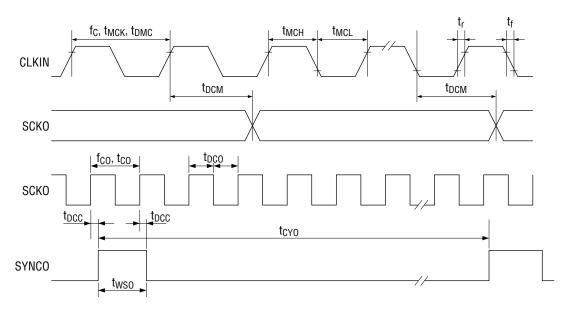

### **TIMING DIAGRAMS**

# **Clock Timing**

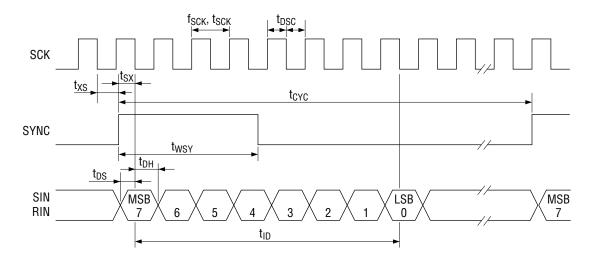

### Serial Data Input Timing (Parallel Mode, FTF Mode)

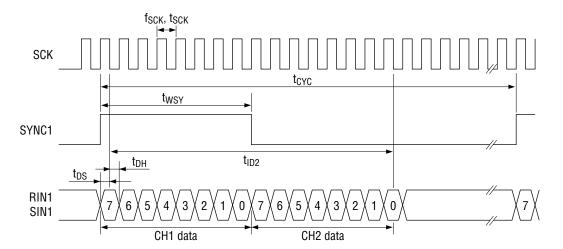

## **Serial Data Input Timing (Serial Mode)**

Note: Refer to parallel mode for detailed timing

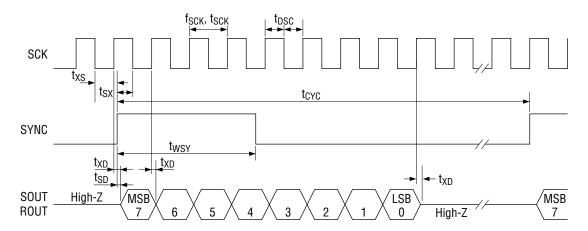

### Serial Data Output Timing (Parallel Mode, FTF Mode)

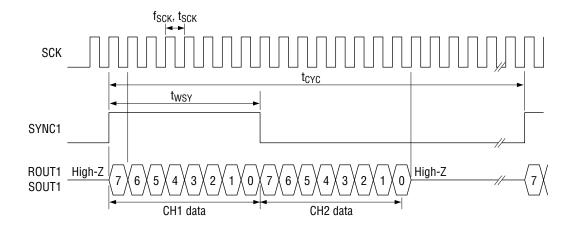

### **Serial Data Output Timing (Serial Mode)**

Note: Refer to parallel mode for detailed timing

### **Operation Timing After Reset**

### **Power-Down Timing**

Note: All inputs are invalid during power-down. Always reset the device after power-down.

### **Capture Timing of Control Pins**

Control pin states are captured during reset and during each period's serial data capture.

### **HOW TO USE THE MSM7617**

The echo canceler cancels the echo on the RIN signal as returned by SIN. Connect the original signal to the R side, and the signal generating the echo to the S side.

### **Connection Methods According to Echoes**

Example 1. Cancel Acoustic Echo (applies to acoustic echo from line input)

Example 2. Cancel Line Echo (applies to line echo from microphone input)

Example 3. Cancel Both Acoustic Echo And Line Echo

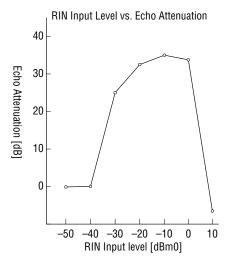

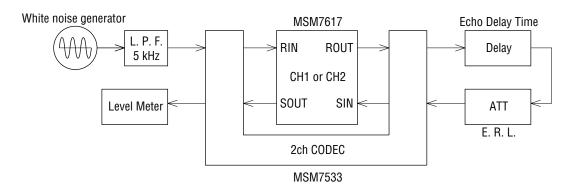

### **ECHO CANCELER CHARACTERISTICS DIAGRAM**

Characteristics of  $\mu$ -law and A-law are identical. (Characteristic graphs below are reference data.)

Measuring Conditions: RIN input level = -10 dBm0 white noise Echo delay time = 50 ms ATT, GC, NLP, LR all off

Measuring Conditions: RIN input = white noise Echo delay time = 50 ms E.R.L. = 6 [dB] ATT, GC, NLP, LR all off

> Measuring Conditions: RIN input level = -10 dBm0 white noise Echo delay time = 50 ms E.R.L = 6 dB ATT, GC, NLP, LR all off

Note: regarding dBm0:

The "dBm0" unit used in the characteristic graphs is a unit that expresses PCM CODEC digital values. Therefore, be aware that the same value 0 [dBm0] might correspond to different analog input levels depending on the PCM CODEC being used. Please check the data sheet of the PCM CODEC being used.

Example MSM7533 0 [dBm0] = 0.85 [Vrms] = 2.4 [Vp-p] = 0.8 [dBm] 600 Ω -10 [dBm0] = 0.27 [Vrms] = 0.76 [Vp-p] = -9.2 [dBm] 600 Ω MSM7543 0 [dBm0] = 0.6007 [Vrms] = 1.7 [Vp-p] = -2.2 [dBm] 600 Ω -10 [dBm0] = 0.19 [Vrms] = 0.54 [Vp-p] = -12.2 [dBm] 600 Ω

# **Measurement System Block Diagram**

### **NOTES ON USE**

1. Set echo return loss (E. R. L) to be attenuated. If the echo return loss is set to be amplified, the echo cannot be canceled. (Refer to the "E. R. L vs Echo Attenuation" characteristic graph.)

When the echo return loss is amplified, adjust the input level to be attenuated by setting the mode with the SA pin. If the level from the SA pin is too low by setting the mode with the SA pin, then amplify the output level by setting the mode with the SG pin.

2. Set RIN input so that there is not excessive input (above 0 dBm0) from the PCM CODEC. Echo cancellation is not possible with excessive input. (Refer to the "RIN vs Echo Attenuation" characteristic graph.)

Recommended input levels are -10 to -20 dBm0. If there is a possibility of excessive input, then set GC mode or 6LR mode with the RGC pins.

- 3. Applying the tone signals to this echo canceler will decrease echo attenuation.

- 4. For changes in the echo path (retransmit, circuit switching during transmission, and so on), convergence may be difficult.

Perform a reset to make it converge.

If the state of the echo path changes after a reset, convergence may again be difficult. In cases such as a change in the echo path, perform a reset each time.