# **OKI** Semiconductor

# This version: Nov. 2001 Previous version: Aug. 1998

# **MSM7584D**

## $\pi$ /4 Shift QPSK MODEM/ADPCM CODEC

#### **GENERAL DESCRIPTION**

The MSM7584D is a CMOS IC developed for use with digital cordless telephones. The device provides a  $\pi/4$  shift QPSK modem function and a CODEC function which performs transcoding between the voice band analog signal and 32 kbps ADPCM data.

The MSM7584C is ideal for use in a handset of the PHS (Personal Handyphone System).

#### **FEATURES**

$(\pi/4 \text{ Shift QPSK Modem})$

- Built-in root Nyquist filter ( $\alpha$  (rolloff rate) = 0.5) for the baseband limiter

- Differential I and Q analog outputs

- The DC offset and gain can be adjusted with respect to the differential I and Q analog outputs

- Completely digitized  $\pi/4$  shift QPSK demodulator system

- Input IF signal frequency of 1.2 MHz or 10.8 MHz is available.

- Built-in A/D converter for RSSI detection

#### (ADPCM CODEC)

- ADPCM: ITU-T Recommendations G.726 (32 kbps)

- Transmit/receive full duplex capability

- PCM interface code format: selectable between μ-law and A-law

- Built-in transmit/receive mute function and transmit/receive programmable gain setting function

- Side tone path formation and level adjustment capabilities

- Built-in DTMF tone and other tones

- Built-in VOX function

- Built-in speech recording/playing interface

- Built-in 150  $\Omega$  driving OP AMP

- Built-in various analog switches

#### (Common)

- Single 3V power supply (V<sub>DD</sub>: 2.7 V to 3.6 V)

- Mode setting through serial interface

- Low power consumption

When the modem unit is operating : 13 mA Typ.  $(V_{DD} = 3.0 \text{ V})$ When the ADPCM CODEC unit is operating : 7 mA Typ.  $(V_{DD} = 3.0 \text{ V})$ When in the power down mode : 0.03 mA Typ.  $(V_{DD} = 3.0 \text{ V})$

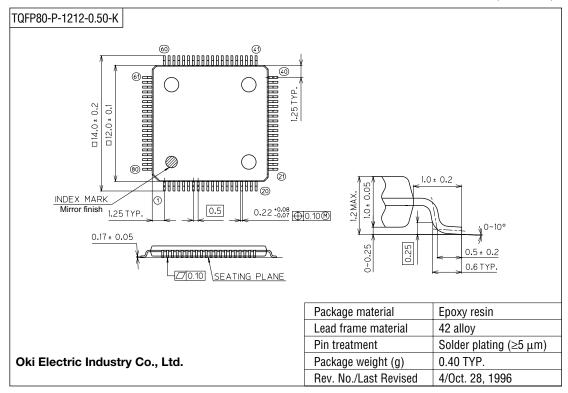

Package:

80-pin plastic TQFP (TQFP80-P-1212-0.50-K) (Product name: MSM7584DTS-K)

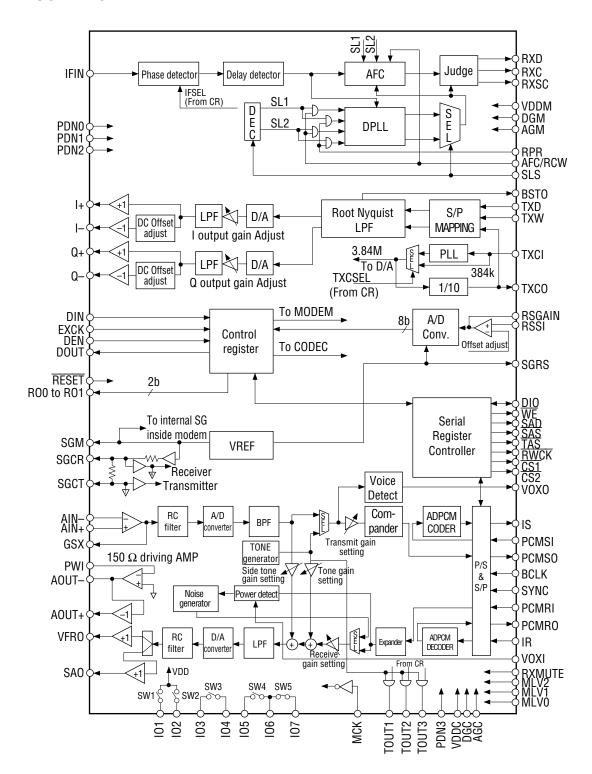

#### **BLOCK DIAGRAM**

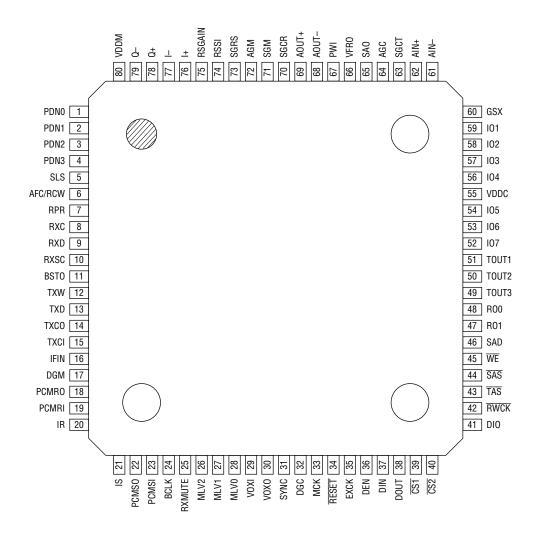

# **PIN CONFIGURATION (TOP VIEW)**

80-Pin Plastic TQFP

# PIN AND FUNCTIONAL DESCRIPTIONS (ADPCM CODEC)

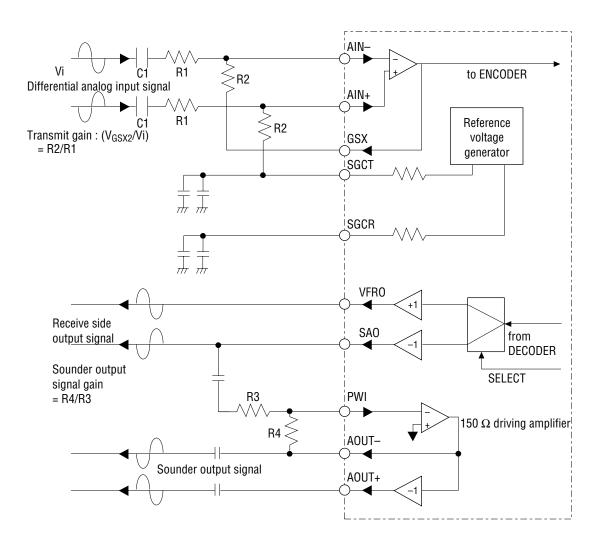

## AIN+, AIN-, GSX

Transmit analog inputs and transmit level adjustment pin.

The AIN– input is connected to the inverting input of the internal transmit amplifier and AIN+ input is connected to the non-inverting input. The GSX pin is connected to the output pin of the amplifier.

See Figure 1 for level adjustment.

## VFRO, SAO

Receive analog output and sounder output.

VFRO is a receive filter output pin and SAO is a sounder output pin. These outputs can directly drive the load of over  $10 \, k\Omega$ . When the system is in the power down mode, these outputs become high impedance.

#### AOUT+, AOUT-, PWI

Input and outputs for internal operation amplifier.

See Figure 1 for connection. When the system is in the power down mode, these outputs become high impedance. The AOUT- and AOUT+ outputs can directly drive the load of over 150  $\Omega$ .

Figure 1 Analog Interface

## SGCT, SGCR

Outputs for CODEC analog signal ground.

The output voltage is approximately 1.4 V. Insert 10  $\mu$ F and 0.1  $\mu$ F bypass capacitors (ceramic type) between these pins and the AG pin. When the device is in power down mode, the output is 0 V.

SGCT is used for transmitting and SGCR is for receiving.

The SG voltage if necessary should be used via a buffer.

#### **AGC**

ADPCM CODEC analog ground (0 V).

#### **DGC**

ADPCM CODEC digital ground (0 V).

Since this pin is internally separated from AGC and AGM (modem ground pin), this pin must be connected to these pins as close as possible on the circuit board.

#### **VDDC**

ADPCM CODEC 3 V power supply.

Connect this pin to the MODEM power Supply VDDM as close as possible on the circuit boards.

#### PDN3

ADPCM CODEC power down control input.

When this pin is set to "0" level, the device enters power down mode.

During normal operation mode, set this pin to "1" level.

The power down mode is controlled by CR0 - B5 of the control register ORed with the signal from the PDN3 pin. Therefore, when using this pin, set CR0 - B5 to digital "0".

**OKI** Semiconductor MSM7584D

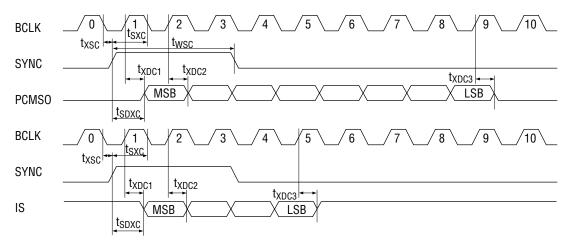

#### **PCMSO**

Transmit PCM data output.

This PCM output signal is output from MSB synchronously with the rising edge of BCLK and SYNC.

#### **PCMSI**

Transmit PCM data input.

This signal is converted to the ADPCM data. The PCM signal is shifted in on the falling edge of BCLK. Normally, this pin is connected to PCMSO.

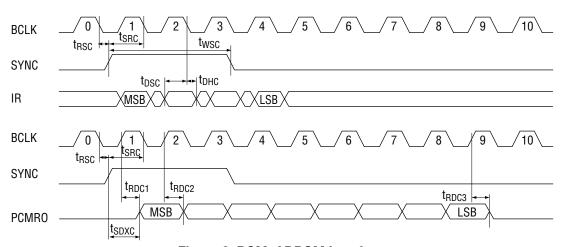

#### **PCMRO**

Receive PCM data output.

The PCM signal is the output signal after ADPCM decoder processing. This signal is serially output from the MSB synchronously with the rising edge of BCLK and SYNC.

#### **PCMRI**

Receive PCM data input.

The PCM input signal is shifted in on the rising edge of BCLK input from MSB. Normally, this pin is connected to PCMRO.

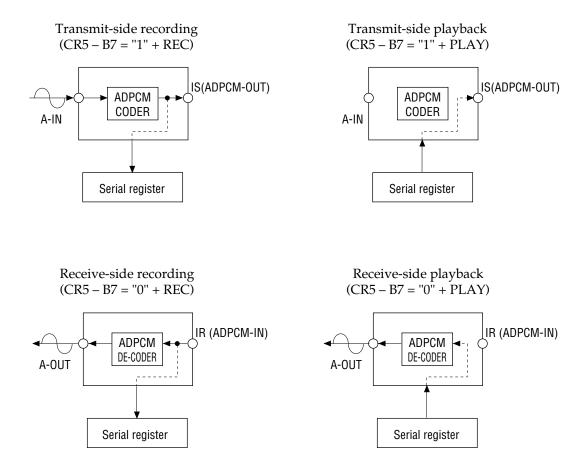

#### IS

Transmit ADPCM signal output.

This signal is the output signal after ADPCM encoding, and is serially output from MSB synchronously with the rising edge of BCLK and SYNC. This pin is an open drain output which requires a pull-up resistor and goes to a high impedence state during power-down mode.

#### **IR**

Receive ADPCM signal input.

Input data is shifted in serially from MSB on the rising edge of BCLK synchronously with SYNC.

#### **BCLK**

Shift clock input for the PCM data (PCMSO, PCMSI, PCMRO, PCMRI) and the ADPCM data (IS, IR).

The frequency ranges from 64 kHz to 2048 kHz.

#### SYNC

8 kHz synchronous signal input for transmit/receive PCM and ADPCM data.

This signal should be synchronous with BCLK. SYNC is used for indicating MSB of the transmit serial PCM and ADPCM data stream.

MSM7584D

## **RXMUTE**

Receive voice path mute control input. When this pin is at "0" level, the device enters normal mode. When at "1" level, the voice level is muted to the value which has been set by MLV2, MLV1, MLV0.

This pin is internally ORed like CR1-B3. Therefore, when using this pin, set CR1-B3 to digital "0".

# MLV2, MLV1, MLV0

Receive voice path mute level setup signals. See the control register map for control method. These signals are internally ORed with CR1-B2, B1, B0, respectively.

Therefore, when using this pin, set these register data to digital "0".

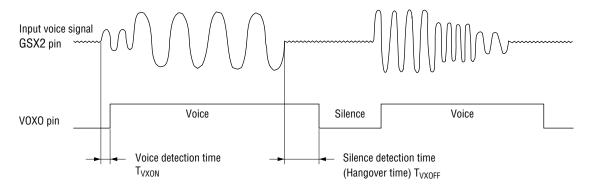

#### VOXO

Transmit VOX function signal output.

VOX function is used to recognize the presence or absence of the transmit voice signal by detecting the signal energy. "1" and "0" levels on this pin correspond to the presence and the absence, respectively. This result also appears at the register CR7 - B7. The signal energy detect threshold is set by the control register data CR6 - B6, B5.

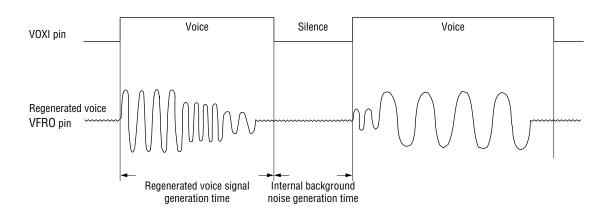

#### VOXI

Signal input for receive VOX function.

The "1" level on VOXI indicates the presence of voice signal, in which case the decoder block processes normal receive signal and the voice signal appears at analog output pins. The "0" level indicates the absence of voice signal, in which case the background noise generated in this device is transferred to the analog output pins. The background noise amplitude is set by the control register CR6. Because this signal is ORed with the register data CR6 - B3, the control register data CR6 - B3 should be set to digital "0".

(a) Transmission Side VOX Function Timing Diagram

(b) Receive Side VOX Function Timing Diagram

Note: The VOXO and VOXI pin function are enabled when CR6 - B7 is set to "1".

Figure 2 VOX Function

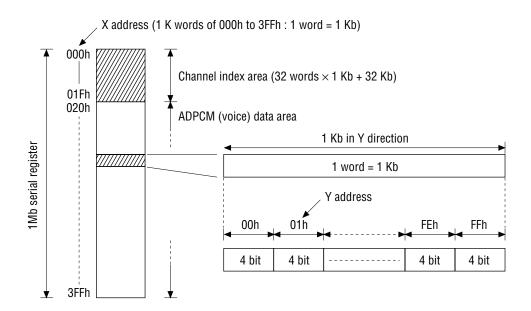

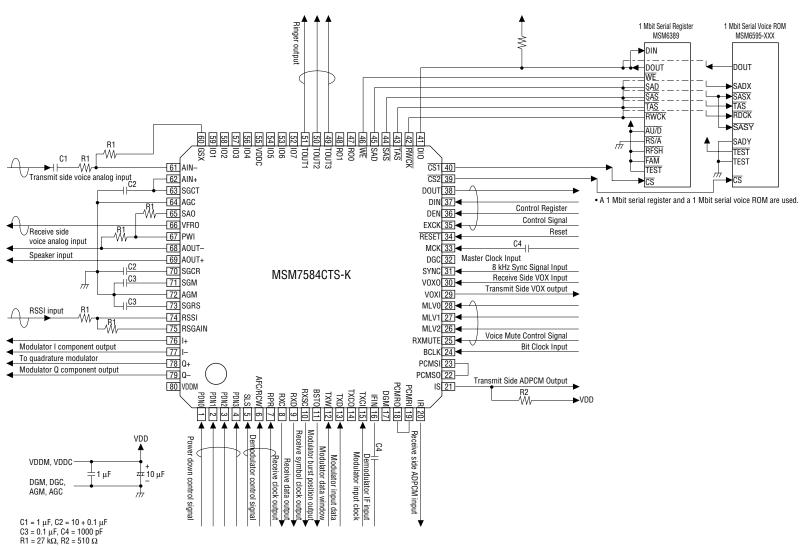

## (Voice Recording Serial Controller)

## DIO

Input/output pin that outputs write data and to input read data.

Connect this pin to the DIN pin, DOUT pin of the serial registers and the DOUT pin of the serial voice ROM. If neither a serial register nor a serial voice ROM is connected, pull this pin up with an approx.  $10 \text{ k}\Omega$  resistor.

## WE

Output that selects the read mode or write mode.

Connect this pin to the  $\overline{\text{WE}}$  pin of the serial registers.

#### SAD

Read/write start address output.

Connect this pin to the SAD pin of the serial registers and the SADX pin of the serial voice ROM.

#### SAS

Output of clocks for writing serial address.

Connect this pin to the  $\overline{SAS}$  pin of the serial registers and the  $\overline{SASX}$  and  $\overline{SASY}$  pins of the serial voice ROM.

#### TAS

Strobe signal output that sets the serial address which is entered from the SAD pin, to the address counter inside the serial register/serial voice ROM.

Connect this pin to the  $\overline{TAS}$  pins of the serial registers and serial voice ROM.

#### **RWCK**

Output of clocks for reading data from or writing data to the serial registers.

Connect this pin to the <u>RWCK</u> pin of the serial registers and the <u>PDCK</u> pin of the serial voice ROM.

## CS1, CS2

Chip select pins.

Connect  $\overline{CS1}$  to the  $\overline{CS}$  pin of the serial registers.

Connect  $\overline{CS2}$  to the  $\overline{CS}$  pin of the serial voice ROM.

#### (Modem)

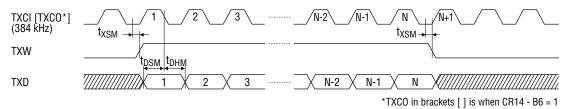

#### **TXD**

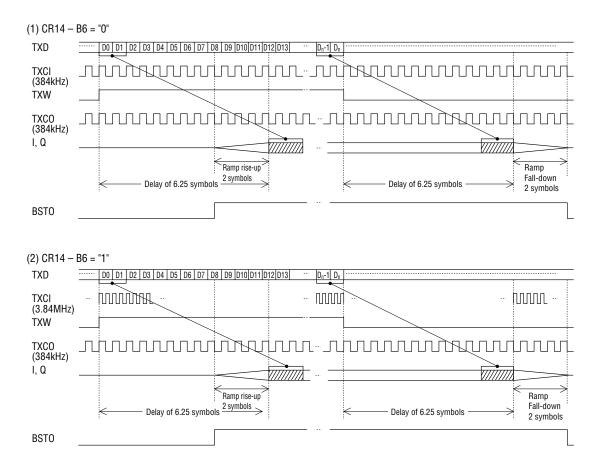

384 kbps transmit data input.

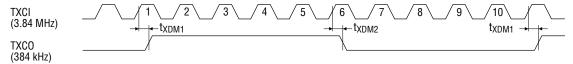

#### **TXCI**

Transmit clock input.

When the control register CR14 - B6 is "0", a 384 kHz clock pulse synchronous with TXD should be input to this pin. This clock pulse should be continuous because this device use APLL to generate an internal clock pulse.

When CR14 - B6 is "1", a 3.84 MHz clock pulse should be input to this pin. When the 3.84 MHz clock pulse is applied, a 384 kHz clock pulse, which is generated by dividing the TXCI by 10, is output to the TXCO pin. The transmit data, synchronous to the 384 kHz clock pulse, should be input to the TXD. In this case the devices do not use APLL, and the 3.84 MHz clock pulse need not be continuous. (Refer to Fig. 3)

#### **TXCO**

Transmit clock output.

When CR14 - B6 is "0", TXCO outputs the 384 kHz clock pulse (APLL output) for monitoring purposes. When CR14 - B6 is "1", this pin outputs a 384 kHz clock pulse generated by dividing the TXCI input by 10. (Refer to Fig. 3)

#### **TXW**

Transmit data window signal input.

The transmit timing signal for the burst data is input to this pin. If TXW is "1", the modulation data is output. (Refer to Fig. 3)

**Figure 3 Transmit Timing Diagram**

MSM7584D

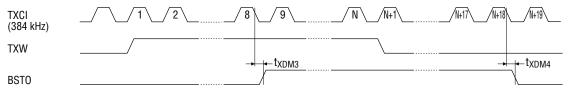

#### **BSTO**

BSTO is the modulator side burst output position specification signal.

The burst time and position of the I and Q analog output including the lamp bits are output. (Refer to Fig. 3)

# I+, I-

Quadrature modulation signal I Component differential analog output.

Their output levels are 500 mV<sub>PP</sub> (maximum) with 1.6 Vdc as the center value. The output pin load conditions are:  $R \ge 10 \,\mathrm{k}\Omega$ ,  $C \le 20 \,\mathrm{pF}$ . The gain of these pins can be adjusted using the control register CR15 - B7 to B4, and the offset voltage at the I– pin can be adjusted using CR16 - B7 to B3.

# Q+, Q-

Quadrature modulation signal Q component differential analog outputs.

Their output levels are 500 mV<sub>PP</sub> (maximum) with 1.6 Vdc as the center value. The output pin load conditions are:  $R \ge 10 \, k\Omega$ ,  $C \le 20 \, pF$ . The gain of these pins can be adjusted using the control register CR15 - B7 to B4, and the offset voltage at the Q– pin can be adjusted by using CR17 - B7 to B3.

#### **SGM**

MODEM internal reference voltage output.

The output voltage value is approximately 2.0 V. Insert a bypass capacitor of approximately 0.1  $\mu F$  between this pin and the AGM pin.

The SG voltage if necessary should be used via a buffer.

MSM7584D

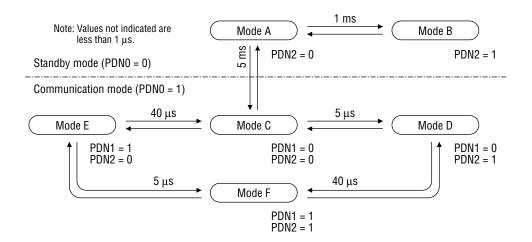

## PDN0, PDN1, PDN2

Various power down controls.

PDN0 controls the standby mode/communication mode; PDN1 controls the modulator; PDN2 controls the demodulator. Refer to Table 1 for details.

**Table 1 Description of Modem Power Down Control**

|                            | PDN0 | PDN2 | PDN1 | Operation State                                                                                                                                                         | Mode Name |

|----------------------------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Standby<br>Mode            | 0    | 0/1  | 0    | Entire system is powered down. The control register is not reset.                                                                                                       | Mode A    |

|                            | 0    | 0/1  | 1    | Modulator unit is powered off. (VREF and PLL also powered off.)  Demodulator unit is powered on.                                                                        | Mode B    |

| Commu-<br>nication<br>Mode | 1    | 0    | 0    | Modulator unit is powered off. (VREF and PLL are powered on.) I and Q outputs are in a high impedance state. Only the demodulator clock regenerator unit is powered on. | Mode C    |

|                            | 1    | 0    | 1    | Modulator unit is powered off. (VREF and PLL are powered on.) I and Q outputs are in a high impedance state. Demodulator unit is powered on.                            | Mode D    |

|                            | 1    | 1    | 0    | Modulator unit is powered on. Only the demodulator clock regenerator unit is powered on.                                                                                | Mode E    |

|                            | 1    | 1    | 1    | Modulator unit is powered on.  Demodulator unit is powered on.                                                                                                          | Mode F    |

#### **VDDM**

+3 V power supply for the modem unit.

Connect this pin to the ADPCM CODEC power supply VDDC on the board.

#### **AGM**

Modem analog signal ground.

#### **DGM**

Modem digital signal ground.

Since this pin is internally separated from AGM, AGC, and DGC, this pin must be connected to theses pins on the board.

#### **MCK**

Master clock input. The clock frequency is 19.2 MHz.

The master clock must always be input to the ADPCM CODEC and MODEM except the device being in power down mode because the both units share the master clock.

If the input level is less than 2 V, the master clock must be input after DC-component is cut by an approx. 1000 pF capacitor. (See the application circuit example.)

#### **IFIN**

Modulated signal input for the demodulator unit.

The CR14 - B4 can select an IF frequency of 1.2 MHz or 10.8 MHz.

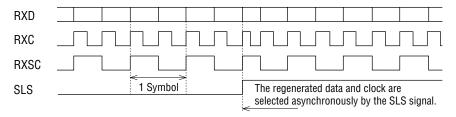

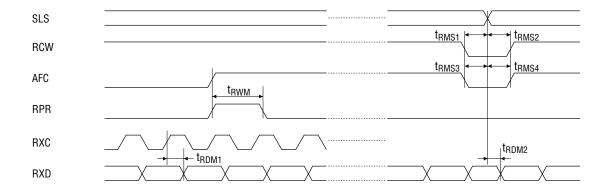

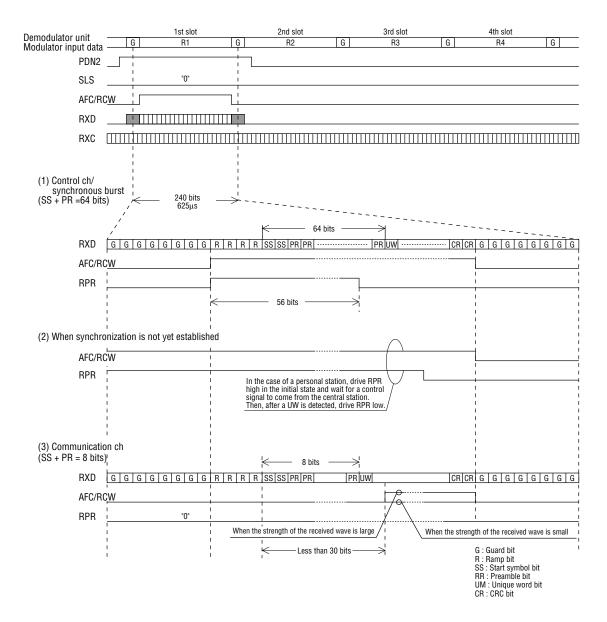

#### RXD, RXC, RXSC

Receive data, receive clock (384 kHz), receive symbol clock (192 kHz) outputs.

When the power is turned on, outputs in which a clock regeneration circuit selected by SLS appear on these output pin.

Figure 4 Timing Diagram of RXD, RXC, and RXSC

#### **SLS**

Receive side operation slot selection signal.

This device has two clock regeneration circuits and two AFC data memory registers. If SLS is at "0" level, slot 1 is selected; if SLS is at "1" level, slot 2 is selected.

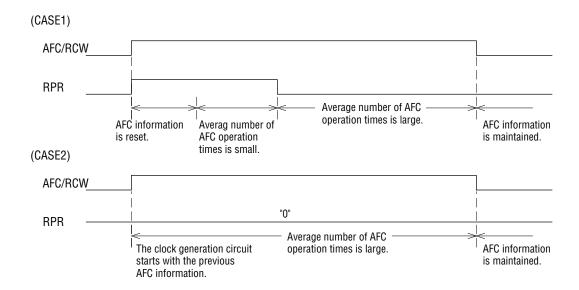

#### **RPR**

High-speed phase clock control signal input for the clock regeneration circuit.

If this pin is at "1" level, the clock regeneration circuit enters the high-speed phase clock mode. When the phase difference is less than a defined value, the circuit shifts to the low-speed phase clock mode automatically. If this pin is at "0" level, the circuit is always in the low-speed phase clock mode.

#### AFC/RCW

AFC operation and clock regeneration range specification signal input.

As shown in Figure 5, AFC information is reset when AFC/RCW and RPR go to "1" level. The AFC operation starts after a certain time elapses.

The average number of AFC operation times is small when RPR is at "1" level.

The average number of AFC operation times is large when RPR is at "0" level.

If AFC/RCW is at "0" level, DPLL will not adjust the phase.

Figure 5 AFC Control Timing Diagram

### (Common)

#### **RESET**

Device reset input.

The control registers CR0 to CR22 all are reset to the initial values by setting this pin to "0" level. The reset width (during "L") should be 200µs or more.

Be sure to initialize all the control registers by executing this RESET to keep this pin to digital "0" level for 200ns or longer after the power is turned on and the  $V_{DD}$  exceeds 2.7V.

#### R0, R1

Output ports for the control register CR21.

The data written in CR21 - B0 and B1 are output on the R0 and R1 pins.

These pins become high impedance when the device is reset.

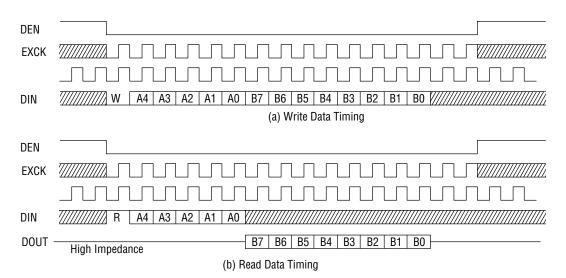

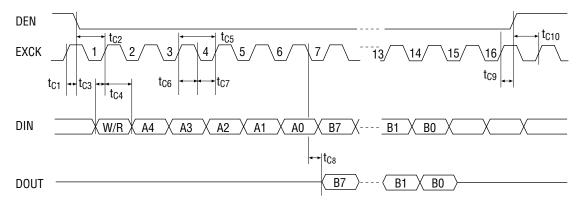

## **DEN, EXCK, DIN DOUT**

Serial control ports for the microcontroller interface.

The device has 23 bytes of control registers. Data is written and read by the external CPU using these ports. DEN is an enable signal input, EXCK is a data shift clock signal input, DIN is an address/data input, and DOUT is a data output.

The input/output timing is shown in Fig. 6.

Figure 6 MCU Interface I/O Timing

The control register map is shown in Table 2.

As shown in Fig. 6, data should be written or read in continuous pulses of the EXCK signal or in 16 bits.

#### 101 to 107

Input/output for internal analog switches.

See the control register map (CR22) and circuit configuration for connection information and control method.

# TOUT1, TOUT2, TOUT3

Sign bit outputs for the tone generator.

The outputs are controlled by the control register CR22. See the control register map and circuit configuration for connection information and control method.

**Table 2 Control Register Map**

| Register |    | Ad | dre       | ss |    |                |                | I              | Data Des       | scription      | 1             |               |               | Register         |

|----------|----|----|-----------|----|----|----------------|----------------|----------------|----------------|----------------|---------------|---------------|---------------|------------------|

| -        | Α4 | АЗ | <b>A2</b> | Α1 | Α0 | В7             | В6             | B5             | B4             | В3             | B2            | B1            | ВО            | function         |

| CR0      | 0  | 0  | 0         | 0  | 0  | Α/μ            | _              | PDN<br>ALL     | _              | _              | SA,VF_<br>OUT | SAO/<br>VFRO  | SA,VF_<br>PDN |                  |

| CR1      | 0  | 0  | 0         | 0  | 1  | TX ON/<br>OFF  | RX ON/<br>OFF  | ADPCM<br>RST   | TX<br>MUTE     | RX<br>MUTE     | MLV2          | MLV1          | MLV0          |                  |

| CR2      | 0  | 0  | 0         | 1  | 0  | TX<br>GAIN3    | TX<br>GAIN2    | TX<br>GAIN1    | TX<br>GAIN0    | RX<br>GAIN3    | RX<br>GAIN2   | RX<br>GAIN1   | RX<br>GAIN0   | ADPCM control    |

| CR3      | 0  | 0  | 0         | 1  | 1  | S_<br>TONE2    | S_<br>TONE1    | S_<br>TONE0    | T ON/<br>OFF   | Tone<br>G3     | Tone<br>G2    | Tone<br>G1    | Tone<br>G0    |                  |

| CR4      | 0  | 0  | 1         | 0  | 0  | DTMF/<br>OT    | TONE_<br>SEND  | TONE5          | TONE4          | TONE3          | TONE2         | TONE1         | TONE0         |                  |

| CR5      | 0  | 0  | 1         | 0  | 1  | SEND/<br>REC   | ROM/<br>SR     | 4M8M/<br>1M    | _              | _              | _             | CMD1          | CMD0          |                  |

| CR6      | 0  | 0  | 1         | 1  | 0  | VOX<br>ON/OFF  | ON<br>LVL1     | ON<br>LVL0     | OFF<br>TIME    | VOX<br>IN      | RX_N<br>SEL   | N_<br>LV1     | N_<br>LV0     |                  |

| CR7      | 0  | 0  | 1         | 1  | 1  | VOX<br>OUT     | Silence<br>L1  | Silence<br>L0  | _              | _              | _             | BUSY          | RPM           |                  |

| CR8      | 0  | 1  | 0         | 0  | 0  | ST0            | ST1            | ST2            | ST3            | ST4            | ST5           | ST6           | ST7           | VOX play         |

| CR9      | 0  | 1  | 0         | 0  | 1  | ST8            | ST9            | ST10           | ST11           | ST12           | _             | _             | _             | mode<br>control  |

| CR10     | 0  | 1  | 0         | 1  | 0  | SPY0           | SPY1           | SPY2           | SPY3           | SPY4           | SPY5          | SPY6          | SPY7          | Control          |

| CR11     | 0  | 1  | 0         | 1  | 1  | SP0            | SP1            | SP2            | SP3            | SP4            | SP5           | SP6           | SP7           |                  |

| CR12     | 0  | 1  | 1         | 0  | 0  | SP8            | SP9            | SP10           | SP11           | SP12           | _             | _             | _             |                  |

| CR13     | 0  | 1  | 1         | 0  | 1  | CH0            | CH1            | CH2            | СНЗ            | CH4            | _             | ADRD          | ADWT          |                  |

| CR14     | 0  | 1  | 1         | 1  | 0  | _              | TXC<br>SEL     | MOD<br>OFF     | IFSEL          |                | _             | _             | _             |                  |

| CR15     | 0  | 1  | 1         | 1  | 1  | Ich<br>GAIN3   | Ich<br>GAIN2   | Ich<br>GAIN1   | Ich<br>GAINO   | Qch<br>GAIN3   | Qch<br>GAIN2  | Qch<br>GAIN1  | Qch<br>GAINO  |                  |

| CR16     | 1  | 0  | 0         | 0  | 0  | Ich<br>Offset4 | Ich<br>Offset3 | Ich<br>Offset2 | Ich<br>Offset1 | Ich<br>Offset0 | _             | _             | _             | MODEM control    |

| CR17     | 1  | 0  | 0         | 0  | 1  | Qch<br>Offset4 | Qch<br>Offset3 | Qch<br>Offset2 | Qch<br>Offset1 | Qch<br>Offset0 | _             | _             | _             |                  |

| CR18     | 1  | 0  | 0         | 1  | 0  | MODEM<br>TEST3 | MODEM<br>TEST2 | MODEM<br>TEST1 | MODEM<br>TEST0 | Local<br>INV1  | Local<br>INV0 | _             | _             |                  |

| CR19     | 1  | 0  | 0         | 1  | 1  | AD07           | AD06           | AD05           | ADO4           | AD03           | AD02          | AD01          | AD00          | RSSI A/D         |

| CR20     | 1  | 0  | 1         | 0  | 0  | AD<br>Offset4  | AD<br>Offset3  | AD<br>Offset2  | AD<br>Offset1  | AD<br>Offset0  | _             | RS<br>PDN     | _             | control          |

| CR21     | 1  | 0  | 1         | 0  | 1  | _              | _              | _              | _              | _              | _             | R01           | R00           | General I/O      |

| CR22     | 1  | 0  | 1         | 1  | 0  | SW1<br>CONT    | SW2<br>CONT    | SW3<br>CONT    | SW4/5<br>CONT  | AOUT<br>PDN    | TOUT3<br>CONT | TOUT2<br>CONT | TOUT1<br>CONT | Switches control |

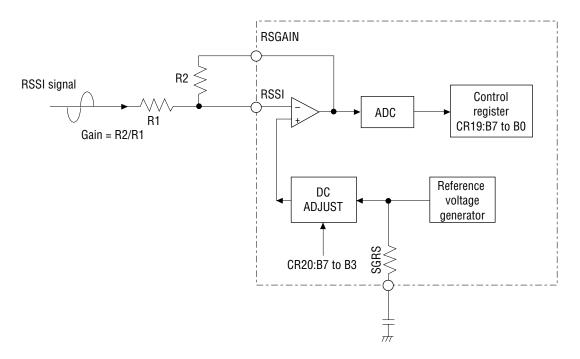

## (RSSI-ADC)

#### **RSSI, RSGAIN**

RSSI input and level adjustment.

RSSI is connected to the inverting input pin of the internal amplifier. RSGAIN is connected to the output pin of the amplifier.

Adjust the gain and DC so that the signal amplitude is between 0.7 V and 2.1 V on the RSGAIN pin. See Fig. 7 for connection.

Gain:

$$A = R2/R1 = 1.4/$$

(Vmax - Vmin)

if  $R1 + R2 \ge 20 \text{ k}\Omega$

DC adjustment value :  $Vadj = A/(1+A) \times ((Vmax + Vmin)/2 - 1.4)$

Set the register CR20 to the DC adjustment value nearest to Vadj.

See the control register map (CR20) for setup values.

#### **SGRS**

Internal reference voltage output for the RSSI - ADC.

The output voltage is 2.0 V. Insert an approx.  $0.1~\mu F$  bypass capacitor between this pin and the AGM pin.

Figure 7 RSSI-ADC Interface

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter             | Symbol           | Condition | Rating                        | Unit |

|-----------------------|------------------|-----------|-------------------------------|------|

| Power Supply Voltage  | V <sub>DD</sub>  | _         | -0.3 to +5                    | V    |

| Analog Input Voltage  | V <sub>AIN</sub> | _         | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Digital Input Voltage | V <sub>DIN</sub> | _         | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Storage Temperature   | T <sub>STG</sub> | _         | −55 to +150                   | °C   |

# **RECOMMENDED OPERATING CONDITIONS**

|            | Parameter                        | Symbol                              | Conditon                         |          | Min.                      | Тур. | Max.                   | Unit |

|------------|----------------------------------|-------------------------------------|----------------------------------|----------|---------------------------|------|------------------------|------|

| Powe       | er Supply Voltage                | $V_{DD}$                            | _                                |          | 2.7                       | _    | 3.6                    | V    |

| Oper       | ating Temperature Range          | Ta                                  |                                  |          | -25                       | +25  | +70                    | °C   |

| High       | Level Input Voltage              | V <sub>IH</sub>                     | Input pins fully digital         |          | 0.45 ×<br>V <sub>DD</sub> | _    | V <sub>DD</sub>        | V    |

| Low        | Level Input Voltage              | V <sub>IL</sub>                     | Input pins fully digital         |          | 0                         | _    | 0.16 × V <sub>DD</sub> | V    |

| Digit      | al Input Rise Time               | t <sub>lr</sub>                     | Input pins fully digital         |          | _                         | _    | 50                     | ns   |

| Digit      | al Input Fall Time               | t <sub>lf</sub>                     | Input pins fully digital         |          | _                         |      | 50                     | ns   |

| Dinit      | al Outrout I and                 | R <sub>DL</sub>                     | IS (Pull-up resistor)            |          | 500                       | _    | _                      | Ω    |

| Digit      | al Output Load                   | C <sub>DL</sub>                     | Input pins fully digital         |          | _                         | _    | 100                    | pF   |

| Вура       | ss Capacitor for SG              | C <sub>SG1</sub>                    | Between SGCT/R and A             | GC       | 10 + 0.1                  | _    | _                      | μF   |

| Вура       | ss Capacitor for SG              | C <sub>SG2</sub>                    | Between SGM, AGM ar<br>AGM       | nd SGRS, | 0.1                       | _    | _                      | μF   |

| Mast       | er Clock Frequency               | F <sub>MCK</sub>                    | MCK                              |          | _                         | 19.2 | _                      | MHz  |

| Mast       | er Clock Duty Ratio              | D <sub>MCK</sub>                    | MCK                              |          | 40                        | 50   | 60                     | %    |

|            | Modulator Side Input             | F <sub>TXC1</sub>                   | TXCI (When CR14 - B6             | i = "0") | _                         | 384  | _                      | kHz  |

| ⊭          | Frequency                        | F <sub>TXC2</sub>                   | TXCI (When CR14 - B6             | i = "1") | _                         | 3.84 | _                      | MHz  |

| 'n         | Clock Duty Ratio                 | D <sub>CKM</sub>                    | TXCI, EXCK                       |          | 40                        | 50   | 60                     | %    |

| Modem Unit | IF Input Duty Ratio              | D <sub>CIF</sub>                    | IFIN                             |          | 45                        | 50   | 55                     | %    |

| Ĭ          | Transmit Sync Pulse              | t <sub>XSM</sub> , t <sub>SXM</sub> | $TXCI \leftrightarrow TXW$       | Fig 10   | _                         | _    | 200                    | ns   |

|            | Setting Time                     | t <sub>DSM</sub> , t <sub>DHM</sub> | $TXCI {\longleftrightarrow} TXD$ | Fig.10   | _                         |      | 200                    | ns   |

|            | Bit Clock Frequency              | F <sub>BCK</sub>                    | BCLK                             |          | 64                        |      | 2048                   | kHz  |

|            | Synchronous Signal Frequency     | F <sub>SYNC</sub>                   | SYNC, SYNC                       |          | _                         | 8.0  | _                      | kHz  |

| ⊭          | Clock Duty Ratio                 | D <sub>CKC</sub>                    | BCLK, EXCK                       |          | 40                        | 50   | 60                     | %    |

| n C        | Transmit Sync Pulse Setting Time | t <sub>XSC,</sub> t <sub>SXC</sub>  | BCLK↔SYNC                        |          | 100                       | _    | _                      | ns   |

| CODEC Unit | Receive Sync Pulse Setting Time  | t <sub>RSC,</sub> t <sub>SRC</sub>  | BCLK↔SYNC                        |          | 100                       |      |                        | ns   |

| 2          | Synchronous Signal Width         | t <sub>WSC</sub>                    | XSYNC, SYNC                      | Fig.8    | 1 BCLK                    | _    | 125μs-1BCLK            | μs   |

|            | PCM, ADPCM Setup Time            | t <sub>DSC</sub>                    | _                                |          | 100                       | _    | _                      | ns   |

|            | PCM, ADPCM Hold Time             | t <sub>DHC</sub>                    |                                  |          | 100                       | _    | _                      | ns   |

# **ELECTRICAL CHARACTERISTICS**

## **DC Characteristics**

|                                          |                   | (*DL                                                                        | -                   |      |          |      |

|------------------------------------------|-------------------|-----------------------------------------------------------------------------|---------------------|------|----------|------|

| Parameter                                | Symbol            | Condition                                                                   | Min.                | Тур. | Max.     | Unit |

|                                          | I <sub>DD1</sub>  | Mode A (When V <sub>DD</sub> = 3.0 V)                                       | _                   | 0.03 | 0.1      | mA   |

| Power Supply Current (Modem)             | $I_{DD2}$         | Mode B (When V <sub>DD</sub> = 3.0 V)                                       | _                   | 4.5  | 10.0     | mA   |

| (When CODEC is in a                      | $I_{DD3}$         | Mode C (When V <sub>DD</sub> = 3.0 V)                                       | _                   | 4.5  | 10.0     | mA   |

| Power Down State)                        | $I_{DD4}$         | Mode D (When $V_{DD} = 3.0 \text{ V}$ )                                     | _                   | 10.5 | 22.0     | mA   |

| 1 ovor bown outer,                       | $I_{DD5}$         | Mode E (When V <sub>DD</sub> = 3.0 V)                                       | _                   | 8.5  | 18.0     | mA   |

|                                          | I <sub>DD6</sub>  | Mode F (When V <sub>DD</sub> = 3.0 V)                                       | _                   | 13.0 | 27.0     | mA   |

| D (00DE0)                                | I <sub>DD7</sub>  | When operating*                                                             | _                   | 7.0  | 15.0     | mA   |

| Power Supply Current (CODEC)             | $I_{DD8}$         | (When no signal, and $V_{DD} = 3.0 \text{ V}$ )                             | _                   | 11.0 | 18.0     | mA   |

| (When Modem is in a Power<br>Down State) | I <sub>DD9</sub>  | When powered down (When $V_{DD} = 3.0 \text{ V}$ )                          | _                   | 0.03 | 0.1      | mA   |

| Power Supply Current (RSSI-ADC)          | I <sub>DD10</sub> | CR22-B3 = "1"<br>(When V <sub>DD</sub> = 3.0 V)                             | _                   | 2.0  | 4.0      | mA   |

| Input Leakage Current                    | I <sub>IH</sub>   | $V_I = V_{DD}$                                                              | _                   | _    | 2.0      | μΑ   |

| IIIput Leakaye Guireiit                  | I <sub>IL</sub>   | V <sub>I</sub> = 0 V                                                        | _                   | _    | 0.5      | μΑ   |

| High Level Output Voltage                | V <sub>OH1</sub>  | I <sub>OH</sub> = 0.4 mA                                                    | $0.5 \times V_{DD}$ | _    | $V_{DD}$ | V    |

| Thigh Level Output voltage               | V <sub>OH2</sub>  | I <sub>OH</sub> = 1 μA                                                      | $0.8 \times V_{DD}$ | _    | $V_{DD}$ | V    |

| Low Level Output Voltage                 | V <sub>OL</sub>   | $I_{OL} = -1.2 \text{ mA}$ (IS pin is pulled up with 500 $\Omega$ resistor) | 0                   | 0.2  | 0.4      | V    |

| Output Leakage Current                   | I <sub>0</sub>    | IS pin                                                                      | _                   | _    | 10       | μΑ   |

| Input Capacitance                        | C <sub>IN</sub>   | _                                                                           | _                   | 5    |          | pF   |

<sup>\*</sup>  $I_{DD7}$  applies when CRC0 - B0 = "0" and CR22 - B3 = "0";  $I_{DD8}$  applies when operating in other conditions.

## **Analog Interface Characteristics (RSSI - ADC)**

$(V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}, \text{ Ta} = -25^{\circ}\text{C to } +70^{\circ}\text{C})$

| Parameter                      | Symbol            | Condition                                     | Min. | Тур. | Max. | Unit |

|--------------------------------|-------------------|-----------------------------------------------|------|------|------|------|

| Input Resistance               | R <sub>INAD</sub> | RSSI                                          | 10   | _    | _    | MΩ   |

| Output Resistance Load         | R <sub>LCAD</sub> | RSGAIN                                        | 10   | _    | _    | kΩ   |

| Output Capacitance Load        | C <sub>LAD</sub>  | RSGAIN                                        | _    | _    | _    | pF   |

| Input Voltage Range            | V <sub>INAD</sub> | When a RSGAIN signal is output.               | 0.7  | _    | 2.1  | V    |

| Offset Voltage Adjust Range    | O <sub>VLAD</sub> | _                                             | -600 | _    | +640 | mV   |

| Offset Voltage Adjust Accuracy | O <sub>VSAD</sub> | When offset voltage is adjusted per LSB step. | -20  | _    | +20  | mV   |

| A/D Conversion Resolution      | R <sub>ESAD</sub> | One LSB step                                  | _    | 5.5  | _    | mV   |

# **Digital Interface Characteristics (RSSI - ADC)**

| Parameter         | Symbol           | Condition     | Refer-<br>rence | Min. | Тур. | Max. | Unit |

|-------------------|------------------|---------------|-----------------|------|------|------|------|

| Output Delay Time | t <sub>DAD</sub> | Cload = 50 pF | Fig.12          | _    | 5    | _    | μS   |

# **Analog Interface Characteristics (Modem)**

$(V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}, \text{ Ta} = -25^{\circ}\text{C to } +70^{\circ}\text{C})$

|                                             |                  | ( 00                                              |      | ,    |          | /                |

|---------------------------------------------|------------------|---------------------------------------------------|------|------|----------|------------------|

| Parameter                                   | Symbol           | Condition                                         | Min. | Тур. | Max.     | Unit             |

| Output Resistance Load                      | R <sub>LIQ</sub> | I+, I-, Q+, Q-                                    | 10   | _    | _        | kΩ               |

| Output Capacitance Load                     | C <sub>LIQ</sub> | I+, I-, Q+, Q-                                    | _    | _    | 20       | pF               |

| Output DC Voltage Level                     | V <sub>DCM</sub> | I+, I-, Q+, Q- (TXW = 0)                          | 1.55 | 1.6  | 1.65     | ٧                |

| Output AC Voltage Level                     | V <sub>ACM</sub> | I+, I-, Q+, Q-<br>(For TXD = 0 continuous input)  | 340  | 360  | 380      | mV <sub>PP</sub> |

| Offset Voltage Difference                   | V <sub>OFF</sub> | Difference among<br>I+, I-, Q+ and Q-             | -20  | _    | +20      | mV               |

| Modulator D/A Conversion Sampling Frequency | F <sub>SDA</sub> | _                                                 | _    | 1.92 | _        | MHz              |

| Modulator D/A Conversion Offset Frequency   | F <sub>CDA</sub> | _                                                 | _    | 380  | _        | kHz              |

| Output DC Voltage Adjustment Level Range    | D <sub>CVL</sub> | _                                                 | _    | ±45  | _        | mV               |

| Output AC Voltage Adjustment Level Range    | A <sub>CVL</sub> | _                                                 | _    | ±4   | _        | %                |

| Out of hand Charteum                        | P600             | 600 kHz detuning                                  | 60   | _    | _        | dB               |

| Out-of-band Spectrum                        | P900             | 900 kHz detuning                                  | 65   | _    | _        | dB               |

| Modulation Accuracy                         | E <sub>VM</sub>  | _                                                 | _    | 1.0  | 3.0      | %<br>rms         |

| Demodulator Side IF Input Level             | I <sub>FV</sub>  | IFIN input level                                  | 0.5  | _    | $V_{DD}$ | V <sub>PP</sub>  |

| IFIN Input Impedance                        | R <sub>IF</sub>  | DC impedance                                      | _    | 20   | _        | kΩ               |

| SGM Output Voltage                          | V <sub>SGM</sub> | _                                                 |      | 2.0  |          | V                |

| SGM Output Impedance                        | R <sub>SGM</sub> | _                                                 |      | 1.5  |          | kΩ               |

| SGM Warm-up Time                            | T <sub>SG</sub>  | SGM↔AGM 0.1µF<br>(Rise Time to 90% of max. level) |      | 3    |          | ms               |

| MCK Input Level                             | lχ               |                                                   | 0.7  | _    | 2.0      | $V_{PP}$         |

| MCK Input Impedance                         | R <sub>X</sub>   | DC impedance                                      | _    | 20   | _        | kΩ               |

# **Digital Interface Characteristics (Modem)**

|                                   |                     |               | ( 00      |      |      |      |      |

|-----------------------------------|---------------------|---------------|-----------|------|------|------|------|

| Parameter                         | Symbol              | Condition     | Reference | Min. | Тур. | Max. | Unit |

| Transmit Digital I/O Setting Time | t <sub>XDM1,2</sub> | Oland FO mF   | Eig 10    | 0    | _    | 200  | ns   |

| Transmit Digital I/O Setting Time | t <sub>XDM3,4</sub> | Cload = 50 pF | Fig. 10   | 0    | _    | 400  | ns   |

| Receive Digital I/O Setting Time  | t <sub>RDM1,2</sub> | Cload = 50 pF | Fig. 11   | 0    | _    | 200  | ns   |

# **Analog Interface Characteristics (CODEC)**

| Powerester Comball Condition Min Tun May Unit |                   |                                    |      |      |      |                 |  |  |  |

|-----------------------------------------------|-------------------|------------------------------------|------|------|------|-----------------|--|--|--|

| Parameter                                     | Symbol            | Condition                          | Min. | Тур. | Max. | Unit            |  |  |  |

| Input Resistance                              | R <sub>INC</sub>  | AIN+, AIN-, PWI                    | 10   | _    | _    | MΩ              |  |  |  |

|                                               | R <sub>LC1</sub>  | GSX                                | 20   | _    | _    | kΩ              |  |  |  |

| Output Resistance Load                        | R <sub>LC2</sub>  | VFRO, SAO                          | 10   |      | _    | kΩ              |  |  |  |

|                                               | R <sub>LC3</sub>  | AOUT                               | 150  | _    | _    | Ω               |  |  |  |

|                                               | C <sub>LC1</sub>  | GSX                                |      |      | 100  | pF              |  |  |  |

| Output Capacitance Load                       | C <sub>LC2</sub>  | VFRO, SAO                          | _    | _    | 100  | pF              |  |  |  |

|                                               | C <sub>LC3</sub>  | AOUT                               | _    | _    | 100  | pF              |  |  |  |

|                                               | V <sub>OC1</sub>  | GSX ( $R_L = 20 \text{ k}\Omega$ ) | _    | _    | 1.3  | V <sub>PP</sub> |  |  |  |

| Output Valtana Laval (*4)                     | V                 | VFRO, SAO                          |      |      | 1.3  | V               |  |  |  |

| Output Voltage Level (*1)                     | V <sub>OC2</sub>  | $(R_L = 10 \text{ k}\Omega)$       |      |      | 1.3  | V <sub>PP</sub> |  |  |  |

|                                               | V <sub>OC3</sub>  | AOUT ( $R_L = 150 \Omega$ )        | _    | _    | 1.3  | V <sub>PP</sub> |  |  |  |

| 0,500                                         | V <sub>OFC1</sub> | VFRO, SAO                          | -100 | _    | +100 | mV              |  |  |  |

| Offset Voltage                                | V <sub>OFC2</sub> | GSX, AOUT                          | -20  | _    | +20  | mV              |  |  |  |

| SGCT, SGCR Output Voltage                     | V <sub>SGC</sub>  | SGCT, SGCR                         | _    | 1.4  | _    | V               |  |  |  |

| SGCT Output Impedance                         | R <sub>SGCT</sub> | SGCT                               | _    | 40   | 80   | kΩ              |  |  |  |

| SGCR Output Impedance                         | R <sub>SGCR</sub> | SGCR                               | _    | 4    | 8    | kΩ              |  |  |  |

|                                               | _                 | SGCT↔AGC 10+0.1μF                  |      | 700  |      |                 |  |  |  |

| SGCT Warm-up Time                             | T <sub>SGCT</sub> | (Rise time to 90% of max. level)   | _    | 700  | _    | ms              |  |  |  |

|                                               | _                 | SGCR↔AGC 10+0.1μF                  |      | 15   |      | ma              |  |  |  |

| SGCR Warm-up Time                             | T <sub>SGCR</sub> | (Rise time to 90% of max. level)   |      | 15   |      | ms              |  |  |  |

| Analog Switch OFF Resistance                  | R <sub>SWof</sub> | SW1 to SW5                         | 50   | _    | _    | MΩ              |  |  |  |

| Analog Switch ON Resistance                   | Rswon             | SW1 to SW5                         | 50   | 100  | 200  | Ω               |  |  |  |

<sup>\*1</sup>  $-7.7~dBm~(600~\Omega)=0~dBm0$ ,  $+3.14~dBm0=1.30~V_{PP}~(A-law)$   $-7.7~dBm~(600~\Omega)=0~dBm0$ ,  $+3.17~dBm0=1.30~V_{PP}~(\mu-law)$

# **Digital Interface Characteristics (CODEC)**

| Parameter                 | Symbol                                | Condition                                       | Reference | Min. | Тур. | Max.      | Unit |

|---------------------------|---------------------------------------|-------------------------------------------------|-----------|------|------|-----------|------|

|                           | t <sub>SDXC</sub> , t <sub>SDRC</sub> | Cload = 50 pF                                   |           | 0    | _    | 200 (100) | ns   |

| Digital Output Delay Time | t <sub>XDC1</sub> , t <sub>RDC1</sub> | pull-up resistor: 500 $\Omega$                  | F: 0      | 0    | _    | 200 (100) | ns   |

| PCM, ADPCM Interface      | $t_{XDC2}, t_{RDC2}$                  | Items in parenthesis<br>mean Cload = 10 pF, and | Fig. 8    | 0    | _    | 200 (100) | ns   |

|                           | t <sub>XDC3</sub> , t <sub>RDC3</sub> | moun oloud - 10 pr, und                         |           | 0    | _    | 200 (100) | ns   |

|                           | t <sub>C1</sub>                       |                                                 |           | 50   | _    | _         | ns   |

|                           | t <sub>C2</sub>                       |                                                 |           | 50   | _    | _         | ns   |

|                           | t <sub>C3</sub>                       |                                                 |           | 50   | _    | _         | ns   |

|                           | t <sub>C4</sub>                       |                                                 |           | 50   | _    | _         | ns   |

|                           | t <sub>C5</sub>                       |                                                 |           | 100  | _    | _         | ns   |

| Serial Port Digital I/O   | t <sub>C6</sub>                       | Oland                                           | Fig. 9    | 50   | _    | _         | ns   |

| Timing Characteristics    | t <sub>C7</sub>                       | Cload = 50 pF                                   |           | 50   | _    | _         | ns   |

|                           | t <sub>C8</sub>                       |                                                 |           | 0    | _    | 100       | ns   |

|                           | t <sub>C9</sub>                       |                                                 |           | 50   | _    | _         | ns   |

|                           | t <sub>C10</sub>                      |                                                 |           | 50   | _    | _         | ns   |

|                           | t <sub>C11</sub>                      |                                                 |           | 0    | _    | 50        | ns   |

|                           | t <sub>C12</sub>                      |                                                 |           | 200  | _    | _         | ns   |

| EXCK Clock Frequency      | F <sub>exck</sub>                     | EXCK                                            | _         | _    | _    | 10        | MHz  |

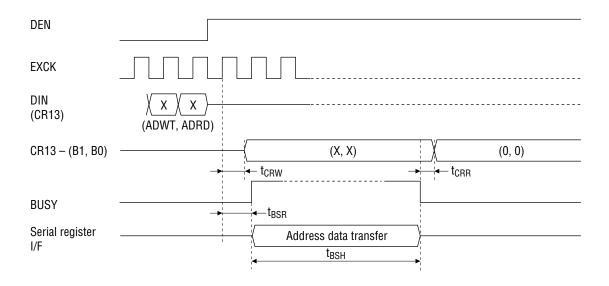

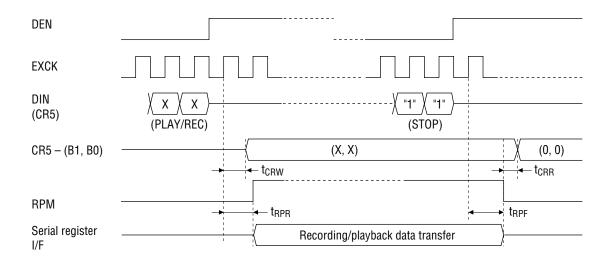

# **Serial Interface Characteristics**

| Parameter                   | Symbol           | Condition               | Refer-<br>rence | Min. | Тур. | Max. | Unit |

|-----------------------------|------------------|-------------------------|-----------------|------|------|------|------|

| Control Register Data Input | t <sub>CRW</sub> | Write                   |                 | _    | _    | 200  | ns   |

| Control Register Data Input | t <sub>CRR</sub> | Reset                   |                 | _    | _    | 200  | ns   |

| DUCV D:+                    | t <sub>BSR</sub> | Rising                  | F: 4.F          | _    | _    | 10   | μs   |

| BUSY Bit                    | t <sub>BSH</sub> | Active time             | Fig.15          | _    | _    | 450  | μS   |

| RPM Bit                     | t <sub>RPR</sub> | Rising                  |                 | _    | _    | 10   | μS   |

| NPIVI BIL                   | t <sub>RPF</sub> | Falling at Stop command |                 | _    | _    | 135  | μS   |

# **AC Characteristics (CODEC)**

| Dawamatan              |                     | Cond           | lition      |       | _         |       |      |  |  |

|------------------------|---------------------|----------------|-------------|-------|-----------|-------|------|--|--|

| Parameter              | Symbol              | Frequency (Hz) | Level dBm0  | Min.  | Тур.      | Max.  | Unit |  |  |

|                        | L <sub>OSS</sub> T1 | 0 to 60        |             | 25    | _         | _     | dB   |  |  |

|                        | L <sub>OSS</sub> T2 | 300 to 3 k     |             | -0.15 | _         | +0.20 | dB   |  |  |

| Transmit Frequency     | L <sub>OSS</sub> T3 | 1020           | ٥           |       | Reference |       |      |  |  |

| Response               | L <sub>OSS</sub> T4 | 3300           | 0           | -0.15 | _         | +0.80 | dB   |  |  |

|                        | L <sub>OSS</sub> T5 | 3400           |             | 0     | _         | 0.80  | dB   |  |  |

|                        | L <sub>OSS</sub> T6 | 3968.75        |             | 13    | _         | _     | dB   |  |  |

|                        | L <sub>OSS</sub> R1 | 0 to 3000      |             | -0.15 | _         | +0.20 | dB   |  |  |

| Dogojuo Fraguenou      | L <sub>OSS</sub> R2 | 1020           |             |       | Reference |       | dB   |  |  |

| Receive Frequency      | L <sub>OSS</sub> R3 | 3300           | 0           | -0.15 | _         | +0.80 | dB   |  |  |

| Response               | L <sub>OSS</sub> R4 | 3400           |             | 0     | _         | 0.80  | dB   |  |  |

|                        | L <sub>OSS</sub> R5 | 3968.75        |             | 13    | _         | _     | dB   |  |  |

|                        | SD T1               |                | 3           | 35    | _         | _     | dB   |  |  |

| Transmit Cianal to     | SD T2               |                | 0           | 35    | _         | _     | dB   |  |  |

| Transmit Signal to     | SD T3               | 1020           | -30         | 35    | _         | _     | dB   |  |  |

| Distortion Ratio (*2)  | SD T4               |                | -40         | 28    | _         | _     | dB   |  |  |

|                        | SD T5               |                | -45         | 23    | _         | _     | dB   |  |  |

|                        | SD R1               |                | 3           | 35    | _         | _     | dB   |  |  |

| Donaire Cianal to      | SD R2               |                | 0           | 35    | _         | _     | dB   |  |  |

| Receive Signal to      | SD R3               | 1020           | -30         | 35    | _         | _     | dB   |  |  |

| Distortion Ratio (*2)  | SD R4               |                | -40         | 28    | _         | _     | dB   |  |  |

|                        | SD R5               |                | -45         | 23    | _         | _     | dB   |  |  |

|                        | GT T1               |                | 3           | -0.2  | _         | +0.2  | dB   |  |  |

| Transmit Gain          | GT T2               |                | -10         |       | Reference |       | dB   |  |  |

|                        | GT T3               | 1020           | -40         | -0.2  | _         | +0.2  | dB   |  |  |

| Tracking  Receive Gain | GT T4               |                | -50         | -0.5  | _         | +0.5  | dB   |  |  |

|                        | GT T5               |                | <b>–</b> 55 | -1.2  |           | +1.2  | dB   |  |  |

|                        | GT R1               |                | 3           | -0.2  | _         | +0.2  | dB   |  |  |

|                        | GT R2               |                | -10         |       | Reference |       | dB   |  |  |

| Tracking               | GT R3               | 1020           | -40         | -0.2  | _         | +0.2  | dB   |  |  |

| Hacking                | GT R4               |                | -50         | -0.5  | _         | +0.5  | dB   |  |  |

|                        | GT R5               |                | <b>-</b> 55 | -1.2  | _         | +1.2  | dB   |  |  |

<sup>\*2</sup> P-message filter used

MSM7584D

# **AC Characteristics (CODEC) (Continued)**

$(V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}, \text{ Ta} = -25^{\circ}\text{C to } +70^{\circ}\text{C})$

| Parameter                  | Cumbal            |                  | ondition             | Min. | T      | Max.  | Unit    |        |

|----------------------------|-------------------|------------------|----------------------|------|--------|-------|---------|--------|

| Parameter                  | Symbol            | Frequency (Hz)   | Level dBm0 Other     |      | IVIII. | Тур.  | wax.    | Unit   |

|                            | M                 |                  | AIN = SG             |      | _      | _     | -68     |        |

| Idle Channel Noise<br>(*2) | N <sub>IDLT</sub> | _                |                      | _    |        |       | (-75.7) | dBm0p  |

|                            | N <sub>IDLR</sub> | _                | (*3)                 | _    | _      | _     | -72     | (dBmp) |

|                            |                   |                  |                      |      |        |       | (-79.7) |        |

| Abaqluta Laval (*4)        | A <sub>VT</sub>   | 1020             | 0                    | GSX2 | 0.285  | 0.320 | 0.359   | Vrms   |

| Absolute Level (*4)        | A <sub>VR</sub>   | 1020             | U                    | VFR0 | 0.285  | 0.320 | 0.359   | Vrms   |

| Power Supply Noise         | P <sub>SRRT</sub> | Noise frequency: | Noise level:         |      | 30     | _     | _       | dB     |

| Rejection Ratio            | P <sub>SRRR</sub> | 0 kHz to 50 kHz  | $50 \text{ mV}_{PP}$ |      | 30     | _     | _       | dB     |

<sup>\*2</sup> P-message filter used

ADPCM characteristics are fully compliant with ITU-T Recommendation G.721.

# **AC Characteristics (DTMF and Other Tones)**

$(V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}, Ta = -25^{\circ}\text{C to } +70^{\circ}\text{C})$

| Parameter                      | Symbol            | C                                                 | Condition                | Min. | Тур. | Max. | Unit |

|--------------------------------|-------------------|---------------------------------------------------|--------------------------|------|------|------|------|

| Fraguency Deviation            | D <sub>FT1</sub>  | DTMF tones                                        | <b>-</b> 7               | _    | +7   | Hz   |      |

| Frequency Deviation            | D <sub>FT2</sub>  | Other various tones                               | <b>-</b> 7               |      | +7   | Hz   |      |

| Tama Dafawanaa                 | V <sub>TL</sub>   | Transmit side tone DTMF (low group)               |                          | -18  | -16  | -14  | dBm0 |

| Tone Reference                 | $V_{TH}$          | (OdB when gain setting)                           | DTMF (high group), other | -16  | -14  | -12  | dBm0 |

| Output Level<br>(*5)           | $V_{RL}$          | Receive side tone                                 | DTMF (low group)         | -10  | -8   | -6   | dBm0 |

|                                | $V_{RH}$          | (-OdB when gain setting) DTMF (high group), other |                          | -8   | -6   | -4   | dBm0 |

| DTMF Tone Level Relative Value | R <sub>DTMF</sub> | VTH/VTL, VRH/VRI                                  | L                        | 1    | 2    | 3    | dB   |

<sup>\*5</sup> Not including programmable gain set values

#### **AC Characteristics (Gain Settings)**

$(V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}, \text{ Ta} = -25^{\circ}\text{C to } +70^{\circ}\text{C})$

| Parameter             | Symbol         | Condition               | Min. | Тур. | Max. | Unit |

|-----------------------|----------------|-------------------------|------|------|------|------|

| Transmit/Receive Gain | n.             | For all gain act values | 4    | 0    | . 4  | ٩D   |

| Setting Accuracy      | D <sub>G</sub> | For all gain set values | -    | U    | +1   | dB   |

## **AC Characteristics (VOX Function)**

| Parameter                | Symbol            |                | Min.                 | Тур.     | Max.             | Unit    |    |

|--------------------------|-------------------|----------------|----------------------|----------|------------------|---------|----|

| Transmit VOX             | т.                | Cilonos vuoiss | VOVO min. Con Fig. 0 |          | 10 <sup>*6</sup> |         | mo |

| Detection Time           | T <sub>VXON</sub> | Silence→voice  | VOXO pin: See Fig. 2 | _        | 10               | _       | ms |

| (Voice and Silence       | т                 | Voice dilence  | Voice/silence        | 1.40/200 | 160/320          | 180/340 | m. |

| Detection Time)          | IVXOF             | Voice→silence  | differential: 10 dB  | 140/300  |                  |         | ms |

| Transmit VOX             |                   | For detection  | lovel est values by  | -2.5     | 0                | +2.5    |    |

| Detection Level Accuracy | D <sub>VX</sub>   |                | level set values by  |          |                  |         | dB |

| (Voice Detection Level)  |                   | CR6 - B6, B5   |                      |          |                  |         |    |

<sup>\*6</sup> When single tone at 1000Hz.

<sup>\*3</sup> PCMRI input: "11010101" (A-law), "111111111" (μ-law)

<sup>\*4</sup>  $0.320 \text{ Vrms} = 0 \text{ dBm0} = -7.7 \text{ dBm } (600 \Omega)$

# TIMING DIAGRAM (ADPCM CODEC)

# **Transmit Side PCM, ADPCM Timing**

## Receive Side PCM, ADPCM Timing

Figure 8 PCM, ADPCM Interface

## **Serial Port Timing for Microcontroller Interface**

Figure 9 Serial Control Port Interface

# TIMING DIAGRAM

## (Modem)

# **Transmit Data Input Timing**

# Transmit Clock (TXCO) Output Timing (When CR14 - B6 = 1)

# Transmit Burst Position (BSTO) Output Timing (When CR14 - B6 = 0)

Figure 10 Modem Transmit Side (Modulator Side) Digital I/O Timing

## Receive Side Data I/O Timing

Figure 11 Receive Side (Demodulator Side) Digital I/O Timing

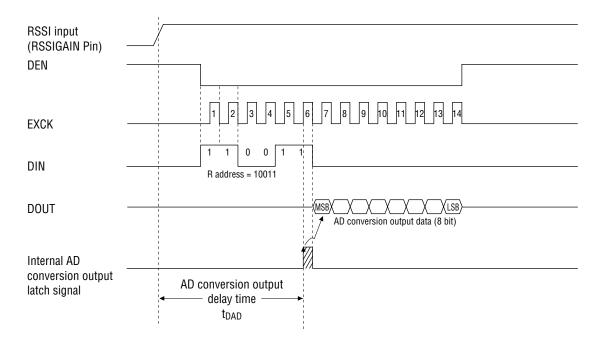

# TIMING DIAGRAM (RSSI - ADC) RSSI - ADC Output Timing

Notes:

- 1. AD conversion output data corresponds to the RSSI analog input value between the rising edge of the 6th EXCK clock pulse and the start point of the AD conversion output delay time ( $t_{DAD}$ ).

- 2. Normal AD conversion output data is output approximately 1ms after the power down mode is cancelled.

Figure 12 RSSI - ADC Output Timing

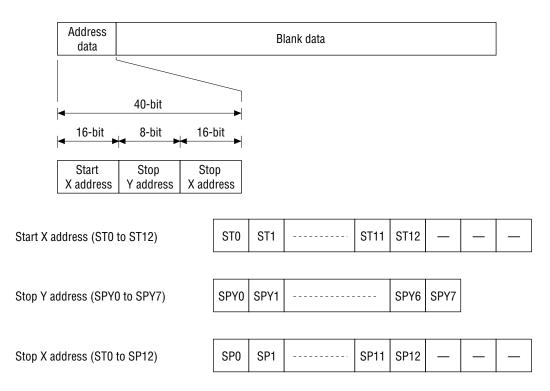

# TIMING DIAGRAM (Serial Register Interface) Address Write/Read Timing

## **Recording/Playback Timing**

Figure 13 Serial Register Interface

#### **Mode State Transition Time in Modem**

Figure 14 Transition Between Power-Down Mode and Power-ON Mode

# Timing Diagram for Demodulator Control in Modem (Example)

Figure 15 Modem Unit Demodulator Timing Diagram Example

#### **FUNCTIONAL DESCRIPTION**

# Control Register Description Table (ADPCM CODEC)

(1) CR0 (Basic Operation Mode Settings)

|                   | В7  | В6 | B5  | B4 | В3 | B2     | B1       | В0     |

|-------------------|-----|----|-----|----|----|--------|----------|--------|

| CDO               | A/μ |    | PDN |    |    | SA, VF | CACATEDO | SA, VF |

| CR0               | SEL | _  | ALL | _  | _  | _ OUT  | SAO/VFRO | _ PDN  |

| Initial Value (*) | 0   | 0  | 0   | 0  | 0  | 0      | 0        | 0      |

<sup>\*</sup> The initial value means a value which is set when the device is reset using the RESET signal.

| B7:PCM interface companding selection 0: μ-law 1: A-law                             |

|-------------------------------------------------------------------------------------|

| B6:Not used                                                                         |

| B5:Power down (entire unit) 0: Power ON 1: Power down                               |

| ORed with the inverting external power down signal PDN3. When using                 |

| this data, set PDN3 to "1".                                                         |

| B2:Output from VFRO and SAO at a time                                               |

| 0: Receive side output signals are output from a pin selected by B1.                |

| 1: Receive side output signals are output from VFRO and SAO at a time.              |

| B1:Receive side output switch control                                               |

| 0: Receive side output signals appear on the SAO (Sounder Amplifier                 |

| Output) pin.                                                                        |

| 1: These signals appear on the VFRO (Receiver Amplifier Output) pin.                |

| B0:Power down control for sounder output amplifier (SAO) and receiver               |

| output amplifier (VFRO).                                                            |

| 0: When SAO is selected by CR0 - B1, VFRO is powered down.                          |

| When VFRO is selected, SAO is powered down.                                         |

| 1: Both SAO and VFRO are powered ON.                                                |

| B4, B3: Not used (These pins are used to test the device. They should be set to "0" |

during normal operation.)

## (2) CR1 (ADPCM Operation Mode Settings)

|               | В7     | В6     | B5    | B4   | В3   | B2        | B1      | В0   |

|---------------|--------|--------|-------|------|------|-----------|---------|------|

| CD4           | TX     | RX     | ADPCM | TX   | RX   | MLV2 MLV1 | NAL \/4 | MINO |

| CR1           | ON/OFF | ON/OFF | RESET | MUTE | MUTE |           | MLV0    |      |

| Initial Value | 0      | 0      | 0     | 0    | 0    | 0         | 0       | 0    |

B7: ......Transmit side PCM signal ON/OFF. 0: ON 1: OFF

OFF: Idle channel state

B6: ......Receive side PCM signal ON/OFF. 0: ON 1: OFF

OFF: PCM idle pattern is transmitted.

B5: ......ADPCM reset (as specified by G. 721) 1: reset\*

B4: ..... Transmit side MUTE.

0: Transmit MUTE OFF.

1: Transmit MUTE ON.

Transmit output is in an idle state.

B3:.....Receive side MUTE. This bit is ORed with the external control pin RXMUTE.

- 0: Receive side MUTE OFF.

- 1: Receive side MUTE ON. The receive side output signals are attenuated by the values represented by a combination of bits B2, B1, and B0 of the CR1. (For voice path only.)

- B2, B1, B0: An attenuation value is selected at receive side MUTE (CR1 B3 = "1") (see Table 3). These bits are ORed with the external pins MLV2, MLV1, and MLV0.

**Table 3 MUTE Level Settings**

| B2 | B1 | В0 | Attenuation value |

|----|----|----|-------------------|

| 0  | 0  | 0  | OdB loss          |

| 0  | 0  | 1  | - 6dB loss        |

| 0  | 1  | 0  | -12dB loss        |

| 0  | 1  | 1  | -18dB loss        |

| 1  | 0  | 0  | -24dB loss        |

| 1  | 0  | 1  | -30dB loss        |

| 1  | 1  | 0  | -36dB loss        |

| 1  | 1  | 1  | MUTE (idle state) |

<sup>\*</sup> The rest width should be 125µs or more.

### (3) CR2 (PCMCODEC Operation Mode Settings and Transmit/Receive Gain Adjustment)

|               | В7    | В6    | B5    | B4    | В3    | B2    | B1    | В0    |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| CDO           | TX    | TX    | TX    | TX    | RX    | RX    | RX    | RX    |

| CR2           | GAIN3 | GAIN2 | GAIN1 | GAIN0 | GAIN3 | GAIN2 | GAIN1 | GAIN0 |

| Initial Value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

B7, B6, B5, B4: ...... Transmit side signal gain adjustment (see Table 4)

B3, B2, B1, B0: ...... Receive side signal gain adjustment (see Table 4)

**Table 4 Receive/Transmit Gain Settings**

| Transmit/<br>receive gain | В7 | В6 | B5 | B4 | В3 | B2 | B1 | В0 |

|---------------------------|----|----|----|----|----|----|----|----|

| -16dB                     | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 0  |

| -14dB                     | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1  |

| -12dB                     | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  |

| -10dB                     | 1  | 0  | 1  | 1  | 1  | 0  | 1  | 1  |

| – 8dB                     | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0  |

| - 6dB                     | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 1  |

| – 4dB                     | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 0  |

| – 2dB                     | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| 0dB                       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 2dB                       | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  |

| 4dB                       | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  |

| 6dB                       | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1  |

| 8dB                       | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 0  |

| 10dB                      | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  |

| 12dB                      | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0  |

| 14dB                      | 0  | 1  | 1  | 1  | 0  | 1  | 1  | 1  |

The above gain settings table shows the transmit/receive voice signal gain settings and the transmit side gain settings for DTMF tones and other tones. Tone signal transmission is enabled by CR4 - B6 (discussed later), and the gain setting is set to the levels shown below.

DTMF tones (low group): .....-16 dBm0

DTMF tones (high group) and other tones: ... –14 dBm0

For example, if the transmit gain set value is set to +8 dB (B7, B6, B5, B4) = (0, 1, 0, 0), then the following tones appear at the PCMSO pin.

DTMF tones (low group): .....-8 dBm0

DTMF tones (high group) and other tones: ... -6 dBm0

-3 dBm0 (mixed tone)

However, the gain of the receive side tone and the gain of the side tones (path from transmit side to receive side) are set by the CR3 register.

MSM7584D

# (4) CR3 (Side Tone and Tone Generator Gain Adjustment)

|               | В7        | В6        | B5        | В4     | В3    | B2    | B1    | В0    |

|---------------|-----------|-----------|-----------|--------|-------|-------|-------|-------|

| CD2           | Side Tone | Side Tone | Side Tone | TONE   | TONE  | TONE  | TONE  | TONE  |

| CR3           | GAIN2     | GAIN1     | GAIN0     | ON/OFF | GAIN3 | GAIN2 | GAIN1 | GAIN0 |

| Initial Value | 0         | 0         | 0         | 0      | 0     | 0     | 0     | 0     |

B7, B6, B5: ...... Side tone gain adjustment (refer to Table 5)

B4: ...... Tone generator ON/OFF 0: OFF 1: ON

B3, B2, B1, B0: . Tone generator

Receive side gain adjustment (refer to Table 6)

**Table 5 Side Tone Gain Settings**

| B7 | В6 | B5 | Side Tone Gain |

|----|----|----|----------------|

| 0  | 0  | 0  | OFF            |

| 0  | 0  | 1  | −15 dB         |

| 0  | 1  | 0  | −13 dB         |

| 0  | 1  | 1  | −11 dB         |

| 1  | 0  | 0  | −9 dB          |

| 1  | 0  | 1  | −7 dB          |

| 1  | 1  | 0  | −5 dB          |

| 1  | 1  | 1  | −3 dB          |

## **Table 6 Receive Side Tone Generator Gain Settings**

| В3 | B2 | B1 | В0 | Tone Generator Gain | В3 | B2 | B1 | В0 | <b>Tone Generator Gain</b> |

|----|----|----|----|---------------------|----|----|----|----|----------------------------|

| 0  | 0  | 0  | 0  | −32 dB              | 1  | 0  | 0  | 0  | −16 dB                     |

| 0  | 0  | 0  | 1  | –30 dB              | 1  | 0  | 0  | 1  | −14 dB                     |

| 0  | 0  | 1  | 0  | –28 dB              | 1  | 0  | 1  | 0  | −12 dB                     |

| 0  | 0  | 1  | 1  | –26 dB              | 1  | 0  | 1  | 1  | -10 dB                     |

| 0  | 1  | 0  | 0  | −24 dB              | 1  | 1  | 0  | 0  | −8 dB                      |

| 0  | 1  | 0  | 1  | –22 dB              | 1  | 1  | 0  | 1  | −6 dB                      |

| 0  | 1  | 1  | 0  | –20 dB              | 1  | 1  | 1  | 0  | −4 dB                      |

| 0  | 1  | 1  | 1  | −18 dB              | 1  | 1  | 1  | 1  | −2 dB                      |

The receive side tone generator gain settings shown in Table 6 are set with the following levels as a reference.

DTMF tones (low group): ..... –2 dBm0

DTMF tones (high group) and other tones: ... 0 dBm0

For example, if the tone generator gain set value is set to –6 dB (B3, B2, B1, B0)=(1, 1, 0, 1), then tones at the following levels appear at the SAO+/SAO- or VFRO pin.

DTMF tones (low group): .....-8 dBm0

DTMF tones (high group) and other tones: ... -6 dBm0

-3 dBm0 (mixed tone)

# (5) CR4 (Tone Generator Operation Mode and Frequency Settings)

|               | B7                  | В6           | B5    | B4    | В3    | B2    | B1    | В0    |

|---------------|---------------------|--------------|-------|-------|-------|-------|-------|-------|

| CR4           | DTMF/<br>OTHERS SEL | TONE<br>SEND | TONE5 | TONE4 | TONE3 | TONE2 | TONE1 | TONE0 |

| Initial Value | 0                   | 0            | 0     | 0     | 0     | 0     | 0     | 0     |

B7: ..... Selection of DTMF signal and other tones

(Stone, Ftone, Rtone, etc.) 0: Other tones 1: DTMF signal

B6: ..... Transmission side tone transmit

0: Voice signal transmit 1: Tone transmit

B5, B4, B3, B2, B1, B0: Tone frequency setting (refer to Table 7)

# **Table 7 Tone Generator Frequency Settings**

# (a) When B7 = 1 (DTMF Tones)

| B5 | B4 | В3 | B2 | B1 | В0 | Description      | B5 | B4 | В3 | B2 | B1 | В0 | Description      |

|----|----|----|----|----|----|------------------|----|----|----|----|----|----|------------------|

| *  | *  | 0  | 0  | 0  | 0  | 697 Hz + 1209 Hz | *  | *  | 0  | 0  | 0  | 0  | 852 Hz + 1209 Hz |

| *  | *  | 0  | 0  | 0  | 1  | 697 Hz + 1336 Hz | *  | *  | 0  | 0  | 0  | 1  | 852 Hz + 1336 Hz |

| *  | *  | 0  | 0  | 1  | 0  | 697 Hz + 1477 Hz | *  | *  | 0  | 0  | 1  | 0  | 852 Hz + 1477 Hz |

| *  | *  | 0  | 0  | 1  | 1  | 697 Hz + 1633 Hz | *  | *  | 0  | 0  | 1  | 1  | 852 Hz + 1633 Hz |

| *  | *  | 0  | 1  | 0  | 0  | 770 Hz + 1209 Hz | *  | *  | 0  | 1  | 0  | 0  | 941 Hz + 1209 Hz |

| *  | *  | 0  | 1  | 0  | 1  | 770 Hz + 1336 Hz | *  | *  | 0  | 1  | 0  | 1  | 941 Hz + 1336 Hz |

| *  | *  | 0  | 1  | 1  | 0  | 770 Hz + 1477 Hz | *  | *  | 0  | 1  | 1  | 0  | 941 Hz + 1477 Hz |

| *  | *  | 0  | 1  | 1  | 1  | 770 Hz + 1633 Hz | *  | *  | 0  | 1  | 1  | 1  | 941 Hz + 1633 Hz |

# (b) When B7 = 0 (Other than DTMF Tones)

| <b>B</b> 5 | В4 | ВЗ | B2 | B1 | ВО | Desci          | ription      | В5 | В4 | В3 | B2 | В1 | В0 | Des     | cription    |

|------------|----|----|----|----|----|----------------|--------------|----|----|----|----|----|----|---------|-------------|

| 0          | 0  | 0  | 0  | 0  | 0  | 400/500 Hz     | 8 Hz Wamble  | 1  | 0  | 0  | 0  | 0  | 0  | 1100 Hz | Single tone |

| 0          | 0  | 0  | 0  | 0  | 1  | 800/1 Hz       | 8 Hz Wamble  | 1  | 0  | 0  | 0  | 0  | 1  | 1142 Hz | Single tone |

| 0          | 0  | 0  | 0  | 1  | 0  | 400/500 Hz     | 16 Hz Wamble | 1  | 0  | 0  | 0  | 1  | 0  | 1200 Hz | Single tone |

| 0          | 0  | 0  | 0  | 1  | 1  | 400/1 Hz       | 16 Hz Wamble | 1  | 0  | 0  | 0  | 1  | 1  | 1210 Hz | Single tone |

| 0          | 0  | 0  | 1  | 0  | 0  | 667/800 Hz     | 16 Hz Wamble | 1  | 0  | 0  | 1  | 0  | 0  | 1250 Hz | Single tone |

| 0          | 0  | 0  | 1  | 0  | 1  | 800/1 Hz       | 16 Hz Wamble | 1  | 0  | 0  | 1  | 0  | 1  | 1300 Hz | Single tone |

| 0          | 0  | 0  | 1  | 1  | 0  | 1 k/1.33 kHz   | 16 Hz Wamble | 1  | 0  | 0  | 1  | 1  | 0  | 1333 Hz | Single tone |

| 0          | 0  | 0  | 1  | 1  | 1  | 2.7 k/1 kHz    | 16 Hz Wamble | 1  | 0  | 0  | 1  | 1  | 1  | 1360 Hz | Single tone |

| 0          | 0  | 1  | 0  | 0  | 0  | 2 k/2.1 kHz    | 16 Hz Wamble | 1  | 0  | 1  | 0  | 0  | 0  | 1410 Hz | Single tone |

| 0          | 0  | 1  | 0  | 0  | 1  | 2 k/2.7 kHz    | 8 Hz Wamble  | 1  | 0  | 1  | 0  | 0  | 1  | 1455 Hz | Single tone |

| 0          | 0  | 1  | 0  | 1  | 0  | 2.6 k/2.7 kHz  | 16 Hz Wamble | 1  | 0  | 1  | 0  | 1  | 0  | 1477 Hz | Single tone |

| 0          | 0  | 1  | 0  | 1  | 1  | 3.2 k/3.31 kHz | 16 Hz Wamble | 1  | 0  | 1  | 0  | 1  | 1  | 1500 Hz | Single tone |

| 0          | 0  | 1  | 1  | 0  | 0  | 400 kHz        | 16 Hz Wamble | 1  | 0  | 1  | 1  | 0  | 0  | 3310 Hz | Single tone |

| 0          | 0  | 1  | 1  | 0  | 1  | 2 kHz          | 16 Hz Wamble | 1  | 0  | 1  | 1  | 0  | 1  | 1600 Hz | Single tone |

| 0          | 0  | 1  | 1  | 1  | 0  | 2.7 kHz        | 16 Hz Wamble | 1  | 0  | 1  | 1  | 1  | 0  | 1635 Hz | Single tone |

| 0          | 0  | 1  | 1  | 1  | 1  | 400 kHz        | 10 Hz Wamble | 1  | 0  | 1  | 1  | 1  | 1  | 1710 Hz | Single tone |

| 0          | 1  | 0  | 0  | 0  | 0  | 350 + 440 kHz  | Mixed tone   | 1  | 1  | 0  | 0  | 0  | 0  | 1800 Hz | Single tone |

| 0          | 1  | 0  | 0  | 0  | 1  | 400 + 480 kHz  | Mixed tone   | 1  | 1  | 0  | 0  | 0  | 1  | 1900 Hz | Single tone |

| 0          | 1  | 0  | 0  | 1  | 0  | 480 + 620 kHz  | Mixed tone   | 1  | 1  | 0  | 0  | 1  | 0  | 2000 Hz | Single tone |

| 0          | 1  | 0  | 0  | 1  | 1  | 350 kHz        | Single tone  | 1  | 1  | 0  | 0  | 1  | 1  | 2100 Hz | Single tone |

| 0          | 1  | 0  | 1  | 0  | 0  | 400 kHz        | Single tone  | 1  | 1  | 0  | 1  | 0  | 0  | 2200 Hz | Single tone |

| 0          | 1  | 0  | 1  | 0  | 1  | 440 kHz        | Single tone  | 1  | 1  | 0  | 1  | 0  | 1  | 2285 Hz | Single tone |

| 0          | 1  | 0  | 1  | 1  | 0  | 480 kHz        | Single tone  | 1  | 1  | 0  | 1  | 1  | 0  | 2400 Hz | Single tone |

| 0          | 1  | 0  | 1  | 1  | 1  | 500 kHz        | Single tone  | 1  | 1  | 0  | 1  | 1  | 1  | 2500 Hz | Single tone |

| 0          | 1  | 1  | 0  | 0  | 0  | 533 kHz        | Single tone  | 1  | 1  | 1  | 0  | 0  | 0  | 2600 Hz | Single tone |

| 0          | 1  | 1  | 0  | 0  | 1  | 571 kHz        | Single tone  | 1  | 1  | 1  | 0  | 0  | 1  | 2670 Hz | Single tone |

| 0          | 1  | 1  | 0  | 1  | 0  | 620 kHz        | Single tone  | 1  | 1  | 1  | 0  | 1  | 0  | 2700 Hz | Single tone |

| 0          | 1  | 1  | 0  | 1  | 1  | 667 kHz        | Single tone  | 1  | 1  | 1  | 0  | 1  | 1  | 2820 Hz | Single tone |

| 0          | 1  | 1  | 1  | 0  | 0  | 727 kHz        | Single tone  | 1  | 1  | 1  | 1  | 0  | 0  | 2910 Hz | Single tone |

| 0          | 1  | 1  | 1  | 0  | 1  | 800 kHz        | Single tone  | 1  | 1  | 1  | 1  | 0  | 1  | 3000 Hz | Single tone |

| 0          | 1  | 1  | 1  | 1  | 0  | 888 kHz        | Single tone  | 1  | 1  | 1  | 1  | 1  | 0  | 3110 Hz | Single tone |

| 0          | 1  | 1  | 1  | 1  | 1  | 1000 kHz       | Single tone  | 1  | 1  | 1  | 1  | 1  | 1  | 3200 Hz | Single tone |

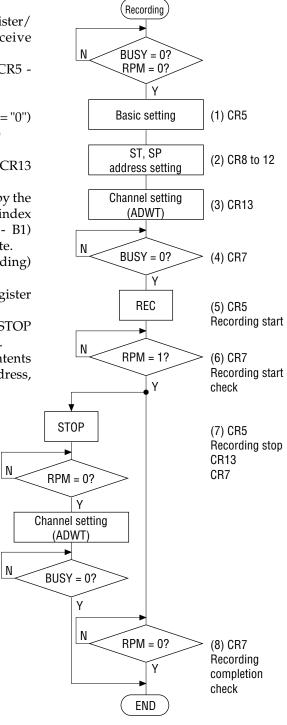

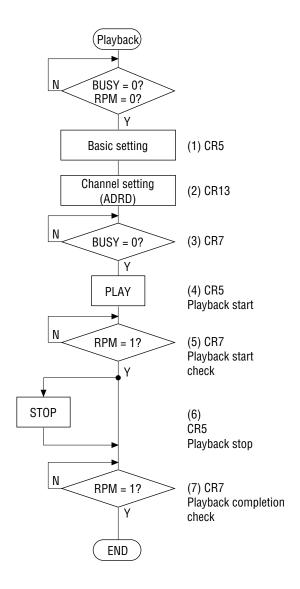

# (6) CR5 (Control of Serial Register I/F)

|               | В7           | В6         | B5          | B4 | В3 | B2 | B1   | В0   |

|---------------|--------------|------------|-------------|----|----|----|------|------|

| CR5           | SEND/<br>REC | ROM/<br>SR | 4M8M/<br>1M | _  | _  | _  | CMD1 | CMD0 |

| Initial Value | 0            | 0          | 0           | 0  | 0  | 0  | 0    | 0    |

B7: ..... Register I/F connection.

0: Connection with ADPCM receiver

1: Connection with ADPCM transmitter

B6: ......Switching between voice ROM and serial register.

0: Serial register

1: Voice ROM

B5: ......Capacitance of serial register to be connected.

0: 1 Mbit (MSM6389)

1: 4 Mbit (MSM6684), 8 Mbit (MSM6685)

B1, B0: ...... Serial register I/F command (CMD1, CMD0) =

(0.0): NOP

(0.1): PLAY

(1.0): REC (RECORD)

(1. 1): STOP

Note: CMD1 and CMD0 are reset to "0" after the instruction is executed.

The PLAY and REC instructions must not be executed when BUSY (CR5 - B1) and RPM  $\,$

(CR5 - B0) are set to "1".

### (7) CR6 (VOX Function Control)

|               | В7     | В6   | B5   | B4   | В3  | B2        | B1       | В0       |

|---------------|--------|------|------|------|-----|-----------|----------|----------|

| CDC           | VOX    | ON   | ON   | OFF  | VOX | RX NOISE  | RX NOISE | RX NOISE |