# **OKI** Semiconductor

This version: Jan. 1998 Previous version: Nov. 1996

# MSM6927/6947

1200 bps Single Chip FSK MODEM

#### **GENERAL DESCRIPTION**

The MSM6927 and the MSM6947 are OKI's 1200 bps single chip modem series which transmit and receive serial, binary data over a switched telephone network using frequency shift keying(FSK).

The MSM6927 is compatible with ITU-T V.23 series data sets, while the MSM6947 is compatible with Bell 202 series data sets.

These devices provide all the necessary modulation, demodulation, and filtering required to implement a serial, asynchronous communication link.

OKI's single chip modem series is designed for users who are not telecommunication experts and are easy to use cost effective alternative to standard discrete modem design.

CMOS LSI technology provides the advantages of small size, low power, and increased reliability.

The design of the integrated circuit assures compatibility with a broad base of installed low speed modems and acoustic couplers. Applications include interactive terminals, desk top computers, point of sale equipment, and credit verification systems.

#### **FEATURES**

- Compatible with ITU-T V.23 (MSM6927)

- Compatible with BELL 202 (MSM6947)

- CMOS silicon gate process

- Switched capacitor and advanced CMOS analog technology

- Data rate from 0 to 1200 bps

- Half duplex (2-Wire)

- Receive squelch delay

- Selectable built-in timers and external delay timers possible

- All filtering, modulation, demodulation, and DTE interface on chip

- Crystal controlled oscillator on chip

- TTL compatible digital interface

- Low power dissipation: 90 mW Typ.

- Package options:

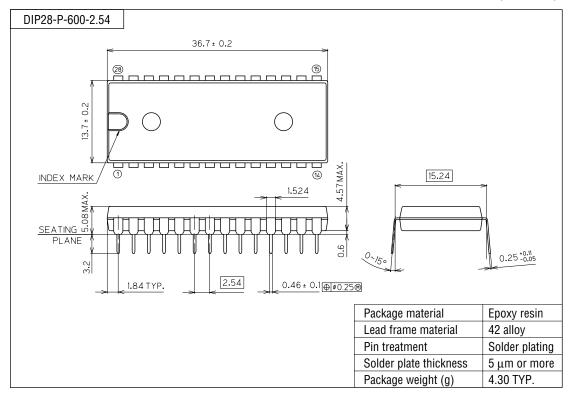

28-pin plastic DIP (DIP28-P-600–2.54) (Product name: MSM6927RS) (Product name: MSM6947RS)

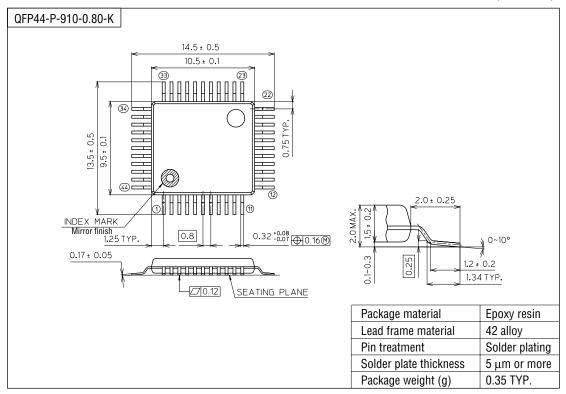

44-pin plastic QFP (QFP44-P-910-0.80–K) (Product name: MSM6927GS-K)

(Product name: MSM6947GS-K)

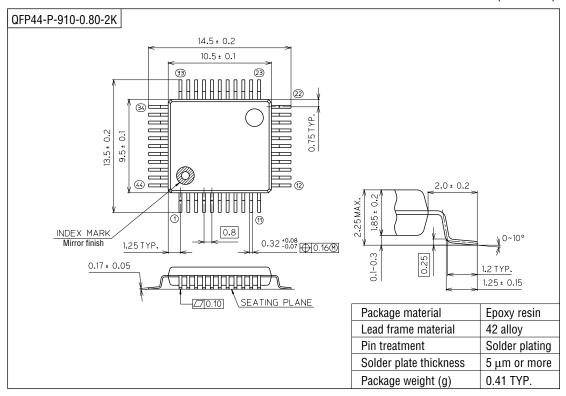

(QFP44-P-910-0.80–2K) (Product name: MSM6927GS-2K)

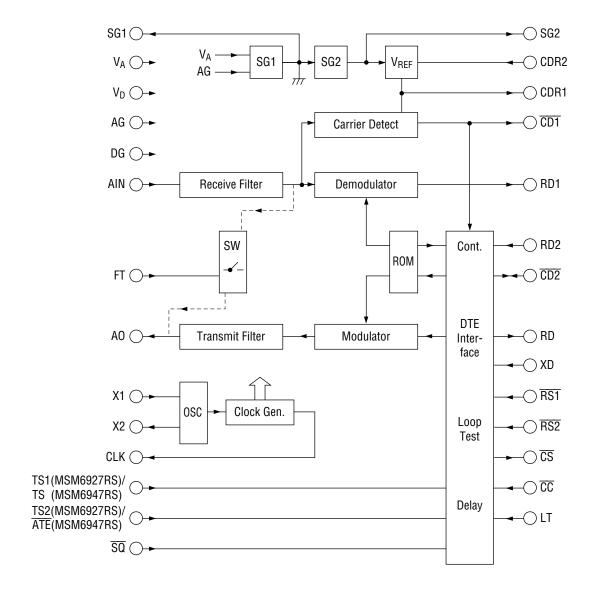

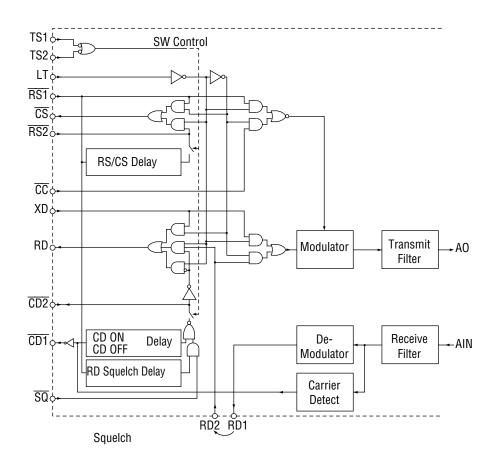

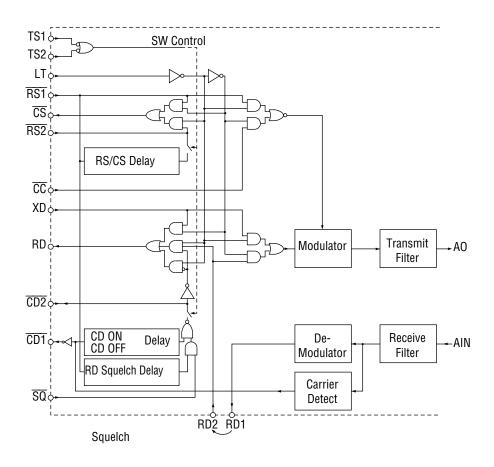

## **BLOCK DIAGRAM**

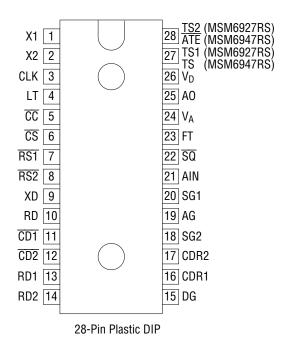

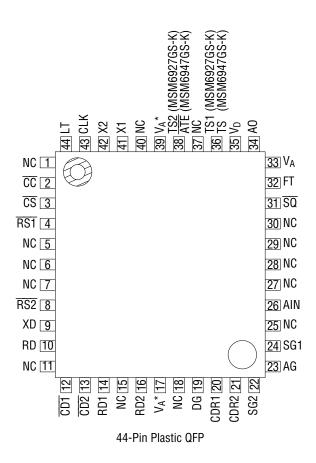

# **PIN CONFIGURATION (TOP VIEW)**

Note: All pin descriptions except No. 27 pin and No. 28 pin are same for both MSM6927RS and MSM6947RS.

Notes: All pin description except No. 36 pin and No. 28 pin are same for both MSM6927GS-K and MSM6947GS-K.

\*: Both No. 17 pin and No. 39 pin are set to be at  $V_A$  level by setting No. 33 pin at  $V_A$  level.

NC: No connect pin

## **PIN DESCRIPTIONS**

## **Power**

| Mana           | Pin | No.  | 1/0 | Description                                         |  |

|----------------|-----|------|-----|-----------------------------------------------------|--|

| Name           | RS  | GS-K | I/O | Description                                         |  |

| DG             | 15  | 19   | _   | Ground reference of V <sub>D</sub> (digital ground) |  |

| AG             | 19  | 23   | _   | Ground reference of V <sub>A</sub> (digital ground) |  |

| V <sub>A</sub> | 24  | 33   | _   | Supply voltage (+12 V nominal)                      |  |

| $V_{D}$        | 26  | 35   | _   | Supply voltage (+5 V nominal)                       |  |

## Clocks

| Nama | Pin | No.  | 1/0 | Description.                                                                                                                                                   |  |  |  |

|------|-----|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name | RS  | GS-K | I/O | Description                                                                                                                                                    |  |  |  |

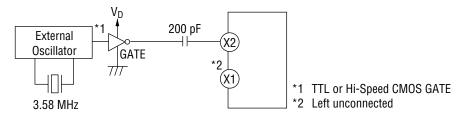

| X1   | 1   | 41   | _   | Master clock timing is provided by either a series resonant crystal (3.579545 MHz ±0.01%) connected across X1 and X2, or by an external TTL/CMOS clock driving |  |  |  |

| X2   | 2   | 42   |     | X2 with AC coupling. In this latter case, X1 is left unconnected.<br>See Fig. 10.                                                                              |  |  |  |

| CLK  | 3   | 43   | 0   | 873.9 Hz clock output. This clock is used to implement external delay circuits etc.                                                                            |  |  |  |

## Control

|                          | Pin | No.  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------|-----|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                     | RS  | GS-K | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LT                       | 4   | 44   | I   | Digital loop back test. During digital "High", any data sent on the $X_D$ pin will appear on the RD pin, and any data sent on the $\overline{RS1}$ pin will immediately appear on the $\overline{CS}$ pin. Any data demodulated from the received carrier on the $A_{IN}$ pin will be the modulated data to implement the transmitted carrier. In this case, sending the transmitted carrier to the phone line depends on the $\overline{CC}$ , but never on $\overline{RS1}$ . |

| $\overline{\mathtt{CC}}$ | 5   | 2    | I   | During digital loop back test, the data on this pin becomes a control signal for sending the transmitted carrier to the phone line in place of $\overline{RS1}$ .                                                                                                                                                                                                                                                                                                               |

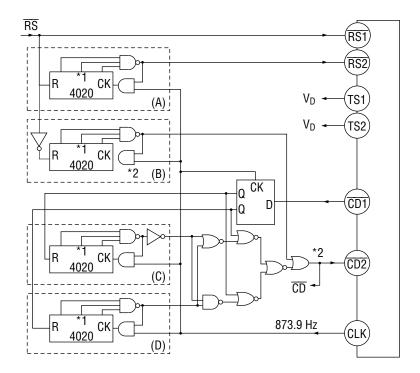

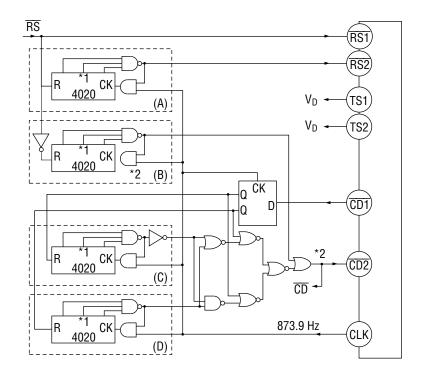

| RS2                      | 8   | 8    | I   | When an external circuit gives the RS/CS delay time which is not within the device as required, this pin should be connected to the external circuit output. See Fig. 11-1 or Fig. 11-2 for MSM6927, MSM6947 respectively.                                                                                                                                                                                                                                                      |

| CD1                      | 11  | 12   | 0   | The fast carrier detection output. This pin is internally connected to the input of the built-in carrier detect delay circuit. When an external delay circuit provides the delay time which is not within the device as required, the CD1 should be connected to the external circuit input. See Fig. 11-1 or Fig. 11-2 for MSM6927, MSM6947 respectively.                                                                                                                      |

| CD2                      | 12  | 13   | I/O | When an external circuit gives the carrier detect delay time which is not within the device as required, this pin becomes the input pin for the external circuit output signal. In other cases (when using the delay time within the device, the data on the TS1 (TS) or TS2 is not digital "High"), this pin becomes the Carrier detect signal output.                                                                                                                         |

| RD1                      | 13  | 14   | 0   | The RD1 data is demodulated data from the received carrier and the RD2 is the input of the following logic circuits referred to in Fig. 12-1and Fig. 12-2. for MSM6927 and MSM6947, respectively Usually, the RD1 data is input directly to RD2. In some                                                                                                                                                                                                                        |

| RD2                      | 14  | 16   | I   | cases, as input data to RD2, the data that is controlled by NCU (Network control unit) etc. may be required in stead of the RD1 data.                                                                                                                                                                                                                                                                                                                                           |

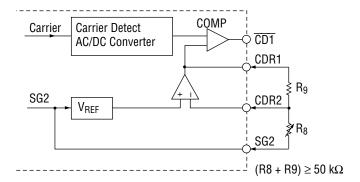

| CDR1                     | 16  | 20   | 0   | These two pins are the output (CRD1) and inverting input (CDR2) of the buffer operational amplifier of which the noninverting input is connected to the built-in voltage reference, stabilized to variations in the supply voltage and temperature. See Fig. 13. An adequate carrier-detect level can be set by selecting the ratio of                                                                                                                                          |

| CDR2                     | 17  | 21   | I   | $R_8$ to $R_9$ . Therefore, the loss in the received carrier level by phone-line transformer can be compensated by adjusting the ratio of $R_8$ to $R_9$ . $R_8$ + $R_9$ should be greater than 50 k $\Omega$ .                                                                                                                                                                                                                                                                 |

| SQ                       | 22  | 31   | I   | When the data rate is 1200 bps and in half duplex mode on two-wire facilities, the delay function called as receiver-squelch is required. In case of four wire facilities, this function is not usually required. When a digital "High" is input to the $\overline{SQ}$ pin, this function is omitted.                                                                                                                                                                          |

| FT                       | 23  | 32   | I   | This pin may be used for device tests only. During digital "High", the A <sub>0</sub> pin will be connected to receiving filter output instead of transmitting filter output.                                                                                                                                                                                                                                                                                                   |

Both MSM6927RS (or GS-K) and MSM6947RS (or GS-K) have 28 (or 44) pins. The pin descriptions for these 28 (or 44) pins are same except those for No. 27 (or No. 36) pin and No. 28 (or No. 38). The pin descriptions for No. 27 (or No. 36) pin and No. 28 (or No. 38) pin are described as follows.

#### MSM6927

| Nome | Pin | No.  | 1/0 | Decembries                                                                                                                                                                                                                                                                                                             |  |

|------|-----|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name | RS  | GS-K | I/O | Description                                                                                                                                                                                                                                                                                                            |  |

| TS1  | 27  | 36   | Ι   | RS/CS delay and carrier detect delay options referred to chapter about timing characteristics are selected by TS1 and TS2 inputs. Be careful that each delay can not be individually selected. If another delay time than the ones within the                                                                          |  |

| TS2  | 28  | 38   | I   | device are required as an option, input a digital "High" to the TS1 and TS2 pin and implement the external delay circuits to obtain the desired delay characteristics. In this case, the CD2 pin becomes not only the input for the external circuit output signal, but also the Carrier detect output. See Fig. 11-1. |  |

## MSM6947

| M    | Pin | No.  | .,, | December 1                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|-----|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name | RS  | GS-K | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TS   | 27  | 36   | I   | When a digital "Low" is input to the TS pin, the built-in RS/CS, carrier detect and receiver-squelch delay are provided. If another delay time is required, it can be implemented by inputting a digital "High" to this pin and incorporates the external delay circuits. In this case, the $\overline{\text{CD2}}$ pin becomes not only the input for the external circuit output signal, but also the Carrier detect output. See Fig. 11-2. |

| ĀTĒ  | 28  | 38   | I   | Answer tone enable input. When a digital "Low" is input to this pin and the $\overline{RS1}$ pin is in the digital "Low" level, the Answer Tone (to 2025 Hz) is sent over the phone line via the $A_0$ pin.                                                                                                                                                                                                                                   |

# Input/Output

| N               | Pin         | No.  | .,, | D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|-------------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name            | RS          | GS-K | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <u>CS</u>       | 6           | 3    | 0   | Clear to send signal output. The digital "High" level indicates the "OFF" state and digital "Low" indicates the "ON" state. This output goes "Low" at the end of a delay (RS/CS delay) initiated when $\overline{\text{RS1}}$ (Request to send) goes "Low".                                                                                                                                                                                                                                                     |

| RS1             | 7           | 4    | I   | Request to send signal input. The digital "High" level indicates the "OFF" state.  The digital "Low" level indicates the "ON" state and instructs the modem to enter the transmit mode. This input must remain "Low" for the duration of data transmission. "High" turns the transmitter off.                                                                                                                                                                                                                   |

| XD              | 9           | 9    | ı   | This is digital data to be modulated and transmitted via $A_0$ . Digital "High" will be transmitted as "Mark". Digital "Low" will be transmitted as "Space". No signal appears at $A_0$ unless $\overline{RS1}$ is "Low".                                                                                                                                                                                                                                                                                       |

| RD              | 10          | 10   | 0   | Digital data demodulated from A <sub>IN</sub> is serially available at this output. Digital "High" indicates "Mark" and digital "Low" indicates "Space". For example, under the following condition, this output is forced to be "Mark" state because the data may be invalid.  • When CD2 (Carrier detect) is in the "OFF" state.  • When SQ is in digital "Low" (two-wire facilities) and RS1 is in the "ON" state.  • During the receive data squelch delay at half duplex operation on two wire facilities. |

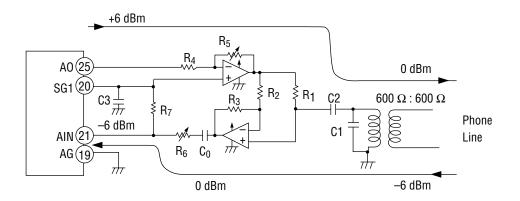

| SG2             | 18          | 22   | 0   | The SG1 and ST2 are built-in analog signal grounds. SG2 is used only for Carrier detect function. The DC voltage of SG1 is approximately 6 V, so the analog line interface must be implemented by AC coupling. See Fig. 9. To make                                                                                                                                                                                                                                                                              |

| SG1             | SG1 20 24 0 |      | 0   | impedance lower and ensure the device performance, it is necessary to put bypass capacitors on SG1 and SG2 in close physical proximity to the device.                                                                                                                                                                                                                                                                                                                                                           |

| A <sub>IN</sub> | 21          | 26   | I   | This is the input for the analog signal from the phone line. The modem extracts the information in this modulated carrier and converts it into a serial data stream for presentation at RD output.                                                                                                                                                                                                                                                                                                              |

| A <sub>0</sub>  | 25          | 34   | 0   | This analog output is the modulated carrier to be conditioned and sent over the phone line.                                                                                                                                                                                                                                                                                                                                                                                                                     |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter             |                      | Symbol          | Condition                   | Rating                       | Unit |

|-----------------------|----------------------|-----------------|-----------------------------|------------------------------|------|

| Dowar Cupply Voltage  |                      | VA              |                             | –0.3 to 15                   |      |

| Power Supply Voltage  |                      | V <sub>D</sub>  | Ta = 25°C                   | -0.3 to 7                    | V    |

| Analog Input Voltage  | log Input Voltage *1 |                 | With respect<br>to AG or DG | -0.3 to V <sub>A</sub> + 0.3 |      |

| Digital Input Voltage | *2                   | V <sub>ID</sub> |                             | -0.3 to V <sub>D</sub> + 0.3 |      |

| Operating Temperature |                      | T <sub>op</sub> | _                           | 0 to +70                     | °C   |

| Storage Temperature   | Storage Temperature  |                 | _                           | -55 to 150                   |      |

<sup>\*3</sup> CD2 is I/O terminal

## RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol          | Condition                            | Min. | Тур.     | Max. | Unit |

|-----------------------|-----------------|--------------------------------------|------|----------|------|------|

|                       | VA              | With respect to AG                   | 10.8 | 12.0     | 13.2 |      |

| Power Supply Voltage  | VD              | With respect to DG                   | 4.75 | 5.00     | 5.25 | V    |

|                       | AG, DG          | _                                    | _    | 0        | _    |      |

| Operating Temperature | T <sub>op</sub> | _                                    | 0    | _        | 70   | °C   |

| CRYSTAL               | _               | _                                    | _    | 3.579545 | _    | MHz  |

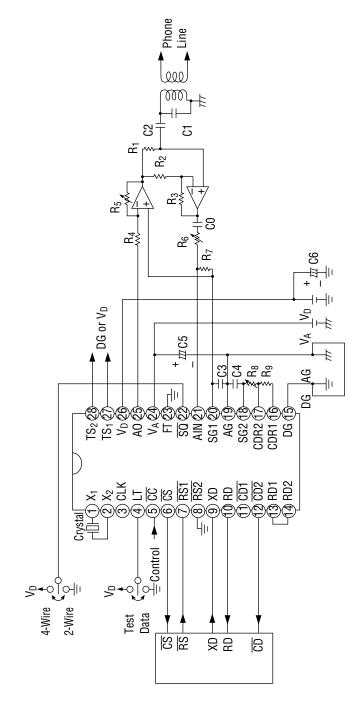

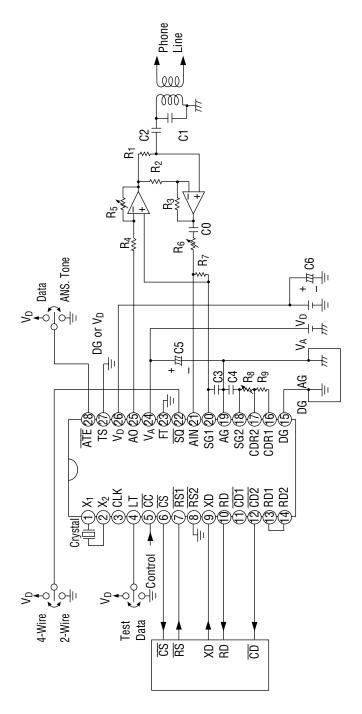

| R <sub>1</sub>        | _               | Transformer impedance = $600 \Omega$ | _    | 600      | _    | Ω    |

| R <sub>2</sub>        | _               |                                      | _    | 51       | _    |      |

| R <sub>3</sub>        | _               |                                      | _    | 51       | _    |      |

| R <sub>4</sub>        | _               |                                      | _    | 51       | _    |      |

| R <sub>5</sub>        | _               |                                      | _    | 51       | _    | kΩ   |

| R <sub>6</sub>        | _               | _                                    | _    | 51       | _    |      |

| R <sub>7</sub>        | _               |                                      | _    | 51       | _    |      |

| R <sub>8</sub>        | _               |                                      | _    | 33       | _    |      |

| R <sub>9</sub>        | _               |                                      | _    | 51       | _    |      |

| $C_0, C_1$            | _               |                                      | _    | 0.047    | _    |      |

| C <sub>2</sub>        | _               |                                      | _    | 2.2      | _    |      |

| C <sub>3</sub>        | _               |                                      | 22   | _        | _    |      |

| C <sub>4</sub>        |                 | _                                    | 0.01 | _        | _    | μF   |

| C <sub>5</sub>        | _               |                                      | _    | 10       | _    |      |

| C <sub>6</sub>        |                 |                                      | _    | 10       | _    |      |

Application circuits using above conditions are provided in Fig. 8.

## **ELECTRICAL CHARACTERISTICS**

## **DC** and Digital Interface Characteristics

$(V_A = 12 \text{ V} \pm 10\%, V_D = 5 \text{ V} \pm 5\%, Ta = 0 \text{ to } 70^{\circ}\text{C})$

| Parameter                | Sy   | ymbol           | Condition                  | Min.     | Тур. | Max.    | Unit |

|--------------------------|------|-----------------|----------------------------|----------|------|---------|------|

| Davis Oraș la Oraș de    |      | lΑ              | Ordinary                   | _        | 7.5  | 15.0    | 0    |

| Power Supply Current     |      | I <sub>D</sub>  | operation                  | _        | 1.0  | 2.0     | mA   |

| lowest Lealing Occurrent | *1 — | I <sub>IL</sub> | $V_I = 0 V$                | -10      |      | 10      |      |

| Input Leakage Currnet    | ^    | I <sub>IH</sub> | $V_I = V_D$                | -10      | _    | 10      | μΑ   |

| Input Voltage            | *4   | V <sub>IL</sub> | _                          | 0        | _    | 0.8     |      |

| Input Voltage            | *1   | V <sub>IH</sub> | _                          | 2.2      |      | $V_{D}$ | V    |

| Output Valtage           | *9   | V <sub>OL</sub> | $I_{0L} = 1.6 \text{ mA}$  | 0        | _    | 0.4     | V    |

| Output Voltage           | ~    | V <sub>OH</sub> | $I_{OH} = 400 \mu\text{A}$ | 0.8 × VD |      | $V_{D}$ | 1    |

<sup>\*1</sup> LT,  $\overline{\text{CC}}$ ,  $\overline{\text{RS1}}$ ,  $\overline{\text{RS2}}$ , XD,  $\overline{\text{CD2}}$ , RD2,  $\overline{\text{SQ}}$ , FT, T<sub>S1</sub> (TS), T<sub>S2</sub> ( $\overline{\text{ATE}}$ )

<sup>\*2</sup> CLK, <del>CS</del>, RD, <del>CD1</del>, <del>CD2</del>, RD1

<sup>\*3</sup>  $\overline{\text{CD2}}$  is I/O terminal.

# **Analog Interface Characteristics**

## 1. MSM6927

Transmit carrier out (A<sub>O</sub>)

$(V_A = 12 \text{ V } \pm 10\%, V_D = 5 \text{ V } \pm 5\%, Ta = 0 \text{ to } 70^{\circ}\text{C})$

| Parameter                                         |                 | Symbol           | Condition                           | Min.               | Тур.            | Max.                | Unit   |  |

|---------------------------------------------------|-----------------|------------------|-------------------------------------|--------------------|-----------------|---------------------|--------|--|

| Carrier Fraguency                                 | Mark<br>1       | f <sub>M</sub>   | f. 2 570545 MLI¬                    | 1290               | 1300            | 1310                | Шт     |  |

| Carrier Frequency                                 | Space<br>0      | f <sub>S</sub>   | f <sub>CRYSTAL</sub> = 3.579545 MHz | 2090               | 2100            | 2100                | Hz     |  |

| Output Resistance                                 |                 | R <sub>OXA</sub> | _                                   | _                  | _               | 200                 | Ω      |  |

| Load Resistance                                   | Load Resistance |                  | _                                   | 50                 | _               | _                   | kΩ     |  |

| Load Capacitance                                  |                 | C <sub>LXA</sub> | _                                   | _                  | _               | 100                 | pF     |  |

| Transmit Level                                    |                 | V <sub>OXA</sub> | _                                   | 4                  | 6               | 8                   | *1 dBm |  |

| Output Offset Voltage                             |                 | V <sub>OSX</sub> | _                                   | $\frac{V_A}{2}$ -1 | $\frac{V_A}{2}$ | $\frac{V_A}{2}$ + 1 | V      |  |

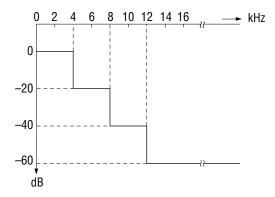

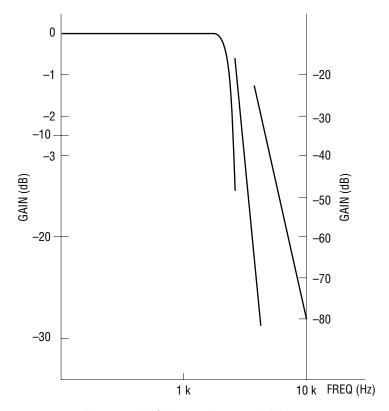

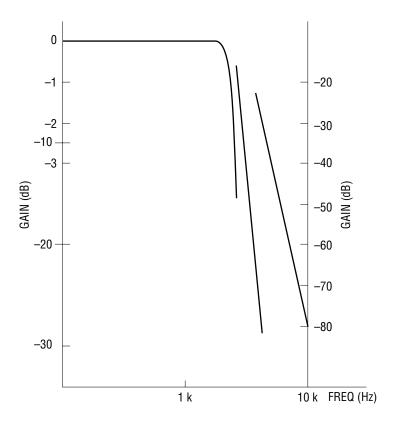

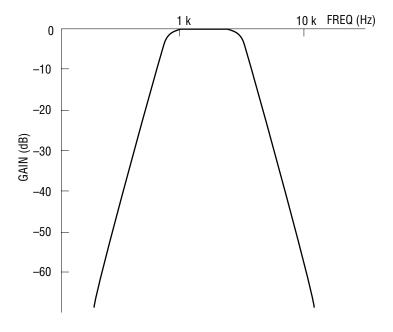

| Out-of-Band Energy<br>(Referred to Carrier Level) |                 | E <sub>0X</sub>  | C <sub>1</sub> = 0.047 μF           | R                  | efer to Fig.    | 1                   | dB     |  |

# Receive carrier input $(A_{IN})$

| Parameter                  | Symbol | Condition           | Min.                                     | Тур. | Max. | Unit |        |

|----------------------------|--------|---------------------|------------------------------------------|------|------|------|--------|

| Input Resistance           |        | R <sub>IRA</sub>    | _                                        | 100  | _    | _    | kΩ     |

| Receive Signal Level Range |        | V <sub>IRA</sub>    | _                                        | -48  | _    | -6   |        |

| Camian Datast Lavel        | ON     | V <sub>CD</sub> ON  | $R_8 = 33 \text{ k}\Omega ^*2$           | _    | _    | -43  | *1 dBm |

| Carrier Detect Level       | OFF    | V <sub>CD</sub> OFF | $R_9 = 51 \text{ k}\Omega$               | -48  | _    | _    |        |

| Carrier Detect Hysteresis  |        | Hys                 | V <sub>CD</sub> ON – V <sub>CD</sub> OFF | 2    | _    | _    | dB     |

## Receive filter

| Parameter              | Symbol          | Condition       | Min. | Тур. | Max. | Unit |

|------------------------|-----------------|-----------------|------|------|------|------|

| Group Delay Distortion | D <sub>DL</sub> | 1100 to 2300 Hz | _    | 210  | _    | μS   |

Notes: \*1 0 dBm = 0.775 Vrms

\*2 The resistor values are typical

Figure 1 MSM6927 Out-of-Band Energy Referred to Carrier Level ( $C_1$  = 0.047  $\mu F$ )

Figure 2 MSM6927 Transmit Filter

Figure 3 MSM6927 Receive Filter

## 2. MSM6947

Transmit carrier out  $(A_O)$

$(V_A = 12 \ V \pm 10\%, \ V_D = 5 \ V \pm 5\%, \ Ta = 0 \ to \ 70 ^{\circ}C)$

| Parameter                                         |            | Symbol           | Condition                           | Min.               | Тур.            | Max.                | Unit   |

|---------------------------------------------------|------------|------------------|-------------------------------------|--------------------|-----------------|---------------------|--------|

| Carrier Frequency                                 | Mark<br>1  | f <sub>M</sub>   |                                     | 1190               | 1200            | 1210                |        |

| Carrier Frequency                                 | Space<br>0 | f <sub>S</sub>   | f <sub>CRYSTAL</sub> = 3.579545 MHz | 2190               | 2200            | 2210                | Hz     |

| Answer Tone Frequency                             |            | f <sub>A</sub>   | ATE = "0"                           | 2019               | 2025            | 2031                |        |

| Output Resistance                                 |            | R <sub>OXA</sub> | _                                   |                    |                 | 200                 | Ω      |

| Load Resistance                                   |            | $R_{LXA}$        | _                                   | 50                 | _               | _                   | kΩ     |

| Load Capacitance                                  |            | C <sub>LXA</sub> | _                                   | _                  | _               | 100                 | pF     |

| Transmit Level                                    |            | V <sub>OXA</sub> | _                                   | 4                  | 6               | 8                   | *1 dBm |

| Output Offset Voltage                             |            | V <sub>OSX</sub> | _                                   | $\frac{V_A}{2}$ -1 | $\frac{V_A}{2}$ | $\frac{V_A}{2}$ + 1 | V      |

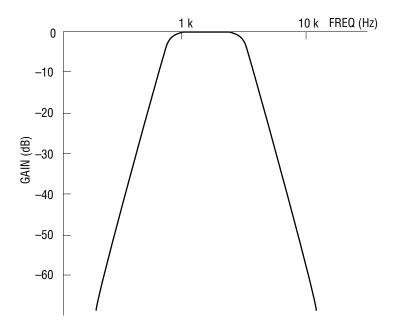

| Out-of-Band Energy<br>(Referred to Carrier Level) |            | E <sub>0X</sub>  | $C_1 = 0.047 \ \mu F$               | Refer to Fig. 4    |                 | 4                   | dB     |

# Receive carrier input $(A_{IN})$

| Parameter                  |     | Symbol              | Condition                                | Min. | Тур. | Max. | Unit   |

|----------------------------|-----|---------------------|------------------------------------------|------|------|------|--------|

| Input Resistance           |     | R <sub>IRA</sub>    | _                                        | 100  | _    | _    | kΩ     |

| Receive Signal Level Range |     | V <sub>IRA</sub>    | _                                        | -48  | _    | -6   |        |

| Courier Detect Level       | ON  | V <sub>CD</sub> ON  | $R_8 = 33 \text{ k}\Omega ^*2$           | _    | _    | -43  | *1 dBm |

| Carrier Detect Level       | OFF | V <sub>CD</sub> OFF | $R_9 = 51 \text{ k}\Omega$               | -48  | _    | _    |        |

| Carrier Detect Hysteresis  |     | Hys                 | V <sub>CD</sub> ON – V <sub>CD</sub> OFF | 0.5  | _    | _    | dB     |

## Receive Filter

| Parameter Symbol       |                 | Condition       | Min. | Тур. | Max. | Unit |

|------------------------|-----------------|-----------------|------|------|------|------|

| Group Delay Distortion | D <sub>DL</sub> | 1100 to 2300 Hz | _    | 210  | _    | μS   |

Notes: \*1 0 dBm = 0.775 Vrms

\*2 The resistor values are typical

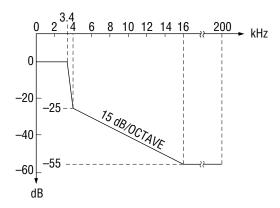

Figure 4 MSM6947 Out-of-Band Energy Referred to Carrier Level (C<sub>1</sub> = 0.047  $\mu$ F)

Figure 5 MSM6947 Transmit Filter

Figure 6 MSM6947 Receive Filter

## **Demodulated Bit Characteristics**

$(V_A = 12 \text{ V } \pm 10\%, V_D = 5 \text{ V } \pm 5\%, Ta = 0 \text{ to } 70^{\circ}\text{C})$

| Parameter                   | Symbol | Condition                                                                 |      |       | Min. | Тур.             | Max. | Unit |

|-----------------------------|--------|---------------------------------------------------------------------------|------|-------|------|------------------|------|------|

| Peak Intersymbol Distortion | ID     | Back-to-back over input signal range –6 to –40 dBm. 511-bit test pattern. |      |       | _    | 9                | _    | %    |

| Bit Error Rate              | 250    | Back-to-backwith<br>0.3 to 3.4 kHz<br>flat noise.                         | 0.51 | 8 dB  | _    | 10 <sup>-3</sup> | _    |      |

|                             | BER    | Receive signal<br>level –25 dBm.<br>511-bit test pattern                  | S/N  | 11 dB | _    | 10 <sup>-5</sup> | _    |      |

## **Timing Characteristics**

## 1. MSM6927

$(V_A = 12 \text{ V} \pm 10\%, V_D = 5 \text{ V} \pm 5\%, Ta = 0 \text{ to } 70^{\circ}\text{C})$

|                                 |                     |                                                          |     | <u>.                                    </u> |      |                      | · · · · · · · · · · · · · · · · · · ·                                                 |      |

|---------------------------------|---------------------|----------------------------------------------------------|-----|----------------------------------------------|------|----------------------|---------------------------------------------------------------------------------------|------|

| Parameter                       | Symbol              | Condition                                                | TS2 | TS1                                          | Min. | Тур.                 | Max.                                                                                  | Unit |

|                                 |                     |                                                          | 0   | 0                                            | 195  | 200                  | 205                                                                                   |      |

| RS/CS Delay Time                | T <sub>RC</sub> ON  | RS1 = "0"                                                | 0   | 1                                            | 25   | 30                   | 35                                                                                    |      |

|                                 |                     | $\rightarrow \overline{\text{CS}} = "0"$                 | 1   | 0                                            | 65   | 70                   | 75                                                                                    |      |

|                                 |                     |                                                          | 1   | 1                                            | Exte | rnal delay t         | imer                                                                                  |      |

|                                 | T <sub>RC</sub> OFF | $\overline{RS1} = "1"$ $\rightarrow \overline{CS} = "1"$ | *   | *                                            | 0    | _                    | 0.5                                                                                   |      |

| CD/ON Delay Time                |                     |                                                          | 0   | 0                                            | 10   | _                    | 25                                                                                    |      |

|                                 | _ ON                |                                                          | 0   | 1                                            | 10   | _                    | 25                                                                                    |      |

|                                 | T <sub>CD</sub> ON  | <b>-</b>                                                 | 1   | 0                                            | 10   | _                    | 25                                                                                    |      |

|                                 |                     |                                                          | 1   | 1                                            | Exte | External delay timer |                                                                                       |      |

|                                 |                     |                                                          | 0   | 0                                            | 5    | _                    | 15                                                                                    |      |

| CD/OFF Doloy Timo               | T. 0E               |                                                          | 0   | 1                                            | 5    | _                    | 200 205 30 35 70 75 delay timer  0.5 25 25 delay timer  15 15 delay timer  10 150 155 |      |

| CD/OFF Delay Time               | T <sub>CD</sub> OF  | _                                                        | 1   | 0                                            | 5    | _                    | 15                                                                                    |      |

|                                 |                     |                                                          | 1   | 1                                            | Exte | rnal delay t         | imer                                                                                  |      |

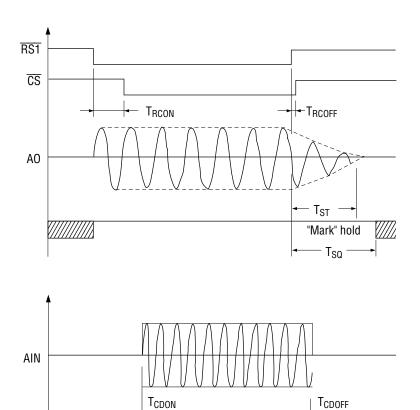

| Soft Turn-OFF Time              | T <sub>ST</sub>     | _                                                        | *   | *                                            | _    | 10                   | _                                                                                     |      |

| Receive Data Squelch Delay Time |                     | <del>SQ</del> = "0"                                      | 0   | 0                                            | 145  | 150                  | 155                                                                                   |      |

|                                 | _                   | RS1 = "1"                                                | 0   | 1                                            | 145  | 150                  | 155                                                                                   |      |

|                                 | T <sub>SQ</sub>     | → RD = "1"                                               | 1   | 0                                            | 35   | 40                   | 45                                                                                    |      |

|                                 |                     | Hold                                                     | 1   | 1                                            | Exte | rnal delay t         | imer                                                                                  |      |

Refer to Fig. 7

Notes: \*: Irrespective of I/O condition

## 2. MSM6947

$(V_A = 12 \text{ V} \pm 10\%, V_D = 5 \text{ V} \pm 5\%, Ta = 0 \text{ to } 70^{\circ}\text{C})$

| Parameter                       | Symbol              | Condition                                                | TS | Min.  | Тур.                 | Max.                                  | Unit |  |  |

|---------------------------------|---------------------|----------------------------------------------------------|----|-------|----------------------|---------------------------------------|------|--|--|

| RS/CS Delay Time                | T <sub>RC</sub> ON  | RS1 = "0"                                                | 0  | 175   | 180                  | 185                                   |      |  |  |

|                                 | I KC OM             | $\rightarrow \overline{\text{CS}} = "0"$                 | 1  | Exte  | rnal delay t         | imer                                  |      |  |  |

|                                 | T <sub>RC</sub> OFF | $\overline{RS1} = "1"$ $\rightarrow \overline{CS} = "1"$ | *  | 0     | _                    | 0.5                                   |      |  |  |

| OD /ON Dalay Time               | T ON                |                                                          | 0  | 15    | _                    | <u> </u>                              |      |  |  |

| CD/ON Delay Time                | T <sub>CD</sub> ON  | _                                                        | 1  | Exte  | External delay timer |                                       |      |  |  |

| OD/OFF Delevi Times             | т ог                |                                                          | 0  | 10    | _                    | 20                                    |      |  |  |

| CD/OFF Delay Time               | T <sub>CD</sub> OF  | 1 External delay timer                                   |    |       |                      |                                       |      |  |  |

| Soft Turn-OFF Time              | T <sub>ST</sub>     | _                                                        | *  | _     | 10                   | _                                     |      |  |  |

|                                 |                     | <del>SQ</del> = "0"                                      | 0  |       | 150                  |                                       |      |  |  |

| Receive Data Squelch Delay Time | _                   | RS1 = "1"                                                | 0  |       | 100                  | _                                     |      |  |  |

|                                 | T <sub>SQ</sub>     | → RD = "1"                                               | 4  | Eveto | rnal dalay t         | — 35 I delay timer — 20 I delay timer |      |  |  |

|                                 |                     | Hold                                                     | 1  | Exte  | rnai delay t         | IIIIei                                |      |  |  |

Refer to Fig. 8

Notes: \*: Irrespective of I/O condition

+: Reserved

## **TIMING DIAGRAM**

CD2

Figure 7 MSM6927/6947 Timing Diagram

$\mathsf{T}_{\mathsf{CDOFF}}$

## **APPLICATION CIRCUIT**

1. MSM6927RS

Notes: 1. The crystal should be wired in close physical proximity to the device.

- 2. High level signals should not be routed next to low level signals.

- 3. Bypass capacitors on  $V_A$ , SG1, and SG2 should be as close to the device as possible.

- 4. AG and DG should be connected as close to the system ground as possible.

Figure 8-1 Application Circuit Using MSM6927RS

## 2. MSM6947RS

Notes: 1. The crystal should be wired in close physical proximity to the device.

- 2. High level signals should not be routed next to low level signals.

- 3. Bypass capacitors on  $V_A$ , SG1, and SG2 should be as close to the device as possible.

- 4. AG and DG should be connected as close to the system ground as possible.

Figure 8-2 Application Circuit Using MSM6947RS

Figure 9 MSM6927RS/MSM6947RS Application

| $C_0, C_1$     | 0.047 μF | R <sub>2</sub> | 51 kΩ                                  | R <sub>6</sub> | (51 kΩ) Receive signal level          |

|----------------|----------|----------------|----------------------------------------|----------------|---------------------------------------|

| $C_2$          | 2.2 μF   | R <sub>3</sub> | 51 kΩ                                  | R <sub>7</sub> | 51 kΩ                                 |

| $C_3$          | 1 μF     | R <sub>4</sub> | 51 kΩ                                  | R <sub>8</sub> | (33 k $\Omega$ ) Carrier detect level |

| R <sub>1</sub> | 600 Ω    | R <sub>5</sub> | (51 k $\Omega$ ) Transmit signal level | R <sub>9</sub> | 51 kΩ                                 |

Note: The signal level on the  $A_{\mbox{\footnotesize{IN}}}$  pin should not exceed –6 dBm.

**External Oscillator Connection**

Figure 10

(A) RS/CS delay, (B) Receive-squelch delay, (C) CD/ON delay, (D) CD/OFF delay Note: Supply voltage equals V<sub>D</sub> for all gates.

- \*1: The desired delay can be realized by selecting the appropriate bits from 4020's outputs. The number of the bits is not always 3. Each delay can be set differently from built-in delays.

- \*2: In case that the Receiver-squelch delay is unnecessary, circuit (B) and this OR gate should be omitted and the output of the NOR gate should be connected to CD2 directly.

Figure 11-1 MSM6927 External Delay Connection

(A) RS/CS delay, (B) Receive-squelch delay, (C) CD/ON delay, (D) CD/OFF delay Note: Supply voltage equals  $V_D$  for all gates.

- \*1: The desired delay can be realized by selecting the appropriate bits from 4020's outputs. The number of the bits is not always 3. Each delay can be set differently from built-in delays.

- \*2: In case that the Receiver-squelch delay is unnecessary, circuit (B) and this OR gate should be omitted and the output of the NOR gate should be connected to CD2 directly.

Figure 11-2 MSM6947 External Delay Connection

Figure 12-1 MSM6927 Equivalent Logic Interface of the Integrated Modem

Figure 12-2 MSM6947 Equivalent Logic Interface of the Integrated Modem

Figure 13 External Resistor Connection for the Setting of Carrier Detect Level

## **PACKAGE DIMENSIONS**

(Unit: mm)

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).