# **OKI** Semiconductor

# This version: Jun. 2001 Previous version: Mar. 2001

# MSM6794

#### DOT MATRIX LCD DRIVER WITH 128-CHANNEL RAM

#### **GENERAL DESCRIPTION**

The MSM6794 is a dot matrix graphic liquid crystal display LSI device to display bit maps. It drives an LCD panel for dot matrix graphic display under the control of a 4- or 8-bit microcomputer.

All necessary functions for driving a bit map type LCD are built in on one chip. Therefore, by using the MSM6794, a bit map type dot matrix graphic liquid crystal display system can be implemented with a small number of chips.

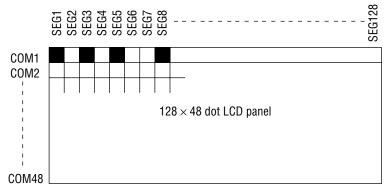

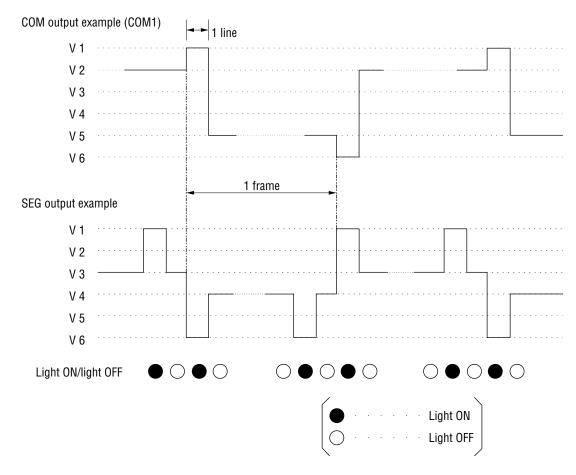

Since 1-bit data of the display RAM corresponds to the light-on/off of 1-dot of the LCD panel (bit map system), a flexible display, including kanji display, is possible. One chip comprises a graphic display system of a maximum of 128×48 dots. This display can be expanded by using multiple chips.

The MSM6794 uses CMOS process. Since it is an internal RAM type, the MSM 6794 features low power consumption, and is suited to display for battery-driven portable equipment.

#### **FEATURES**

Segment outputs

Common outputs

Display duty

Maximum of 128

Maximum of 48

1/33, 1/41, 1/44, 1/48

• Display duty : 1/33, 1/41, 1/44

• Bit map type internal RAM : 6,144 bits (128×48 bits)

• Display data I/F : 8-bit parallel/serial switchable

• Standby function by program

• LCD drive bias resistor (externally connected)

Built-in voltage multiplier circuitLOGIC voltage

$\bullet$  LCD driving voltage  $$:V_{BI}\,5$$  to 12V (positive voltage)

• Low current consumption : Maximum of 10μA (in standby mode)

: 2.7 to 5.5V

• Number of pads : 224

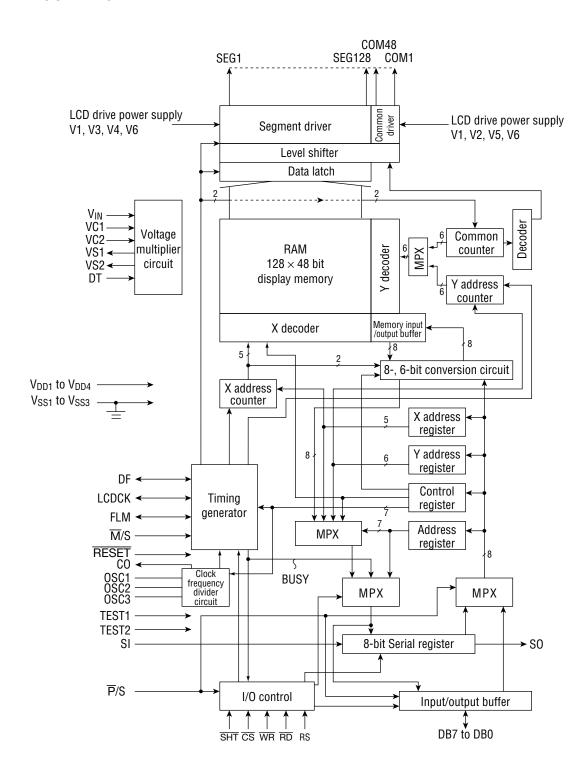

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter              | Symbol           | Condition                              | Rating                       | Unit | Applicable Pins                         |  |

|------------------------|------------------|----------------------------------------|------------------------------|------|-----------------------------------------|--|

| Supply voltage         | V <sub>DD</sub>  | Ta=25°C,                               | -0.3 to +7                   | V    | V <sub>DD1-4</sub> , V <sub>SS1-3</sub> |  |

|                        |                  | V <sub>DD1-4</sub> -V <sub>SS1-3</sub> |                              |      |                                         |  |

| Bias voltage           | V <sub>BI</sub>  | Ta=25°C,V1-V6                          | -0.3 to +14                  | V    | V1, V6                                  |  |

| Voltage multiplication | V                | V <sub>IN</sub> -V <sub>SS1-3</sub> *2 | -0.3 to +7                   | V    | V V                                     |  |

| reference voltage      | V <sub>IN</sub>  | V <sub>IN</sub> -V <sub>SS1-3</sub> *3 | -0.3 to +4.6                 | V    | V <sub>IN</sub> , V <sub>SS1</sub> -3   |  |

| Input voltage          | VI               | Ta=25°C                                | -0.3 to V <sub>DD</sub> +0.3 | V    | All Inputs                              |  |

| Power dissipation      | PD               | _                                      | *1                           | mW   | _                                       |  |

| Storage temperature    | T <sub>STG</sub> | _                                      | -55 to +150                  | °C   | _                                       |  |

Ta: ambient temperature

#### RECOMMENDED OPERATING CONDITIONS

| Parameter               | Symbol          | Condition                              | Range                | Unit | Applicable Pins                         |  |

|-------------------------|-----------------|----------------------------------------|----------------------|------|-----------------------------------------|--|

| Supply voltage          | V <sub>DD</sub> | V <sub>DD1-4</sub> -V <sub>SS1-3</sub> | 2.7 to 5.5           | V    | V <sub>DD1-4</sub> , V <sub>SS1-3</sub> |  |

| Bias voltage            | V <sub>BI</sub> | V1–V6 1                                | 5 to 12              | V    | V1, V6                                  |  |

| Voltage multiplicatipon | W               | V <sub>IN</sub> -V <sub>SS1-3</sub>    | 1 to V <sub>DD</sub> | V    |                                         |  |

| reference voltage       | V <sub>IN</sub> | See Note 1 on p.6                      | 1 to 4               | V    | $V_{IN}, V_{SS1-3}$                     |  |

| Operating frequency     | f <sub>op</sub> | 2                                      | 270 to 500           | kHz  | OSC1                                    |  |

| Operating temperature   | T <sub>op</sub> | _                                      | -25 to +85           | °C   | _                                       |  |

- 1 For bias potential, V1 has the highest potential and V6 has the lowest potential. Use V6 at the same potential as  $V_{SS1}$  to  $V_{SS3}$ .

- 2 RC oscillation and external input clock frequency. When an RC oscillation circuit is configured, 1 is the only available frequency dividing ratio. If an external input clock is used, the available frequency dividing ratios are from 1 to 1/8.

- Clock frequency after dividing must be within this range.

- See "Control register (FCR)".

<sup>\*1</sup> Power dissipation depends on the heat radiation in a device attach condition. Set junction temperature to 150°C or lower.

<sup>\*2</sup> Ta = 25 °C; when doubler is used.

<sup>\*3</sup> Ta = 25°C; when tripler is used.

## **ELECTRICAL CHARACTERISTICS**

# DC Characteristics (1)

$(V_{DD}=2.7 \text{ to } 4.5V, V_{BI}=5 \text{ to } 12V, Ta=-25 \text{ to } +85^{\circ}C)$

| Parameter                              | Symbol           | Condition                                                               | Min.                       | Тур. | Max.               | Unit. | Applicable Pin                                      |

|----------------------------------------|------------------|-------------------------------------------------------------------------|----------------------------|------|--------------------|-------|-----------------------------------------------------|

| "H" input voltage 1                    | V <sub>IH1</sub> | _                                                                       | 0.8V <sub>DD</sub>         | _    | $V_{DD}$           | V     | 0SC1                                                |

| "H" input voltage 2                    | V <sub>IH2</sub> | _                                                                       | 0.8V <sub>DD</sub>         | _    | $V_{DD}$           | V     | DB0-7, LCDCK, FLM, DF                               |

| "H" input voltage 3                    | V <sub>IH3</sub> | _                                                                       | 0.8V <sub>DD</sub>         | _    | $V_{DD}$           | V     | Other input pins                                    |

| "L" input voltage 1                    | V <sub>IL1</sub> | _                                                                       | 0                          | _    | 0.2V <sub>DD</sub> | V     | OSC1                                                |

| "L" input voltage 2                    | V <sub>IL2</sub> | _                                                                       | 0                          | _    | 0.2V <sub>DD</sub> | V     | DB0-7, LCDCK, FLM, DF                               |

| "L" input voltage 3                    | V <sub>IL3</sub> | _                                                                       | 0                          | _    | 0.2V <sub>DD</sub> | Unit. | Other input pins                                    |

| "H" input current 1                    | I <sub>IH1</sub> | V <sub>I</sub> =V <sub>DD</sub>                                         | _                          | _    | 5                  | μА    | Input pins excluding<br>DB0-7, LCDCK,<br>FLM and DF |

| "H" input current 2                    | I <sub>IH2</sub> | V <sub>I</sub> =V <sub>DD</sub>                                         | <b>-</b> 5                 |      | 5                  | μΑ    | DB0-7, LCDCK, FLM, DF                               |

| "L" input current 1                    | l <sub>IL1</sub> | V <sub>I</sub> =0V                                                      | -5                         | _    | _                  | μА    | Input pins excluding<br>DB0-7, LCDCK,<br>FLM and DF |

| "L" input current 2                    | I <sub>IL2</sub> | V <sub>I</sub> =0V                                                      | <b>-</b> 5                 | _    | 5                  | μΑ    | DB0-7, LCDCK, FLM, DF                               |

| OFF leakage<br>current                 | l <sub>off</sub> | V <sub>I</sub> =V <sub>DD</sub> or 0V                                   | <b>-</b> 5                 | _    | 5                  | μΑ    | S0                                                  |

| "H" output voltage 1                   | V <sub>OH1</sub> | I <sub>0</sub> =-1.0mA                                                  | 0.9V <sub>DD</sub>         | _    | _                  | V     | CO, LCDCK, FLM, DF, SO                              |

| "H" output voltage 2                   | V <sub>OH2</sub> | I <sub>0</sub> =–1.0mA                                                  | 0.9V <sub>DD</sub>         |      | _                  | V     | DB0 to DB7                                          |

| "L" output voltage 1                   | V <sub>OL1</sub> | I <sub>0</sub> =1.0mA                                                   | _                          | _    | 0.1V <sub>DD</sub> | V     | CO, LCDCK, FLM, DF, SO                              |

| "L" output voltage 2                   | V <sub>OL2</sub> | I <sub>0</sub> =1.0mA                                                   | _                          | _    | 0.1V <sub>DD</sub> | ٧     | DB0 to DB7                                          |

| Multiplied voltage 1 Doubler output    | V <sub>DB</sub>  | I <sub>0</sub> =–500μA<br>f <sub>osc</sub> =350kHz                      | V <sub>IN</sub> ×2<br>-0.5 | _    |                    | V     | VS2                                                 |

| Multiplied voltage 2<br>Tripler output | V <sub>TR</sub>  | I <sub>0</sub> =–500μA<br>f <sub>osc</sub> =350kHz                      | V <sub>IN</sub> ×3<br>−1.0 | _    | _                  | V     | VS2                                                 |

| COM output resistance                  | R <sub>C</sub>   | I <sub>0</sub> =±50μΑ                                                   | _                          | _    | 10                 | kΩ    | COM1 to COM48                                       |

| SEG output resistance                  | R <sub>S</sub>   | I <sub>0</sub> =±20μA                                                   | _                          | _    | 20                 | kΩ    | SEG1 to SEG128                                      |

| Supply Current 1                       | I <sub>DD1</sub> | During display<br>External clock<br>f <sub>osc</sub> = 350kHz           | _                          |      | 450                | μΑ    | V <sub>DD</sub>                                     |

| Supply Current 2                       | I <sub>DD2</sub> | During display<br>Internal<br>oscillation<br>$f_{osc} = 350 \text{kHz}$ | _                          | 360  | 700                | μΑ    | V <sub>DD</sub>                                     |

| Supply Current 3                       | I <sub>DDS</sub> | During standby                                                          | _                          | _    | 10                 | μΑ    | V <sub>DD</sub>                                     |

| Oscillation frequency                  | f <sub>OSC</sub> | $R_{f}$ =18 $k\Omega$ $C_{f}$ =56 $pF$ See Note 3 on p.6                | 292                        | 350  | 437                | kHz   | OSC1, OSC2, OSC3                                    |

# DC Characteristics (2)

$(V_{DD}=4.5 \text{ to } 5.5 \text{V}, V_{BI}=5 \text{ to } 12 \text{V}, Ta=-25 \text{ to } +85^{\circ}\text{C})$

|                                        |                  |                                                                                                                      |                            | (*00 |                    |      |                                                     |

|----------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------|------|--------------------|------|-----------------------------------------------------|

| Parameter                              | Symbol           | Condition                                                                                                            | Min.                       | Тур. | Max.               | Unit | Applicable Pin                                      |

| "H" input voltage 1                    | V <sub>IH1</sub> | _                                                                                                                    | 0.8V <sub>DD</sub>         | _    | $V_{DD}$           | V    | OSC1                                                |

| "H" input voltage 2                    | V <sub>IH2</sub> | _                                                                                                                    | 0.8V <sub>DD</sub>         | _    | $V_{DD}$           | ٧    | DB0-7, LCDCK, FLM, DF                               |

| "H" input voltage 3                    | V <sub>IH3</sub> | _                                                                                                                    | 0.8V <sub>DD</sub>         | _    | $V_{DD}$           | ٧    | Other input pins                                    |

| "L" input voltage 1                    | V <sub>IL1</sub> | _                                                                                                                    | 0                          | _    | 0.2V <sub>DD</sub> | ٧    | OSC1                                                |

| "L" input voltage 2                    | V <sub>IL2</sub> | _                                                                                                                    | 0                          | _    | 0.2V <sub>DD</sub> | ٧    | DB0-7, LCDCK, FLM, DF                               |

| "L" input voltage 3                    | V <sub>IL3</sub> | _                                                                                                                    | 0                          | _    | 0.2V <sub>DD</sub> | ٧    | Other input pins                                    |

| "H" input current 1                    | I <sub>ІН1</sub> | V <sub>I</sub> =V <sub>DD</sub>                                                                                      | _                          | _    | 5                  | μА   | Input pins excluding<br>DB0-7, LCDCK,<br>FLM and DF |

| "H" input current 2                    | I <sub>IH2</sub> | V <sub>I</sub> =V <sub>DD</sub>                                                                                      | <b>-</b> 5                 | _    | 5                  | μΑ   | DB0-7, LCDCK, FLM, DF                               |

| "L" input current 1                    | l <sub>IL1</sub> | V <sub>I</sub> =0V                                                                                                   | -5                         | _    | _                  | μА   | Input pins excluding<br>DB0-7, LCDCK,<br>FLM and DF |

| "L" input current 2                    | I <sub>IL2</sub> | V <sub>I</sub> =0V                                                                                                   | <b>-</b> 5                 |      | 5                  | μΑ   | DB0-7, LCDCK, FLM, DF                               |

| OFF leakage<br>current                 | I <sub>off</sub> | V <sub>I</sub> =V <sub>DD</sub> /0V                                                                                  | <b>-</b> 5                 | _    | 5                  | μА   | S0                                                  |

| "H" output voltage 1                   | V <sub>OH1</sub> | I <sub>0</sub> =–1.5mA                                                                                               | 0.9V <sub>DD</sub>         | _    | _                  | V    | CO, LCDCK, FLM, DF, SO                              |

| "H" output voltage 2                   | V <sub>OH2</sub> | I <sub>0</sub> =–1.5mA                                                                                               | 0.9V <sub>DD</sub>         | _    | _                  | V    | DB0 to DB7                                          |

| "L" output voltage 1                   | V <sub>OL1</sub> | I <sub>0</sub> =1.5mA                                                                                                | _                          | _    | 0.1V <sub>DD</sub> | ٧    | CO, LCDCK, FLM, DF, SO                              |

| "L" output voltage 2                   | V <sub>0L2</sub> | I <sub>0</sub> =1.5mA                                                                                                | _                          | _    | $0.1V_{DD}$        | V    | DB0 to DB7                                          |

| Multiplied voltage 1<br>Doubler output | V <sub>DB</sub>  | I <sub>0</sub> =-500μA<br>f <sub>osc</sub> =350kHz                                                                   | V <sub>IN</sub> ×2<br>−0.5 | _    | _                  | V    | VS2                                                 |

| Multiplied voltage 2<br>Tripler output | V <sub>TR</sub>  | I <sub>0</sub> =-500μA<br>f <sub>osc</sub> =350kHz                                                                   | V <sub>IN</sub> ×3<br>−1.0 | _    | _                  | V    | VS2                                                 |

| COM output resistance                  | R <sub>C</sub>   | I <sub>0</sub> =±50μA                                                                                                | _                          | _    | 10                 | kΩ   | COM1 to COM48                                       |

| SEG output resistance                  | R <sub>S</sub>   | I <sub>0</sub> =±20μA                                                                                                | _                          | _    | 20                 | kΩ   | SEG1 to SEG128                                      |

| Supply Current 1                       | I <sub>DD1</sub> | During display<br>External clock<br>f <sub>osc</sub> = 350kHz                                                        | _                          | _    | 450                | μΑ   | V <sub>DD</sub>                                     |

| Supply Current 2                       | I <sub>DD2</sub> | During display<br>Internal<br>oscillation<br>f <sub>osc</sub> =350kHz                                                | _                          | 360  | 700                | μА   | V <sub>DD</sub>                                     |

| Supply Current 3                       | I <sub>DDS</sub> | During standby                                                                                                       | _                          | _    | 10                 | μА   | V <sub>DD</sub>                                     |

| Oscillation<br>frequency               | f <sub>OSC</sub> | $\begin{array}{c} R_{f}\text{=}22\text{k}\Omega \\ C_{f}\text{=}56\text{pF} \\ \text{See Note 3 on p.6} \end{array}$ | 292                        | 350  | 437                | kHz  | OSC1, OSC2, OSC3                                    |

Notes: 1. Voltage multiplication reference voltage is  $= V_{DD}$  maximum when the multiplied voltage is 12V or less.

The voltage multiplication reference voltage is 4V maximum when the multiplied voltage is 12V or more (tripler output).

Condition:  $f_{osc} = 350 \text{kHz}$

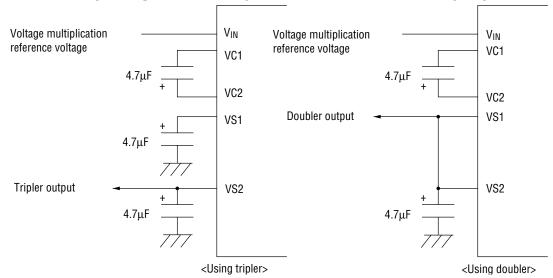

Voltage multiplier circuit configuration: connect as in the following diagram.

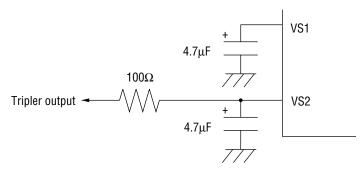

2. If the multiplied voltage output and bias power supply are directly connected, the voltage multiplier circuit operation may malfunction due to bias power supply noise. A countermeasure for noise is necessary, such as inserting a series resistor to prevent noise from entering multiplied voltage output (VS1, VS2).

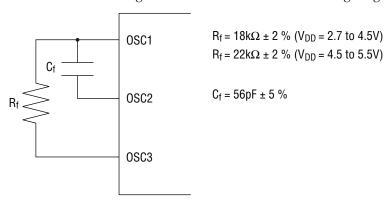

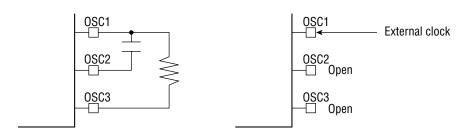

3. RC oscillation circuit configuration: connect as in the following diagram.

#### **AC Characteristics**

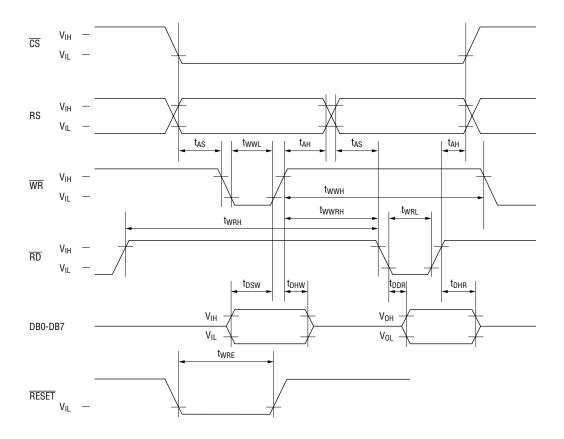

# Parallel interface (1)

$(V_{DD}=2.7 \text{ to } 4.5V, V_{BI}=5 \text{ to } 12V, Ta=-25 \text{ to } +85^{\circ}C)$

| Parameter                   | Symbol             | Condition            | Min | Max | Unit |

|-----------------------------|--------------------|----------------------|-----|-----|------|

| RD "H" level width          | t <sub>WRH</sub>   | vrh —                |     | _   | ns   |

| RD "L" level width          | t <sub>WRL</sub>   |                      | 200 | _   | ns   |

| WR "H" level width          | t <sub>WWH</sub>   | _                    | 200 | _   | ns   |

| WR "L" level width          | t <sub>WWL</sub>   | _                    | 200 | _   | ns   |

| WR-RD "H" level width       | t <sub>wwr</sub> H |                      | 200 | _   | ns   |

| CS, RS setup time           | t <sub>AS</sub>    |                      | 50  | _   | ns   |

| CS, RS hold time            | t <sub>AH</sub>    | _                    | 10  | _   | ns   |

| Write data setup time       | t <sub>DSW</sub>   | _                    | 50  | _   | ns   |

| Write data hold time        | t <sub>DHW</sub>   |                      | 20  | _   | ns   |

| Read data output delay time | t <sub>DDR</sub>   | C <sub>L</sub> =50pF | _   | 170 | ns   |

| Read data hold time         | t <sub>DHR</sub>   | _                    | 20  | _   | ns   |

| RESET pulse width           | twre               | _                    | 2.0 | _   | μs   |

# Parallel interface (2)

$(V_{DD}=4.5 \text{ to } 5.5V, V_{BI}=5 \text{ to } 12V, Ta=-25 \text{ to } +85^{\circ}C)$

| Parameter                   | Symbol             | Condition            | Min | Max | Unit |

|-----------------------------|--------------------|----------------------|-----|-----|------|

| RD "H" level width          | t <sub>WRH</sub> — |                      | 150 | _   | ns   |

| RD "L" level width          | t <sub>WRL</sub>   |                      | 150 | _   | ns   |

| WR "H" level width          | t <sub>ww</sub>    |                      | 150 | _   | ns   |

| WR "L" level width          | t <sub>WWL</sub>   |                      | 150 | _   | ns   |

| WR-RD "H" level width       | t <sub>wwr</sub> — |                      | 150 | _   | ns   |

| CS, RS setup time           | t <sub>AS</sub>    | t <sub>AS</sub> —    |     | _   | ns   |

| CS, RS hold time            | t <sub>AH</sub>    |                      | 10  | _   | ns   |

| Write data setup time       | t <sub>DSW</sub>   |                      | 50  | _   | ns   |

| Write data hold time        | t <sub>DHW</sub>   |                      | 20  | _   | ns   |

| Read data output delay time | t <sub>DDR</sub>   | C <sub>L</sub> =50pF | _   | 130 | ns   |

| Read data hold time         | t <sub>DHR</sub>   |                      | 20  | _   | ns   |

| RESET pulse width           | t <sub>WRE</sub>   | _                    | 2.0 | _   | μs   |

# **Parallel Interface Timing Diagram**

$V_{IH}=0.8V_{DD}, \hspace{0.5cm} V_{IL}=0.2V_{DD} \\$

$V_{OH} = 0.9 V_{DD}, \quad V_{OL} = 0.1 V_{DD}$

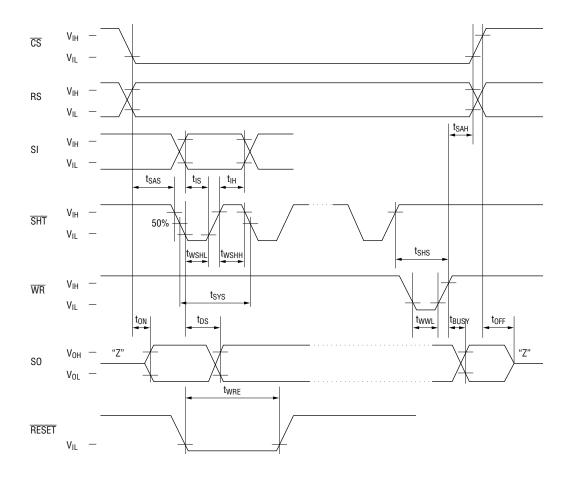

#### Serial interface (1)

$(V_{DD}=2.7 \text{ to } 4.5V, V_{BI}=5 \text{ to } 12V, Ta=-25 \text{ to } +85^{\circ}C)$

| Parameter            | Symbol            | Condition            | Min | Max | Unit |

|----------------------|-------------------|----------------------|-----|-----|------|

| CS, RS setup time    | t <sub>SAS</sub>  | _                    | 60  | _   | ns   |

| CS, RS hold time     | t <sub>SAH</sub>  | _                    | 15  | _   | ns   |

| SI setup time        | t <sub>IS</sub>   | _                    | 100 | _   | ns   |

| SI hold time         | t <sub>IH</sub>   | _                    | 15  | _   | ns   |

| SHT "H" pulse width  | t <sub>WSHH</sub> | _                    | 100 | _   | ns   |

| SHT "L" pulse width  | t <sub>WSHL</sub> | _                    | 100 | _   | ns   |

| SHT clock cycle time | t <sub>SYS</sub>  | _                    | 400 |     | ns   |

| SO ON delay time     | t <sub>ON</sub>   | C <sub>L</sub> =50pF | _   | 200 | ns   |

| SO output delay time | t <sub>DS</sub>   | C <sub>L</sub> =50pF | 0   | 200 | ns   |

| SO OFF delay time    | t <sub>OFF</sub>  | _                    | _   | 50  | ns   |

| BUSY delay time      | t <sub>BUSY</sub> | C <sub>L</sub> =50pF | _   | 200 | ns   |

| WR setup time        | t <sub>SHS</sub>  | _                    | 100 | _   | ns   |

| WR "L" pulse width   | t <sub>WWL</sub>  | _                    | 120 | _   | ns   |

| RESET pulse width    | t <sub>WRE</sub>  | _                    | 2.0 | _   | μs   |

## Serial interface (2)

$(V_{DD}=4.5 \text{ to } 5.5V, V_{BI}=5 \text{ to } 12V, Ta=-25 \text{ to } +85^{\circ}C)$

| Parameter            | Symbol            | Condition            | Min | Max | Unit |

|----------------------|-------------------|----------------------|-----|-----|------|

| CS, RS setup time    | t <sub>SAS</sub>  | _                    | 50  | _   | ns   |

| CS, RS hold time     | t <sub>SAH</sub>  | _                    | 10  | _   | ns   |

| SI setup time        | t <sub>IS</sub>   | _                    | 50  | _   | ns   |

| SI hold time         | t <sub>IH</sub>   | _                    | 10  | _   | ns   |

| SHT "H" pulse width  | t <sub>WSHH</sub> | _                    | 80  | _   | ns   |

| SHT "L" pulse width  | t <sub>WSHL</sub> | _                    | 80  | _   | ns   |

| SHT clock cycle time | t <sub>SYS</sub>  | _                    | 200 | _   | ns   |

| SO ON delay time     | t <sub>ON</sub>   | C <sub>L</sub> =50pF |     | 100 | ns   |

| SO output delay time | t <sub>DS</sub>   | C <sub>L</sub> =50pF | 0   | 100 | ns   |

| SO OFF delay time    | t <sub>OFF</sub>  | _                    | _   | 20  | ns   |

| BUSY delay time      | t <sub>BUSY</sub> | C <sub>L</sub> =50pF | _   | 100 | ns   |

| WR setup time        | t <sub>SHS</sub>  | _                    | 50  | _   | ns   |

| WR "L" pulse width   | t <sub>WWL</sub>  | _                    | 80  | _   | ns   |

| RESET pulse width    | t <sub>WRE</sub>  | _                    | 2.0 | _   | μs   |

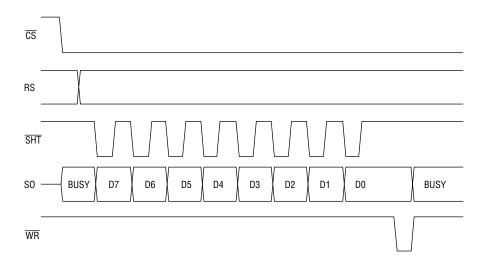

# **Serial Interface Timing Diagram**

$$V_{IH}=0.8V_{DD}, \hspace{0.5cm} V_{IL}=0.2V_{DD} \\$$

$$V_{OH} = 0.9 V_{DD}, \quad V_{OL} = 0.1 V_{DD}$$

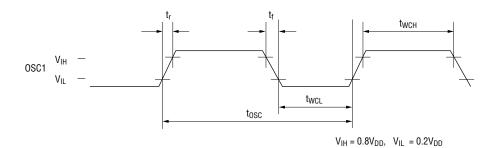

# External clock (1)

$(V_{DD}=2.7 \text{ to } 4.5V, V_{BI}=5 \text{ to } 12V, Ta=-25 \text{ to } +85^{\circ}C)$

| Parameter                           | Symbol                          | Condition | Min | Max | Unit |

|-------------------------------------|---------------------------------|-----------|-----|-----|------|

| OSC clock cycle time                | tosc                            | _         | 600 | _   | ns   |

| External clock "H" level width      | twch                            |           | 200 | _   | ns   |

| External clock "L" level width      | t <sub>WCL</sub>                | _         | 200 | _   | ns   |

| External clock rise time, fall time | t <sub>r</sub> , t <sub>f</sub> | _         | _   | 100 | ns   |

# External clock (2)

(V<sub>DD</sub>=4.5 to 5.5V, V<sub>BI</sub>=5 to 12V, Ta=–25 to +85 $^{\circ}$ C)

| Parameter                           | Symbol                          | Condition | Min | Max | Unit |

|-------------------------------------|---------------------------------|-----------|-----|-----|------|

| OSC clock cycle time                | tosc                            | _         | 340 | _   | ns   |

| External clock "H" level width      | t <sub>WCH</sub>                | _         | 150 | _   | ns   |

| External clock "L" level width      | twcL                            | _         | 150 | _   | ns   |

| External clock rise time, fall time | t <sub>r</sub> , t <sub>f</sub> | _         | _   | 20  | ns   |

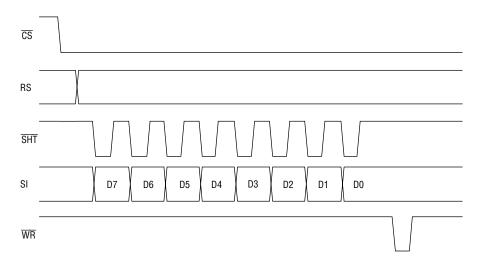

# **Serial Interface Input/Output Timing**

# Input timing

# **Output timing**

For SO output, 8 bits after input of the  $\overline{\text{WR}}$  pulse are valid.

#### **FUNCTIONAL DESCRIPTION**

#### **Pin Functional Description**

#### • <del>CS</del> (Chip Select)

Chip select input pin. "L" is for Select, "H" is for Unselect. Internal registers can be accessed only when this pin is at "L".

When this pin is "H", the SO pin becomes high impedance.

#### $\bullet \overline{WR}$ (Write Enable)

This is a write signal input pin when a parallel interface is used. Data is written to a register at the rising edge of a signal pulse.

This becomes a latch signal input pin when a serial interface is used.

This pin is normally "H".

#### • RD (Read Enable)

This is a read signal input pin when a parallel interface is used. Data can be read while the pulse is "L". This pin is normally "H".

Set this pin to "H" or "L" when a serial interface is used.

#### •RS (Register Select)

Input pin to select register. Setting this pin to "L" selects the address register. Setting to "H" selects a register set by the address register.

If this pin is changed from "H" to "L" while a serial interface is used, the SERW bit (D4 bit) of the address register is automatically reset to "0".

#### • DB0 to DB7 (Data Buses 0 to 7)

Data input/output pins for parallel interface. These pins are normally in high impedance status. When  $\overline{RD} = "L"$ , each register data is output.

Leave this pin open when a serial interface is used.

#### •SI (Serial Data Input)

Data input pin for serial interface. Each register data and display data are read at the rising edge of  $\overline{SHT}$ , and written to the register at the falling edge of  $\overline{WR}$ . 8-bit data just before the rise of  $\overline{WR}$  is valid data.

Set this pin to "H" or "L" when a parallel interface is used.

#### •SO (Serial Data Output)

Data output pin for serial interface. Each register data is output synchronizing with the rise of  $\overline{SHT}$ . For busy/non-busy data, busy ("H") is output after the rise of  $\overline{WR}$ , and automatically becomes non-busy ("L") after a specified time.

This pin is always in high impedance status when a parallel interface is used.

#### •SHT (Shift Clock)

Clock input pin for serial interface data input/output. Data is input synchronizing with the rise of the clock, and data is output synchronizing with the fall of the clock.

This pin is normally in "H".

Set this pin to "H" or "L" when a parallel interface is used.

#### • P/S (Parallel/Serial Select)

Input pin for selecting parallel interface or serial interface. Setting this pin to "L" selects parallel interface. Setting to "H" selects serial interface. Do not change the setting value after power is turned on.

#### •LCDCK (LCD Clock)

Input/output pin for display data latch clock. This pin is an output pin if master is specified and is an input pin if slave is specified. To use two or more MSM6794 devices, connect LCDCK of the master with LCDCK of the slave.

#### •FLM (First Line Marker)

Input/output pin for the first line marker. This pin is an output pin if master is specified, and is an input pin if slave is specified. To use two or more MSM6794 devices, connect FLM of the master with FLM of the slave.

#### •DF (Display Frequency)

Input/output pin for LCD alternating frame signals. This pin is an output pin if master is specified, and an input pin if slave is specified. To use two or more MSM6794 devices, connect DF of the master with DF of the slave.

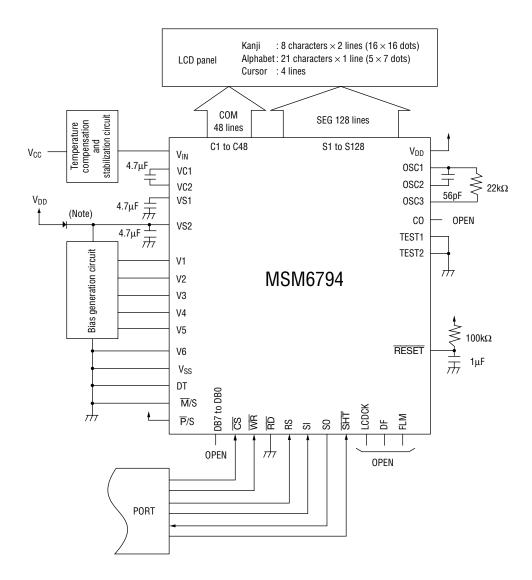

#### •OSC1 (Oscillation 1)

Input pin for RC oscillation. Connecting the specified capacitor and resistor to this pin and the OSC2 and OSC3 pins creates an RC oscillation circuit. The wiring distance between the external parts and these pins should be as short as possible. To generate an original oscillation clock externally, input the original oscillation clock to this pin.

#### •OSC2, OSC3 (Oscillation 2, Oscillation 3)

Output pins for RC oscillation. Connecting the specified capacitor and resistor to these pins and the OSC1 pin creates an RC oscillation circuit. The wiring distance between the external parts and these pins should be as short as possible. To generate an original oscillation clock externally, leave these pins open.

For RC oscillation circuit

For external clock input

Oscillation circuit diagram

#### $\overline{M}/S$ (Master/Slave)

Input pin for switching between master and slave. Setting this pin to "L" sets this IC to the IC at the master side. Setting this pin to "H" sets this IC to the IC at the slave side. Do not change the setting value after power is turned on.

#### CO (Clock Output)

Output pin for original oscillation clock. The clock in the same phase as OSC1 is output. To use two or more MSM6794 devices, connect CO of the master with OSC1 of the slave.

#### RESET (Reset)

Pin for reset signal input. Setting this pin to "L" sets initial status. For the status of each register and display after reset input, see "Status of Pins and Registers after Reset Input".

#### TEST1, TEST2 (Test Signal 1, Test Signal 2)

Test signal input pins. These pins are used by Oki to test. Set these pins to "L" permanently.

#### SEG1 to SEG128 (Segment 1 to Segment 128)

Segment signal output pins for driving LCD. Leave unused segment pins open.

#### COM1 to COM48 (Common 1 to Common 48)

Common signal output pins for driving LCD. Use COM1 to COM33 and leave COM34 to COM48 open for 1/33 duty. Use COM1 to COM41 and leave COM42 to COM48 open for 1/41 duty. Use COM1 to COM44 and leave COM45 to COM48 open for 1/44 duty.

#### V<sub>DD1</sub> to V<sub>DD4</sub>

Pins to connect the logic power supply. Connect these pins to positive pins of the power supply.

#### $V_{SS1}$ to $V_{SS3}$

Pins to connect GND power supply.

#### V1, V3, V4, V6

LCD power supply pins for the segment driver. Connect V6 to GND.

#### V1, V2, V5, V6

LCD power supply pins for the common driver. Connect V6 to GND.

#### DT (Doubler/Tripler Select)

Input pin to select voltage multiplier circuit. Setting this pin to "L" selects tripler, and setting this pin to "H" selects doubler. Do not change the selection after power is turned on.

#### VS1

Doubler voltage output pin. Voltage twice as high as voltage that is input from  $V_{IN}$  is output from this pin. Connect a  $4.7\mu F$  capacitor between this pin and the  $V_{SS1}$  to  $V_{SS3}$  pins to stabilize power supply. When doubler is used, connect this pin with VS2. The wiring distance between the external parts and these pins should be as short as possible.

Set this pin to GND level if the voltage multiplier circuit is not used.

#### VS2

Multiplied voltage output pin. Multiplied voltage set by the DT pin is output from this pin. If tripler is used, connect a  $4.7\mu F$  capacitor between this pin and the  $V_{SS1}$  to  $V_{SS3}$  pins to stabilize power supply. If doubler is used, connect this pin with VS1. The wiring distance between the external parts and these pins should be as short as possible.

Set this pin to GND level if the voltage multiplier circuit is not used.

#### VC1, VC2

Capacitor connection pins for voltage multiplication. Connect a  $4.7\mu F$  capacitor between the VC1 and VC2 pins. When an electrolytic capacitor is used, connect the VC2 pin to the positive side. The wiring distance between the external parts and these pins should be as short as possible. Set these pins to GND level if the voltage multiplier circuit is not used.

MSM6794

#### $V_{IN}$

Voltage multiplication reference voltage input pin. Voltage two or three times higher than voltage that is input to this pin is output from the VS2 pin.

Set this pin to GND level if the voltage multiplier circuit is not used.

#### (Note)

Input the  $V_{IN}$  level after rise of the  $V_{DD}$  level.

$5\,\text{ms/V}$  or more is required for rise of the  $V_{IN}$  level because abnormal voltage multiplication will possibly occurs if the  $V_{IN}$  level rises too quickly.

Even if it is impossible to have 5 ms/V or more, the voltage potential relationship VS2> $V_{DD}$ > $V_{IN}$  can prevent abnormal voltage multiplication by inserting a diode with a reversal withstand voltage of 14 V or more between  $V_{DD}$  and VS2. (See APPLICATION CIRCUIT EXAMPLE)

#### Registers

| cs | RS | Register number |   | Register | Register              |      |      |      | Data | a bit |     |          |        |

|----|----|-----------------|---|----------|-----------------------|------|------|------|------|-------|-----|----------|--------|

| CS | пэ | 1               | 0 | symbol   | name                  | 7    | 6    | 5    | 4    | 3     | 2   | 1        | 0      |

| 1  | _  | _               | _ | _        | Invalid               | _    | _    | _    | _    | _     |     | _        | _      |

| 0  | 0  | _               | _ | AR       | Address register      | BUSY | STBY | DISP | SERW | HZ    |     | Register | number |

| 0  | 1  | 0               | 0 | DRAM     | Display data register | D7   | D6   | D5   | D4   | D3    | D2  | D1       | D0     |

| 0  | 1  | 0               | 1 | YAD      | X address register    | _    | _    | _    |      |       | XAD |          |        |

| 0  | 1  | 1               | 0 | XAD      | Y address register    | _    | _    |      |      | YAD   |     |          |        |

| 0  | 1  | 1               | 1 | FCR      | Control register      | INC  | WLS  | _    |      | FFS   |     | DU       | ITY    |

#### **Register Description**

#### Address register (AR)

| D7   | D6   | D5   | D4   | D3 | D2 | D1              | D0 |

|------|------|------|------|----|----|-----------------|----|

| BUSY | STBY | DISP | SERW | HZ | _  | Register number |    |

#### (1) D7 BUSY (Busy flag)

1: busy

0: ready

This bit indicates that this IC is in internal processing. Reading/Writing display memory sets this bit to "1". This bit becomes busy for a period of a maximum of 8 clocks by reading/writing display memory. Registers other than this register cannot be read or written while this bit is "1".

Setting the  $\overline{RESET}$  pin to "L" also sets this bit to "1". This bit becomes "1" while the  $\overline{RESET}$  pin is "L", and becomes "0" when the  $\overline{RESET}$  pin becomes "H". In the case of a serial interface, the SO pin becomes high impedance if the  $\overline{RESET}$  pin becomes "L". Therefore this bit cannot be read during a reset period.

This bit is read only. Writing to this bit is invalid.

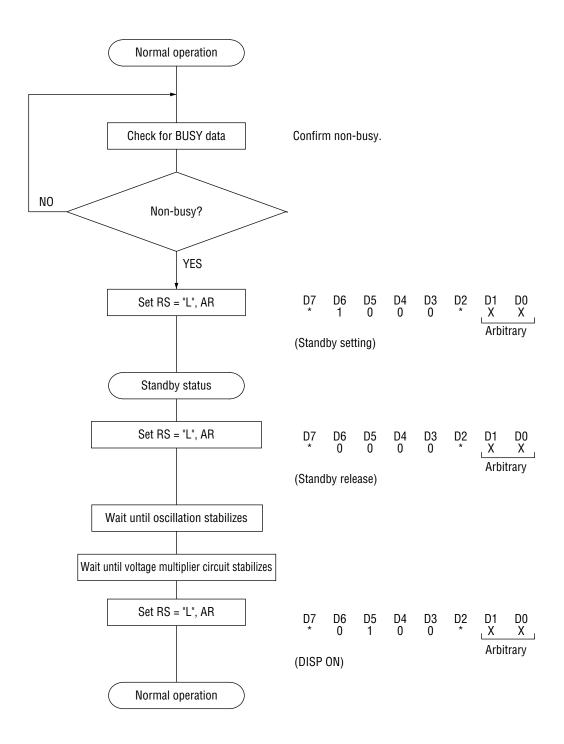

#### (2) D6 STBY (Standby)

1: standby

0: normal

This bit sets this IC to standby mode. This IC enters standby mode by writing "1" to this bit, and returns from standby mode to normal mode by writing "0" to this bit.

This bit is set to normal status by setting the RESET pin to "L".

Setting this bit to standby mode in a busy state may cause a malfunction.

For details of standby mode, see "Pin status during Standby Operation and Register Status after Cancellation".

#### (3) D5 DISP (Display on/off)

1: display on

0: display off

This bit sets ON/OFF of the liquid crystal display connected to this IC. Writing "1" to this bit turns the liquid crystal display ON, and writing "0" turns it OFF. This bit is used to prevent a random display until the initialization of the display memory after power-on.

This bit is set to display off status by setting the  $\overline{RESET}$  pin to "L".

#### (4) D4 SERW (Serial Data Read/Write)

1: writing registers other than address register is invalid

0: writing all registers is valid

This bit limits writing to registers when a serial interface is used. Writing "1" to this bit disables writing to registers other than the address register, and writing "0" enables writing to all registers.

This bit is a command to make registers read-only when a serial interface is used. When serial data is read from the SO pin, this pin disables writing to registers other than the address register, even if data is input to the SI pin.

This bit is valid only when a serial interface is used. When a parallel interface is used, writing to this bit is invalid, and "0" is always read from this bit.

This bit is set to write enable of all registers by setting the  $\overline{RESET}$  pin to "L". This bit is automatically reset to "0" each time the RS pin is set from "H" to "L".

MSM6794

#### (5) D3 HZ (high impedance) (SO pin output control)

1: high impedance

0: output enable

This bit sets the status of the SO pin when a serial interface is used. Writing "1" to this bit sets the SO pin to a high impedance state, and writing "0" to this bit sets the SO pin to an output enable state.

This bit is valid only when a serial interface is used. When a parallel interface is used, writing to this bit is invalid, and "0" is always read from this bit.

This bit is set to a high impedance state by setting the  $\overline{RESET}$  pin to "L".

#### (6) D2 (Invalid Bit)

Writing to this bit is invalid, and "0" is always read from this bit.

#### (7) D1, D0 (Register Number)

These bits select a register other than the address register. The relationship between each bit and each register is shown in the table below.

| Code | D1 | D0 | Register Name         |

|------|----|----|-----------------------|

| 0    | 0  | 0  | Display data register |

| 1    | 0  | 1  | X address register    |

| 2    | 1  | 0  | Y address register    |

| 3    | 1  | 1  | Control register      |

These bits are reset to (D1, D0) = (0, 0) (display data register select status) by setting the  $\overline{RESET}$  pin to "L".

MSM6794

#### Display data register (DRAM)

| D7           |  |  | D5 D4 D3 D2 |  |  |  | D0 |  |  |

|--------------|--|--|-------------|--|--|--|----|--|--|

| 8-bit DATA   |  |  |             |  |  |  |    |  |  |

| — 6-bit DATA |  |  |             |  |  |  |    |  |  |

This register is used to write or read display data to and from the liquid crystal display RAM. The contents of this register are written or read to and from the address set by the X address register and Y address register.

The bit length of display data is selected by the WLS bit (D6 bit) of the control register. If 6-bit data is selected, writing to the D7 and D6 bit is invalid, and "0" is always read from these bits. D7 (D5 for 6-bit DATA) is MSB, and D0 is LSB.

The content of this register does not change, even if the RESET pin is set to "L".

#### X address register (XAR)

| D7 | D6 | D5 | D4 | D3 | D2  | D1 | D0 |

|----|----|----|----|----|-----|----|----|

| _  |    |    |    |    | XAD |    |    |

This register is used to set the X address of the liquid crystal display RAM.

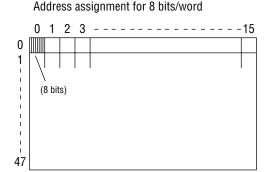

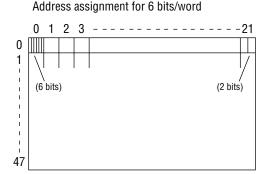

If 8-bit data is selected by the WLS bit (D6 bit) of the control register, the addresses are 0 to 15 (00H to 0FH). If 6-bit data is selected, the addresses are 0 to 21 (00H to 15H). If other addresses are set, operation is unpredictable.

Writing to the D7 to D5 bits is invalid, and "0" is always read from these bits.

This register is reset to "0" by setting the  $\overline{RESET}$  pin to "L".

#### Y address register (YAR)

| D7    | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-------|----|----|----|----|----|----|----|

| — YAD |    |    |    |    |    |    |    |

This register is used to set the Y address of the liquid crystal display RAM.

If 1/48 duty is selected by DUTY bits (D1, D0 bits) of the control register, the address set value is 0 to 47 (00H to 2FH). If 1/44 duty is selected, the address set value is 0 to 43 (00H to 2BH). If 1/41 duty is selected, the address set value is 0 to 40 (00H to 28H), and if 1/33 duty is selected, the address set value is 0 to 32 (00H to 20H). If other values are set, operation is unpredictable. Writing to D7 and D6 bits is invalid, and "0" is always read from these bits.

This register is reset to "0" by setting the  $\overline{RESET}$  pin to "L".

#### **Control register (FCR)**

| D7  | D6  | D5 | D4 | D3  | D2 | D1  | D0 |

|-----|-----|----|----|-----|----|-----|----|

| INC | WLS | -  |    | FFS | DU | ITY |    |

#### (1) D7 INC (Address Increment Direction)

- 1: X direction

- 0: Y direction

This bit sets the address increment direction of the display RAM. The address of the display RAM is automatically incremented by 1 by writing data to the display data register. Writing "1" to this bit sets the X address increment, and writing "0" to this bit sets the Y address increment.

For details of address increment, see "X, Y Address Counter Auto Increment".

The value of this register does not change, even if the  $\overline{RESET}$  pin is set to "L".

#### (2) D6 WLS (Word Length Select)

- 1: 6 bits

- 0: 8 bits

This bit selects the read/write word length to the display RAM. Writing "1" to this bit sets read/write data to the display RAM in 6 bit units, and writing "0" to this bit sets read/write data to the display RAM in 8 bit units. Select the word length according to the character font to be used.

The value of this register does not change, even if the  $\overline{RESET}$  pin is set to "L".

#### (3) D5 (Invalid Bit)

Writing to this bit is invalid. "0" is always read from this bit.

#### (4) D4 to D2 FFS (Frame Frequency Select)

This bit selects the internal clock frequency dividing ratio to the original oscillation frequency. Correspondence between each bit and each frequency dividing ratio is shown in the table below.

| Code | D4 | D3 | D2 | Frequency Dividing Ratio |

|------|----|----|----|--------------------------|

| 0    | 0  | 0  | 0  | 1                        |

| 1    | 0  | 0  | 1  | 1/2                      |

| 2    | 0  | 1  | 0  | 1/3                      |

| 3    | 0  | 1  | 1  | 1/4                      |

| 4    | 1  | 0  | 0  | 1/6                      |

| 5    | 1  | 0  | 1  | 1/8                      |

| 6    | 1  | 1  | 0  | TEST                     |

| 7    | 1  | 1  | 1  | TEST                     |

When the original oscillation frequency is 350kHz and the frequency dividing ratio is 1, the frame frequency is about 80Hz. When the display data register is written/read, the maximum busy time is 8 oscillation clocks for RC oscillation (typ. 350 kHz), and 8 supplied clocks for external clock input. It is possible to increase the original oscillation frequency in order to shorten the busy time when an external clock is input; however, the frame frequency increases in proportion to the original oscillation frequency. In this case the frequency dividing ratio must be changed so that the frame frequency falls in the range of 60 to 100Hz. For details on the relation between original oscillation frequency and frame frequency, see "Original Oscillation Frequency and Frame Frequency".

When an RC oscillation circuit is configured, 1 is the only available frequency dividing ratio. (D4, D3, D2) = (1, 1, 0) and (1, 1, 1) are combinations which Oki uses for testing.

If these combinations are used by the user, the operation of this IC is unpredictable.

The value of this register does not change even if the RESET pin is set to "L".

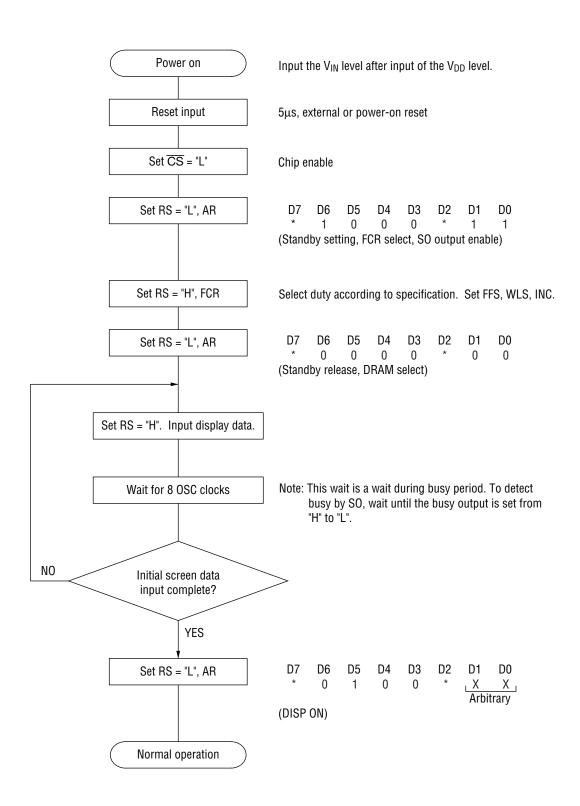

Once frame frequency is set after power is turned on, the value cannot be changed. To change the frame frequency, set it again according to the power-on flowchart. See "Power-on Flowchart".

#### (5) D1, D0 DUTY (Display Duty Select)

These bits select the display duty. Correspondence between each bit and display duty is shown in the table below.

| Code | D1 | D0 | DUTY |

|------|----|----|------|

| 0    | 0  | 0  | 1/48 |

| 1    | 0  | 1  | 1/44 |

| 2    | 1  | 0  | 1/41 |

| 3    | 1  | 1  | 1/33 |

The value of this register does not change, even if the  $\overline{\text{RESET}}$  pin is set to "L". Once display duty is set after power is turned on, the value cannot be changed. To change display duty, set it again according to the power-on flowchart. See "Power-on Flowchart".

# **Status of Pins and Registers After Reset Input**

The following tables show pin and register status after reset input.

| Pin     | Status                               |

|---------|--------------------------------------|

| OSC2, 3 | Clock output or oscillation status   |

| CO      | Clock output                         |

| S0      | High impedance                       |

| DF      | "H" (master), high impedance (slave) |

| FLM     | "L" (master), high impedance (slave) |

| LCDCK   | "L" (master), high impedance (slave) |

| Register              | Status                                       |

|-----------------------|----------------------------------------------|

| Address register      | HZ = "1", other bits are reset to "0".       |

| Display data register | Display data is held                         |

| X address register    | Reset to "0"                                 |

| Y address register    | Reset to "0".                                |

| Control register      | No change from status before inputting reset |

# Pin Status during Standby Operation and Register Status after Cancellation

The following tables show pin status during standby operation and register status after cancellation.

| Pin   | Status                               |  |  |  |

|-------|--------------------------------------|--|--|--|

| OSC2  | "L"                                  |  |  |  |

| OSC3  | "H"                                  |  |  |  |

| CO    | "L"                                  |  |  |  |

| S0    | High impedance                       |  |  |  |

| DF    | "H" (master), high impedance (slave) |  |  |  |

| FLM   | "L" (master), high impedance (slave) |  |  |  |

| LCDCK | "L" (master), high impedance (slave) |  |  |  |

| Register              | Status                                              |

|-----------------------|-----------------------------------------------------|

| Address register      | STBY = "0", other bits maintain data before standby |

| Display data register | Maintains data before standby                       |

| X address register    | Reset to "0"                                        |

| Y address register    | Reset to "0"                                        |

| Control register      | Maintains data before standby                       |

#### X, Y Address Counter Auto Increment

RAM for the liquid crystal display of the MSM6794 has an X address counter and Y address counter, and both have an auto increment function.

Writing/reading display data increments either X or Y address counter. The INC bit (D7 bit) of the control register selects X or Y address to be incremented.

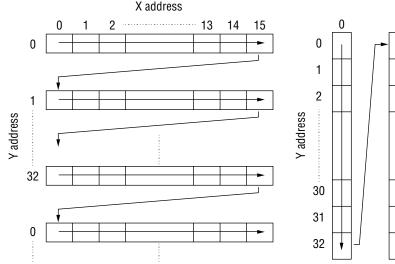

(When X address is selected:)

Address count cycle of X address counter changes depending on word length: 8- or 6-bit.

If the word length is 8-bit, X address is counted in a 0 to 15 range.

If the word length is 6-bit, X address is counted in a 0 to 21 range.

When the maximum value of an X address count value (15 for an 8-bit word length, and 21 for a 6-bit word length) returns to "0", the Y address count value is also automatically incremented.

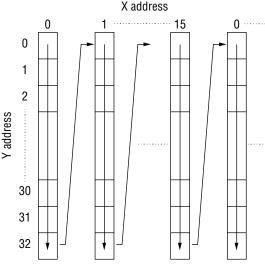

(When Y address is selected:)

The address count of Y address counter changes depending on the display duty: 1/33, 1/41, 1/44 or 1/48.

If the display duty is 1/33, Y address is counted in a 0 to 32 range.

If the display duty is 1/41, Y address is counted in a 0 to 40 range.

If the display duty is 1/44, Y address is counted in a 0 to 43 range.

If the display duty is 1/48, Y address is counted in a 0 to 47 range.

When the maximum value of a Y address count value (32 for display duty 1/33, 40 for display duty 1/41, 43 for display duty 1/44, and 47 for display duty 1/48) returns to "0", the X address count value is also automatically incremented.

(Note) If an address other than the count cycle is set at X or Y address counter, count operation becomes abnormal.

- 1. Example of X address increment (8-bit word length, 1/33 duty)

- 2. Example of Y address increment (8-bit word length, 1/33 duty)

#### **Display Screen and Memory Address**

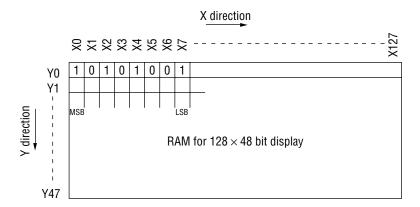

The MSM6794 includes a bit map type display RAM ( $48 \times 128$  bit). Display data is written to display memory with MSB as (Xn, Yn) address, and LSB as (Xn+7, Yn) address, as shown in Figure 1.

Writing "1" to display memory turns the light on, and writing "0" turns the light off.

The address assignment of memory address changes depending on the selection of word length: 8 bits or 6 bits. The memory address is 0 to 15 for 8 bits per word, and 0 to 21 for 6 bits per word. When X address is 21 with 6 bits per word, the display memory is 2 bits. 2 bits (D5, D4) from MSB of data display are written to memory, with the remaining 4 bits (D3 to D0) becoming invalid.

Figure 1. Correspondence between display screen and memory

Figure 2. Display memory address

# **Power-on Flowchart (Serial Interface)**

# **STBY Setting and Cancellation Flowchart**

MSM6794

#### Original Oscillation Frequency and Frame Frequency

#### Frame frequency calculation

For 1/33, 1/44, 1/48 DUTY:

(Original oscillation clock cycle) × (1/frequency dividing ratio) × 4224 = frame cycle .......Formula 1

For 1/41 DUTY:

(Original oscillation clock cycle) × (1/frequency dividing ratio) × 4264 = frame cycle ......Formula 2

Frame frequency can be calculated by the above formulas.

Example 1) For original oscillation 350 [kHz], frequency dividing ratio 1/1, and 1/33 duty specification: By formula 1, frame cycle Tf =  $1/(350\times10^3)\times1\times4224=12.1$  [ms] Therefore, frame frequency = 82.9 [Hz]

Example 2) For original oscillation 1 [MHz], frequency dividing ratio 1/3, 1/41 duty specification: By formula 2, frame cycle Tf =  $1/(1\times10^6)\times3\times4264=12.8$  [ms] Therefore, frame frequency = 78.2 [Hz]

#### Original oscillation frequency and BUSY time

When RAM data is written or read, data processing time (BUSY time) occurs. BUSY time is a maximum of [(original oscillation clock cycle)  $\times$  8]. As the original oscillation frequency increases, BUSY time becomes shorter (not influenced by the frequency dividing ratio).

By increasing the original oscillation frequency, BUSY time can be made shorter in proportion. In this case frame frequency also increases. So, set the frequency dividing ratio so that frame frequency reaches a frequency close to the frame frequency to be used.

# **LCD Drive Power Supply**

COM DRV input power supply: V1, V2, V5, V6 SEG DRV input power supply: V1, V3, V4, V6

#### **APPLICATION CIRCUITS**

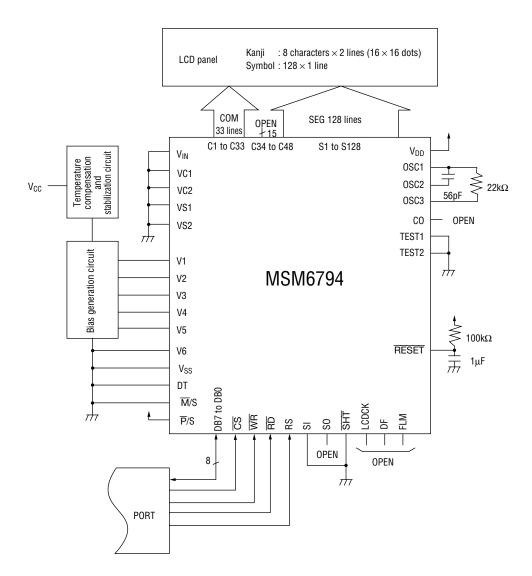

#### Application example (1)

(1/48 duty, serial interface, voltage multiplier circuit (tripler) used, single chip)

(Note) If the potential relationship is  $VS2>V_{DD}>V_{IN}$  insert a diode between  $V_{DD}$  and VS2 for activating the voltage multiplier circuit.

#### Application example (2)

(1/33 duty, parallel interface, voltage multiplier circuit unused, single chip)

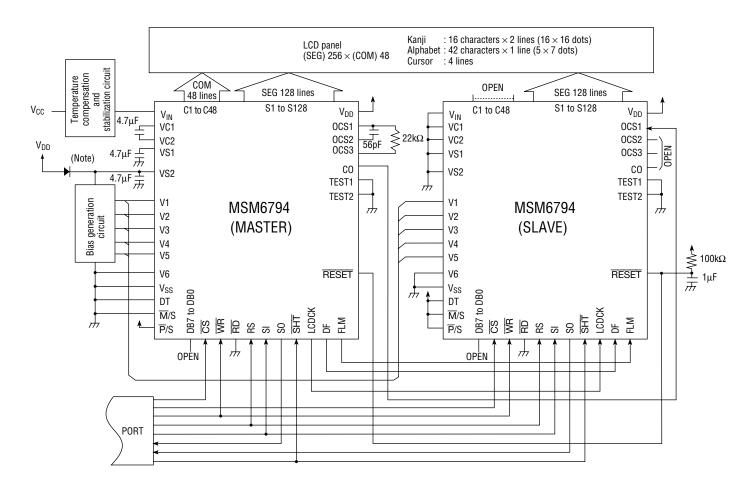

# Application example (3)

(1/48 duty, serial interface, 2 chips used, cascade connection)

(Note) If the potential relationship is  $VS2>V_{DD}>V_{IN}$  insert a diode between  $V_{DD}$  and VS2 for activating the voltage multiplier circuit.

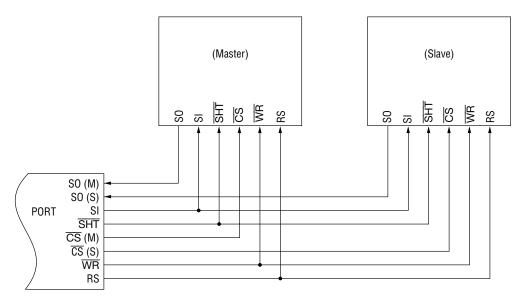

#### **Interface Connection Example**

For serial interface (only control signals are described)

#### Master and slave control operation

Connect as in the above diagram. The master side and slave side can be selected by setting  $\overline{\text{CS}}$  to "L" respectively.

Rise or fall the  $\overline{CS}$  signal level after confirming NON-BUSY.

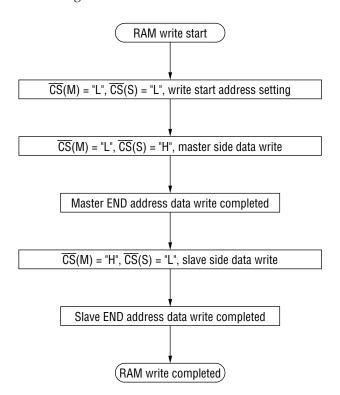

Example of continuous writing of RAM data (all master addresses  $\rightarrow$  all slave addresses):

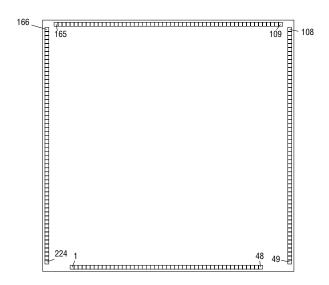

# PAD CONFIGURATION (TOP VIEW)

#### **Pad Layout**

Chip Size:  $8.44 \times 8.02$  mm Chip Thickness:  $350 \mu m$

Passivation Hole:  $100 \times 100 \, \mu m$

Note: The chip substrate should be connected to V<sub>SS</sub> (GND) or left open.

#### **Pad Coordinates**

| Pad | Ded News         | V()   | V()           | Pad | Ded Name         | V()          | V()           | Pad | Ded Neme | V()          | V/           |

|-----|------------------|-------|---------------|-----|------------------|--------------|---------------|-----|----------|--------------|--------------|

| No. | Pad Name         | X(μm) | <b>Υ (μm)</b> | No. | Pad Name         | <b>Χ(μm)</b> | <b>Υ (μm)</b> | No. | Pad Name | <b>Χ(μm)</b> | <b>Υ(μm)</b> |

| 1   | V6               | -3377 | -3784         | 26  | DB3              | 271          | -3784         | 51  | C46      | 4058         | -3306        |

| 2   | V4               | -3257 | -3784         | 27  | DB2              | 440          | -3784         | 52  | C45      | 4058         | -3186        |

| 3   | V3               | -3137 | -3784         | 28  | DB1              | 609          | -3784         | 53  | C44      | 4058         | -3066        |

| 4   | V1               | -3017 | -3784         | 29  | DB0              | 778          | -3784         | 54  | C43      | 4058         | -2946        |

| 5   | V <sub>DD1</sub> | -2897 | -3784         | 30  | TEST1            | 967          | -3784         | 55  | C42      | 4058         | -2826        |

| 6   | V <sub>DD2</sub> | -2777 | -3784         | 31  | TEST2            | 1098         | -3784         | 56  | C41      | 4058         | -2706        |

| 7   | OSC1             | -2647 | -3784         | 32  | M/S              | 1218         | -3784         | 57  | C40      | 4058         | -2586        |

| 8   | OSC2             | -2453 | -3784         | 33  | FLM              | 1399         | -3784         | 58  | C39      | 4058         | -2466        |

| 9   | OSC3             | -2284 | -3784         | 34  | DF               | 1568         | -3784         | 59  | C38      | 4058         | -2346        |

| 10  | CO               | -2115 | -3784         | 35  | LCDCK            | 1737         | -3784         | 60  | C37      | 4058         | -2226        |

| 11  | V <sub>SS1</sub> | -1962 | -3784         | 36  | DT               | 1937         | -3784         | 61  | C36      | 4058         | -2106        |

| 12  | V <sub>SS2</sub> | -1842 | -3784         | 37  | $V_{DD3}$        | 2057         | -3784         | 62  | C35      | 4058         | -1986        |

| 13  | RESET            | -1712 | -3784         | 38  | V <sub>SS3</sub> | 2177         | -3784         | 63  | C34      | 4058         | -1866        |

| 14  | S0               | -1519 | -3784         | 39  | VS1              | 2297         | -3784         | 64  | C33      | 4058         | -1746        |

| 15  | SI               | -1317 | -3784         | 40  | VS2              | 2417         | -3784         | 65  | C32      | 4058         | -1626        |

| 16  | SHT              | -1186 | -3784         | 41  | VC2              | 2537         | -3784         | 66  | C31      | 4058         | -1506        |

| 17  | P/S              | -1066 | -3784         | 42  | V <sub>IN</sub>  | 2657         | -3784         | 67  | C30      | 4058         | -1386        |

| 18  | <del>CS</del>    | -946  | -3784         | 43  | VC1              | 2777         | -3784         | 68  | C29      | 4058         | -1266        |

| 19  | WR               | -826  | -3784         | 44  | $V_{DD4}$        | 2897         | -3784         | 69  | C28      | 4058         | -1146        |

| 20  | RD               | -706  | -3784         | 45  | V1               | 3017         | -3784         | 70  | C27      | 4058         | -1026        |

| 21  | RS               | -586  | -3784         | 46  | V2               | 3137         | -3784         | 71  | C26      | 4058         | -906         |

| 22  | DB7              | -404  | -3784         | 47  | V5               | 3257         | -3784         | 72  | C25      | 4058         | -786         |

| 23  | DB6              | -235  | -3784         | 48  | V6               | 3377         | -3784         | 73  | C24      | 4058         | -666         |

| 24  | DB5              | -67   | -3784         | 49  | C48              | 4058         | -3546         | 74  | C23      | 4058         | -546         |

| 25  | DB4              | 103   | -3784         | 50  | C47              | 4058         | -3426         | 75  | C22      | 4058         | -426         |

| Pad<br>No. | Pad Name | <b>Χ(μm)</b> | <b>Υ(μm)</b> | Pad<br>No. | Pad Name | <b>Χ(μm)</b> | <b>Υ(μm)</b> | Pad<br>No. | Pad Name | <b>Χ(μm)</b> | <b>Υ(μm)</b> |

|------------|----------|--------------|--------------|------------|----------|--------------|--------------|------------|----------|--------------|--------------|

| 76         | C21      | 4058         | -306         | 101        | S124     | 4058         | 2694         | 126        | S99      | 1292         | 3824         |

| 77         | C20      | 4058         | -186         | 102        | S123     | 4058         | 2814         | 127        | S98      | 1172         | 3824         |

| 78         | C19      | 4058         | -66          | 103        | S122     | 4058         | 2934         | 128        | S97      | 1052         | 3824         |

| 79         | C18      | 4058         | 54           | 104        | S121     | 4058         | 3054         | 129        | S96      | 932          | 3824         |

| 80         | C17      | 4058         | 174          | 105        | S120     | 4058         | 3174         | 130        | S95      | 812          | 3824         |

| 81         | C16      | 4058         | 294          | 106        | S119     | 4058         | 3294         | 131        | S94      | 692          | 3824         |

| 82         | C15      | 4058         | 414          | 107        | S118     | 4058         | 3414         | 132        | S93      | 572          | 3824         |

| 83         | C14      | 4058         | 534          | 108        | S117     | 4058         | 3534         | 133        | S92      | 452          | 3824         |

| 84         | C13      | 4058         | 654          | 109        | S116     | 3332         | 3824         | 134        | S91      | 332          | 3824         |

| 85         | C12      | 4058         | 774          | 110        | S115     | 3212         | 3824         | 135        | S90      | 212          | 3824         |

| 86         | C11      | 4058         | 894          | 111        | S114     | 3092         | 3824         | 136        | S89      | 93           | 3824         |

| 87         | C10      | 4058         | 1014         | 112        | S113     | 2972         | 3824         | 137        | S88      | -28          | 3824         |

| 88         | C9       | 4058         | 1134         | 113        | S112     | 2852         | 3824         | 138        | S87      | -147         | 3824         |

| 89         | C8       | 4058         | 1254         | 114        | S111     | 2732         | 3824         | 139        | S86      | -267         | 3824         |

| 90         | C7       | 4058         | 1374         | 115        | S110     | 2612         | 3824         | 140        | S85      | -387         | 3824         |

| 91         | C6       | 4058         | 1494         | 116        | S109     | 2492         | 3824         | 141        | S84      | -507         | 3824         |

| 92         | C5       | 4058         | 1614         | 117        | S108     | 2372         | 3824         | 142        | S83      | -627         | 3824         |

| 93         | C4       | 4058         | 1734         | 118        | S107     | 2252         | 3824         | 143        | S82      | -747         | 3824         |

| 94         | C3       | 4058         | 1854         | 119        | S106     | 2132         | 3824         | 144        | S81      | -867         | 3824         |

| 95         | C2       | 4058         | 1974         | 120        | S105     | 2012         | 3824         | 145        | S80      | -987         | 3824         |

| 96         | C1       | 4058         | 2094         | 121        | S104     | 1892         | 3824         | 146        | S79      | -1107        | 3824         |

| 97         | S128     | 4058         | 2214         | 122        | S103     | 1772         | 3824         | 147        | S78      | -1227        | 3824         |

| 98         | S127     | 4058         | 2334         | 123        | S102     | 1652         | 3824         | 148        | S77      | -1347        | 3824         |

| 99         | S126     | 4058         | 2454         | 124        | S101     | 1532         | 3824         | 149        | S76      | -1467        | 3824         |

| 100        | S125     | 4058         | 2574         | 125        | S100     | 1412         | 3824         | 150        | S75      | -1587        | 3824         |

| Pad | Pad Name | <b>Χ(μm)</b> | <b>Υ(μm)</b> | Pad | Pad Name | <b>Χ(μm)</b> | <b>Υ(μm)</b> | Pad | Pad Name | <b>Χ(μm)</b> | <b>Υ(μm)</b> |

|-----|----------|--------------|--------------|-----|----------|--------------|--------------|-----|----------|--------------|--------------|

| No. |          | , ,          | , ,          | No. |          |              |              | No. |          | , ,          |              |

| 151 | S74      | -1707        | 3824         | 176 | S49      | -4058        | 2334         | 201 | S24      | -4058        | -666         |

| 152 | S73      | -1827        | 3824         | 177 | S48      | -4058        | 2214         | 202 | S23      | -4058        | -786         |

| 153 | S72      | -1947        | 3824         | 178 | S47      | -4058        | 2094         | 203 | S22      | -4058        | -906         |

| 154 | S71      | -2067        | 3824         | 179 | S46      | -4058        | 1974         | 204 | S21      | -4058        | -1026        |

| 155 | S70      | -2187        | 3824         | 180 | S45      | -4058        | 1854         | 205 | S20      | -4058        | -1146        |

| 156 | S69      | -2307        | 3824         | 181 | S44      | -4058        | 1734         | 206 | S19      | -4058        | -1266        |

| 157 | S68      | -2427        | 3824         | 182 | S43      | -4058        | 1614         | 207 | S18      | -4058        | -1386        |

| 158 | S67      | -2547        | 3824         | 183 | S42      | -4058        | 1494         | 208 | S17      | -4058        | -1506        |

| 159 | S66      | -2667        | 3824         | 184 | S41      | -4058        | 1374         | 209 | S16      | -4058        | -1626        |

| 160 | S65      | -2787        | 3824         | 185 | S40      | -4058        | 1254         | 210 | S15      | -4058        | -1746        |

| 161 | S64      | -2907        | 3824         | 186 | S39      | -4058        | 1134         | 211 | S14      | -4058        | -1866        |

| 162 | S63      | -3027        | 3824         | 187 | S38      | -4058        | 1014         | 212 | S13      | -4058        | -1986        |

| 163 | S62      | -3147        | 3824         | 188 | S37      | -4058        | 894          | 213 | S12      | -4058        | -2106        |

| 164 | S61      | -3267        | 3824         | 189 | S36      | -4058        | 774          | 214 | S11      | -4058        | -2226        |

| 165 | S60      | -3387        | 3824         | 190 | S35      | -4058        | 654          | 215 | S10      | -4058        | -2346        |

| 166 | S59      | -4058        | 3534         | 191 | S34      | -4058        | 534          | 216 | S9       | -4058        | -2466        |

| 167 | S58      | -4058        | 3414         | 192 | S33      | -4058        | 414          | 217 | S8       | -4058        | -2586        |

| 168 | S57      | -4058        | 3294         | 193 | S32      | -4058        | 294          | 218 | S7       | -4058        | -2706        |

| 169 | S56      | -4058        | 3174         | 194 | S31      | -4058        | 174          | 219 | S6       | -4058        | -2826        |

| 170 | S55      | -4058        | 3054         | 195 | S30      | -4058        | 54           | 220 | S5       | -4058        | -2946        |

| 171 | S54      | -4058        | 2934         | 196 | S29      | -4058        | -66          | 221 | S4       | -4058        | -3066        |

| 172 | S53      | -4058        | 2814         | 197 | S28      | -4058        | -186         | 222 | S3       | -4058        | -3186        |

| 173 | S52      | -4058        | 2694         | 198 | S27      | -4058        | -306         | 223 | S2       | -4058        | -3306        |

| 174 | S51      | -4058        | 2574         | 199 | S26      | -4058        | -426         | 224 | S1       | -4058        | -3426        |

| 175 | S50      | -4058        | 2454         | 200 | S25      | -4058        | -546         |     |          |              |              |

#### **NOTICE**

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 2001 Oki Electric Industry Co., Ltd.