# MSM6562B-xx

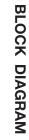

## DOT MATRIX LCD CONTROLLER DRIVER

## **GENERAL DESCRIPTION**

The MSM6562B-xx controls a character type dot matrix LCD in combination with an 8-bit or 4-bit microcontroller.

The MSM6562B-xx can control a display of up to 40 characters. With the display data serial transfer function, the MSM6562B-xx, when used in combination with the character extension IC (MSM5259), can control a maximum of 80 characters.

## FEATURES

- Easy interface with an 8-bit or 4-bit microcontroller.

- Dot matrix LCD controller driver for  $5 \times 7$  dots font or  $5 \times 10$  dots font.

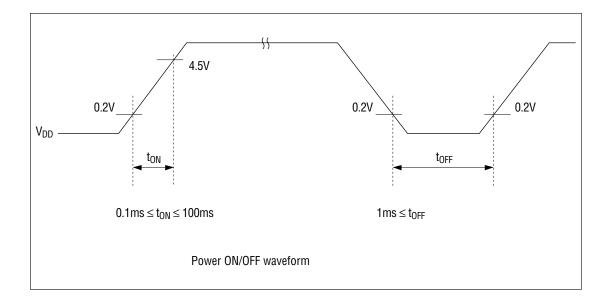

- Automatic power ON reset.

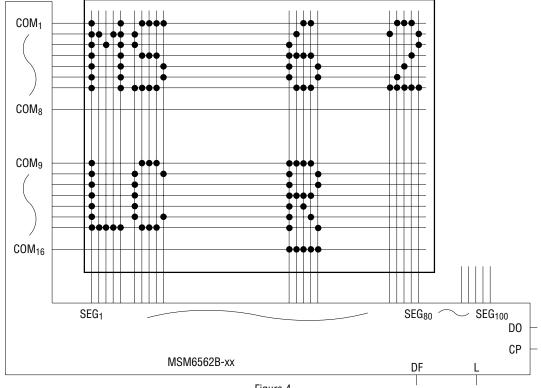

- 16 COMMON signal drivers and 100 SEGMENT signal drivers are built in.

- Can control up to 80 characters when used in combination with MSM5259.

- Built-in character generator ROM for 160 characters with  $5 \times 7$  dots font and 32 characters with  $5 \times 10$  dots font.

- Character patterns can be programmed by CG RAM. (5×8 dots font: 8 kinds, 5×11 dots font: 4 kinds)

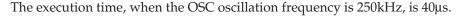

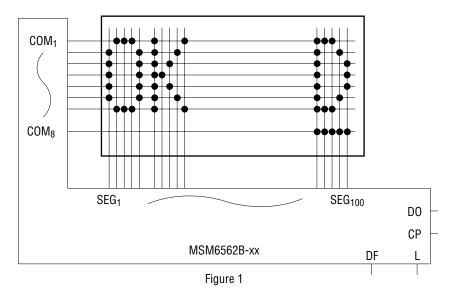

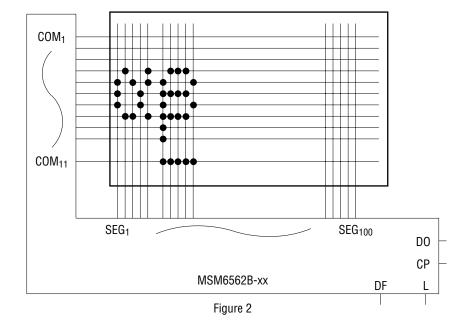

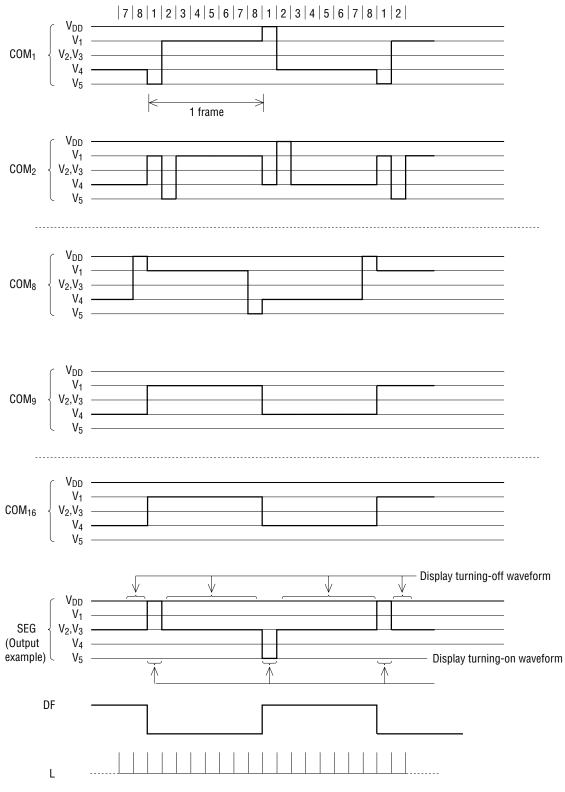

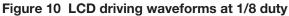

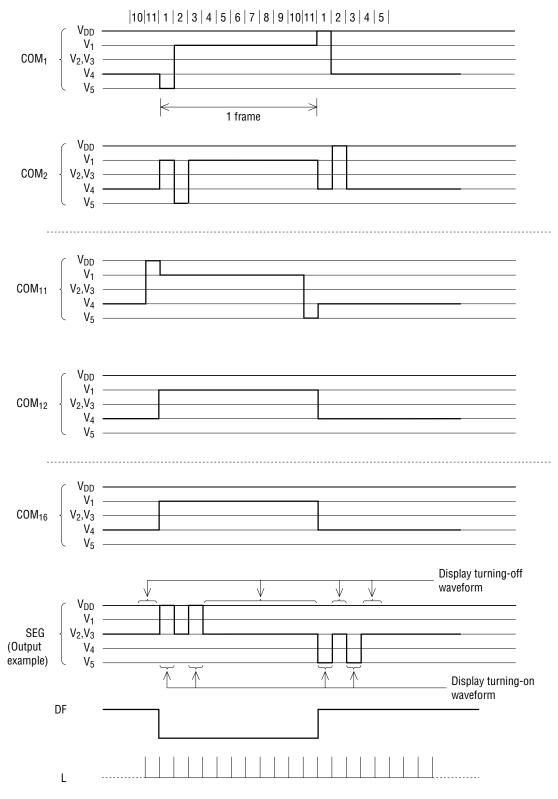

- 1/8 duty (1 line; 5×7 dots + cursor), 1/11 duty (1 line; 5×10 dots + cursor), or 1/16 duty (2 lines; 5×7 dots + cursor) selectable.

- Built-in RC oscillation circuit by an external resistor or an internal resistor.

- Built-in bias dividing resistors for LCD driving.

- Built-in contrast adjusting circuit.

- Bidirectional transfer available on segment output.

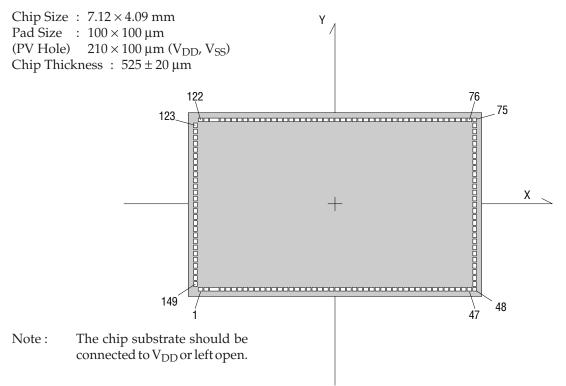

- Aluminum pad chip (Product name: MSM6562B-xx)

xx indicates code number.

# INPUT AND OUTPUT CONFIGURATION

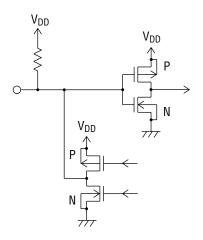

V<sub>DD</sub> V<sub>DD</sub> V<sub>DD</sub> P V<sub>DD</sub> N

Applied to Pin E.

Applied to Pins  $\mathsf{T}_1,\,\mathsf{T}_2$  and  $\mathsf{T}_3.$

Applied to DB<sub>0</sub> - DB<sub>7</sub>.

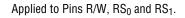

Applied to DO, CP, L and DF.

## **PIN DESCRIPTIONS**

| Symbol                                             | Description                                                                                                                                                  |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DAM                                                | Read/write selection input pin.                                                                                                                              |

| R/W                                                | "H": Read, and "L": Write                                                                                                                                    |

| RS <sub>0</sub> , RS <sub>1</sub>                  | Register selection input pins.       RS0 "H" RS1 "H": Data register         RS0 "L" RS1 "H": Instruction register         RS0 "L" RS1 "L": Contrast register |

| E                                                  | Input pin for data input/output between CPU and MSM6562B-xx and for activating instruction.                                                                  |

| DB <sub>0</sub> - DB <sub>7</sub>                  | Input/output pins for data send/receive between CPU and MSM6562B-xx.                                                                                         |

| OSC <sub>1</sub> , OSC <sub>2</sub> ,              | Clock oscillating pins required for internal operation upon receipt of CPU instruction and                                                                   |

| OSC <sub>R</sub>                                   | the LCD drive signal.                                                                                                                                        |

|                                                    | When oscillated by an external resistor, connect a resistor between $OSC_1$ and $OSC_2$ .                                                                    |

|                                                    | When oscillated by a built-in resistor, connect $OSC_R$ and $OSC_2$ externally.                                                                              |

| COM <sub>1</sub> - COM <sub>16</sub>               | LCD COMMON signal output pins.                                                                                                                               |

| SEG1 - SEG100                                      | LCD SEGMENT signal output pins.                                                                                                                              |

| SHL <sub>0</sub> , SHL <sub>1</sub>                | Input pins to control the transfer direction of the SEGMENT signal output data. See table below.                                                             |

| DO                                                 | Data output pin to send serial data to the character extension IC.                                                                                           |

| CP                                                 | Clock output pin to transfer the serial data to the character extension IC.                                                                                  |

| L                                                  | Latch output pin to latch the transferred data to the character extension IC.                                                                                |

| DF                                                 | Output pin for the alternating signal (DF, display frequency) required for an LCD display.                                                                   |

| V <sub>DD</sub>                                    | Power supply pin.                                                                                                                                            |

| V <sub>SS</sub>                                    | Ground pin.                                                                                                                                                  |

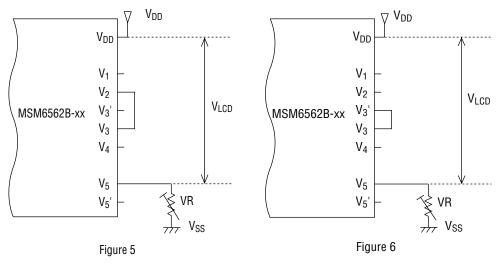

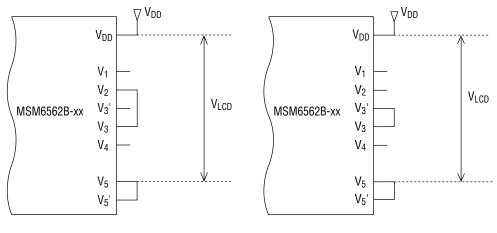

| V <sub>1</sub> - V <sub>5</sub> , V <sub>3</sub> ' | Bias voltage input pins to drive an LCD and bias setting pin. (Built-in bias dividing resistor)                                                              |

|                                                    | 1/4 bias : Connect $V_2$ and $V_3$ . Leave $V_3'$ open.                                                                                                      |

|                                                    | 1/5 bias : Connect V <sub>3</sub> and V <sub>3</sub> '.                                                                                                      |

|                                                    | Since $V_{\text{LCD}}$ value depends on $V_5$ voltage, connect a variable resistor between $V_5$ pin and                                                     |

|                                                    | $V_{SS}$ potential or connect $V_5$ pin and $V_5^\prime$ pin to adjust $V_{LCD}.$                                                                            |

| V <sub>5</sub> '                                   | Contrast adjusting voltage output pin.                                                                                                                       |

| SHL <sub>0</sub> | SHL <sub>1</sub> | Segment data transfer direction                                         |

|------------------|------------------|-------------------------------------------------------------------------|

| L                | L                | $SEG_1 \rightarrow SEG_{100}$                                           |

| L                | Н                | $SEG_{100} \rightarrow SEG_1$                                           |

| Н                | L                | $SEG_1 \rightarrow SEG_{50} \Rightarrow SEG_{100} \rightarrow SEG_{51}$ |

| Н                | Н                | $SEG_{100} \rightarrow SEG_1$                                           |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                      | Symbol                                                                                | Condition | Rating                        | Unit | Applicable Pin                                                                               |

|--------------------------------|---------------------------------------------------------------------------------------|-----------|-------------------------------|------|----------------------------------------------------------------------------------------------|

| Supply voltage                 | V <sub>DD</sub>                                                                       | Ta = 25°C | -0.3 to + 7.0                 | V    | V <sub>DD</sub> , V <sub>SS</sub>                                                            |

| Supply voltage for LCD display | V <sub>1</sub> , V <sub>2</sub> , V <sub>3</sub> ,<br>V <sub>4</sub> , V <sub>5</sub> | Ta = 25°C | -0.3 to V <sub>DD</sub> + 0.3 | V    | V <sub>1</sub> , V <sub>2</sub> , V <sub>3</sub> ,<br>V <sub>4</sub> , V <sub>5</sub>        |

| Input voltage                  | VI                                                                                    | Ta = 25°C | -0.3 to V <sub>DD</sub> + 0.3 | V    | R / W, RS1,<br>RS <sub>0</sub> , E,<br>DB <sub>0</sub> - DB <sub>7</sub><br>OSC <sub>1</sub> |

| Junction temperature           | Tj                                                                                    | _         | 150                           | °C   | _                                                                                            |

| Storage temperature            | T <sub>STG</sub>                                                                      |           | -55 to + 150                  | °C   | _                                                                                            |

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter             | Symbol           | Condition                                | Range                    | Unit | Applicable Pin                    |

|-----------------------|------------------|------------------------------------------|--------------------------|------|-----------------------------------|

| Supply voltage        | V <sub>DD</sub>  | —                                        | 4.5 to 5.5               | V    | V <sub>DD</sub> , V <sub>SS</sub> |

| LCD driving voltage   | N.               | $V_{DD} - V_{SS} 1/4$ bias <sup>*1</sup> | 3.0 to 5.5 <sup>*3</sup> | V    |                                   |

| LCD driving voltage   | V <sub>LCD</sub> | $V_{DD} - V_{SS} 1/5$ bias <sup>*2</sup> | 3.0 to 5.5 <sup>*3</sup> | V    | V <sub>DD</sub> , V <sub>5</sub>  |

| Operating temperature | T <sub>op</sub>  | —                                        | -30 to +85               | °C   |                                   |

- \*1 This voltage should be applied to  $V_{DD} V_5$ . Voltages applicable to  $V_1$ ,  $V_2$ ,  $V_3$  and  $V_4$  are as follows:  $V_1 = V_{DD} - 1/4 (V_{DD} - V_5)$   $V_2 = V_3 = V_{DD} - 1/2 (V_{DD} - V_5)$  $V_4 = V_{DD} - 3/4 (V_{DD} - V_5)$

- \*2 This voltage should be applied to  $V_{DD} V_5$ . Voltages applicable to  $V_1$ ,  $V_2$ ,  $V_3$  and  $V_4$  are as follows:  $V_1 = V_{DD} - 1/5 (V_{DD} - V_5)$   $V_2 = V_{DD} - 2/5 (V_{DD} - V_5)$   $V_3 = V_{DD} - 3/5 (V_{DD} - V_5)$  $V_4 = V_{DD} - 4/5 (V_{DD} - V_5)$

- \*3 The relation of  $V_{DD} > V_1 > V_2 \ge V_3 (=V_3') > V_4 > V_5 \ge V_{SS}$  must be kept. (High  $\leftarrow \rightarrow Low$ )

LCD driving voltage can be adjusted by varying  $V_5$ . However,  $V_5$  cannot be used under  $V_{SS}$  voltage.

## **ELECTRICAL CHARACTERISTICS**

## **DC Characteristics**

|                                                                                                    |                      |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                             |                       | (•0  | 0                  | ,                                                   |                                                                               |

|----------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------|------|--------------------|-----------------------------------------------------|-------------------------------------------------------------------------------|

| Parameter                                                                                          | Symbol               | Condition                                                                                                                                                                                                                                                                                                                                                                                             |                                                                             | Min.                  | Тур. | Max.               | Unit                                                | Applied Pin                                                                   |

| "H" input voltage                                                                                  | VIH1                 |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                             | 2.2                   |      | V <sub>DD</sub>    | V                                                   | R/W, RS <sub>0</sub> , RS <sub>1</sub> , E,                                   |

| "L" input voltage                                                                                  | V <sub>IL1</sub>     |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                             | -0.3                  | _    | 0.6                | V                                                   | DB <sub>0</sub> - DB <sub>7</sub>                                             |

| "H" input voltage                                                                                  | V <sub>IH2</sub>     |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                             | V <sub>DD</sub> – 0.8 |      | V <sub>DD</sub>    | V                                                   | OSC1                                                                          |

| "L" input voltage                                                                                  | V <sub>IL2</sub>     |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                             | -0.3                  |      | 0.8                | V                                                   | SHL <sub>0</sub> , SHL <sub>1</sub>                                           |

| "H" output voltage                                                                                 | V <sub>OH1</sub>     | I <sub>0</sub> = -0.205mA                                                                                                                                                                                                                                                                                                                                                                             |                                                                             | 2.4                   | _    | _                  | V                                                   |                                                                               |

| "L" output voltage                                                                                 | V <sub>0L1</sub>     | l <sub>0</sub> = 1.6mA                                                                                                                                                                                                                                                                                                                                                                                |                                                                             | _                     | _    | 0.4                | V                                                   | DB <sub>0</sub> - DB <sub>7</sub>                                             |

| "H" output voltage                                                                                 | V <sub>0H2</sub>     | I <sub>0</sub> = -40μA                                                                                                                                                                                                                                                                                                                                                                                |                                                                             | 0.9V <sub>DD</sub>    | _    | _                  | V                                                   | D0, CP, L,                                                                    |

| "L" output voltage                                                                                 | V <sub>0L2</sub>     | I <sub>0</sub> = 40μA                                                                                                                                                                                                                                                                                                                                                                                 |                                                                             |                       | _    | 0.1V <sub>DD</sub> | V                                                   | DF, OSC <sub>2</sub>                                                          |

| COM voltage drop                                                                                   | V <sub>C</sub>       | I <sub>0</sub> = ± 40μA<br>(Note 1)                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |                       | _    | 2.3                | V                                                   | COM <sub>1</sub> - COM <sub>16</sub>                                          |

| SEG voltage drop                                                                                   | Vs                   | I <sub>0</sub> = ± 40μA<br>(Note 1)                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |                       |      | 3.0                | V                                                   | SEG <sub>1</sub> - SEG <sub>100</sub>                                         |

|                                                                                                    |                      | $V_I = V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                        |                                                                             | _                     | _    | 1                  | μA                                                  |                                                                               |

| Input leakage current                                                                              | IIL I                | $V_I = V_{SS}$                                                                                                                                                                                                                                                                                                                                                                                        |                                                                             | _                     | _    | -1                 | μA                                                  | E, SHL <sub>0</sub> , SHL <sub>1</sub>                                        |

| "H" input current                                                                                  | I <sub>IH2</sub>     |                                                                                                                                                                                                                                                                                                                                                                                                       | $V_I = V_{DD}$<br>Except the current flowing<br>to the pull-up resistor and |                       | _    | 2                  | μA                                                  | R/W, RS <sub>0</sub> , RS <sub>1</sub> ,<br>DB <sub>0</sub> - DB <sub>7</sub> |

| "L" input current                                                                                  | I <sub>IL2</sub>     | V <sub>DD</sub> = 5.0V<br>V <sub>I</sub> = V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                                            |                                                                             | -34                   | -83  | -204               | μA                                                  | - 000 - 007                                                                   |

| Supply current                                                                                     | I <sub>DD</sub>      | $V_{DD} = 5.0V$ $E = "L" level, SHL_0, SHL_1 = "L" level$ Built-in R <sub>f</sub> oscillation or external<br>clock input to OSC <sub>1</sub> .<br>External clock frequency (f <sub>IN</sub> ) is<br>270kHz.<br>R/W, RS <sub>0</sub> , RS <sub>1</sub> , and DB <sub>0</sub> to DB <sub>7</sub> are<br>open.<br>Output pins are all no load. Except<br>bias current for LCD driving.<br>(Note 2, 3, 4) |                                                                             |                       | _    | 1                  | mA                                                  | V <sub>DD</sub>                                                               |

| LCD driving bias resistance                                                                        | LBR                  | _                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                             | 2                     | 4    | 8                  | kΩ                                                  | $V_{DD} - V_1, V_1 - V_2 V_2 - V_3', V_3 - V_4 V_4 - V_5$                     |

| Variable range by built-in                                                                         | V <sub>LCD MAX</sub> | V <sub>DD</sub> = 5.0V, 1/5 bi                                                                                                                                                                                                                                                                                                                                                                        | as                                                                          | 4.6                   | _    | _                  | N                                                   |                                                                               |

| variable resistor for LCD<br>driving voltage V <sub>LCD MIN</sub> V <sub>DD</sub> = 5.0V, 1/5 bias |                      | as                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                           |                       | 3.7  | V                  | V <sub>DD</sub> – V <sub>5</sub> (V <sub>5</sub> ') |                                                                               |

| LCD driving bias voltage                                                                           | V <sub>LCD1</sub>    | $V_{DD} - V_5$                                                                                                                                                                                                                                                                                                                                                                                        | 1/5 bias                                                                    | 3.0                   | _    | 5.5                | V                                                   | V <sub>DD</sub> , V <sub>1</sub> , V <sub>2</sub> , V <sub>3</sub> ,          |

| (external input)                                                                                   | V <sub>LCD2</sub>    | (Note 5)                                                                                                                                                                                                                                                                                                                                                                                              | 1/4 bias                                                                    | 3.0                   | _    | 5.5                | V                                                   | V <sub>3</sub> ', V <sub>4</sub> , V <sub>5</sub>                             |

(Note 1) Applies to the voltage drop (V<sub>C</sub>) from V<sub>DD</sub>, V<sub>1</sub>, V<sub>4</sub> and V<sub>5</sub> to each COMMON pin (COM<sub>1</sub> to COM<sub>16</sub>) as well as to voltage drop (V<sub>S</sub>) from V<sub>DD</sub>, V<sub>2</sub>, V<sub>3</sub> and V<sub>5</sub> to each SEG pin (SEG<sub>1</sub> to SEG<sub>100</sub>) when 40 $\mu$ A is flowed through one COM or SEG pin. When output level is at V<sub>DD</sub>, V<sub>1</sub>, or V<sub>2</sub> level, 40 $\mu$ A is flowed out, while 40 $\mu$ A is flowed in when the output level is at V<sub>3</sub>, V<sub>4</sub> or V<sub>5</sub> level.

This occurs when 5V is input to  $V_{\text{DD}},\,V_1$  and  $V_2$  , and 0V is input to  $V_3,\,V_4$  and  $V_5.$

- (Note 2) Applies to the current value flowed in the pin V<sub>DD</sub>, in the case of V<sub>DD</sub> = 5V,  $V_{SS} = 0V$ ,  $V_1$ ,  $V_2 = 5V$ ,  $V_3$ ,  $V_4$ ,  $V_5 = 0V$  and  $V_5'$  is open.

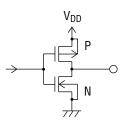

- (Note 3) Built-in R<sub>f</sub> oscillation circuit

Minimum wiring is required between  $OSC_R$  and  $OSC_2$ . Leave  $OSC_1$  open.

(Note 4) External clock input circuit

(Note 5) Input the voltage to  $V_5$ . (However,  $V_5$  cannot be used under  $V_{SS}$  voltage.)

| N (number of LCD lines) Pin | 1-line mode<br>Bias : 1/4     | 2-line mode<br>Bias : 1/5     |

|-----------------------------|-------------------------------|-------------------------------|

| V <sub>1</sub>              | $V_{DD} - \frac{V_{LCD}}{4}$  | $V_{DD} - \frac{V_{LCD}}{5}$  |

| V <sub>2</sub>              | $V_{DD} - \frac{V_{LCD}}{2}$  | $V_{DD} - \frac{2V_{LCD}}{5}$ |

| V <sub>3</sub>              | $V_{DD} - \frac{V_{LCD}}{2}$  | $V_{DD} - \frac{3V_{LCD}}{5}$ |

| V4                          | $V_{DD} - \frac{3V_{LCD}}{4}$ | $V_{DD} - \frac{4V_{LCD}}{5}$ |

| V <sub>5</sub>              | $V_{DD} - V_{LCD}$            | $V_{DD} - V_{LCD}$            |

At 1/4 bias : Connect V<sub>2</sub> and V<sub>3</sub> externally and leave V<sub>3</sub>' open. At 1/5 bias : Connect V<sub>3</sub> and V<sub>3</sub>' externally. V<sub>LCD</sub> is the LCD driving voltage. (For N [number of LCD lines], refer to

the explanation of the Function setting instruction of the instruction code.)

# **AC Characteristics**

|                                                                                           | Symbol            | Condition                                                                                          | Min.                        | Тур. | Max.  | Unit                             | Applicable Pir                                           |

|-------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------|-----------------------------|------|-------|----------------------------------|----------------------------------------------------------|

| R <sub>f</sub> clock oscillation frequency                                                | f <sub>OSC1</sub> | $R_{f} = 120 \text{ k}\Omega \pm 2\%$<br>(Note 1)                                                  | 175                         | 270  | 350   | kHz                              | 0SC1<br>0SC2                                             |

| External clock frequency                                                                  | f <sub>IN</sub>   | OSC <sub>R</sub> and OSC <sub>2</sub> are open.<br>Input a pulse to OSC <sub>1</sub> .<br>(Note 4) | 125                         | _    | 480   | kHz                              | OSC1                                                     |

| External clock duty                                                                       | f <sub>duty</sub> | (Note 2)                                                                                           | 45                          | 50   | 55    | %                                | OSC1                                                     |

| External clock rise time     t <sub>rf</sub> External clock fall time     t <sub>ff</sub> |                   | (Note 3)                                                                                           |                             | _    | 0.2   | μs                               | OSC1                                                     |

|                                                                                           |                   | (Note 3)                                                                                           | _                           | _    | 0.2   | μs                               | OSC1                                                     |

| Built-in R <sub>f</sub> clock<br>oscillation frequency                                    | f <sub>OSC2</sub> | OSC <sub>1</sub> is open. (Note 5)<br>Connect OSC <sub>R</sub> and OSC <sub>2</sub> .              | 140                         | 280  | 480   | kHz                              | OSC <sub>1</sub><br>OSC <sub>R</sub><br>OSC <sub>2</sub> |

| OS                                                                                        |                   | f between                                                                                          |                             |      |       |                                  | $SC_1$ and $R_f$ and                                     |

| OS<br>Note 2)                                                                             | G2 <b>→</b>       | Leave OS                                                                                           | 1                           |      | Annli | es to the                        | nulse to he                                              |

|                                                                                           |                   |                                                                                                    | 1                           |      |       | es to the<br>to OSC <sub>1</sub> | pulse to be                                              |

| (Note 2)<br>V <sub>DD</sub><br>f <sub>IN</sub><br>waveform                                | f                 | t <sub>HW</sub> t <sub>LV</sub>                                                                    | <u>V</u><br><u>VDD</u><br>2 |      |       |                                  | pulse to be                                              |

(Note 4) See Note 4 to "DC Characteristics."

(Note 5) See Note 3 to "DC Characteristics."

## **Switching Characteristics**

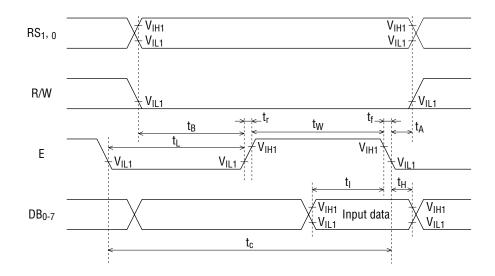

1. Timing for input from the CPU (write operation)

|                                                          |                | 1    | (*00 - 4.0 | 100.00, 10 = 0 |      |

|----------------------------------------------------------|----------------|------|------------|----------------|------|

| Parameter                                                | Symbol         | Min. | Тур.       | Max.           | Unit |

| R/W, RS <sub>0</sub> and RS <sub>1</sub> setup time      | t <sub>B</sub> | 40   | _          | _              | ns   |

| E "H" pulse width                                        | tw             | 220  | —          | —              | ns   |

| $R/W$ , $RS_0$ and $RS_1$ hold time                      | t <sub>A</sub> | 10   | _          | _              | ns   |

| E rise time                                              | tr             |      | _          | 20             | ns   |

| E fall time                                              | t <sub>f</sub> |      | _          | 20             | ns   |

| E "L" pulse width                                        | tL             | 210  | _          |                | ns   |

| E cycle time                                             | t <sub>C</sub> | 500  | _          | _              | ns   |

| DB <sub>0</sub> to DB <sub>7</sub> input data setup time | tı             | 100  | _          | _              | ns   |

| DB <sub>0</sub> to DB <sub>7</sub> input data hold time  | t <sub>H</sub> | 10   | _          | _              | ns   |

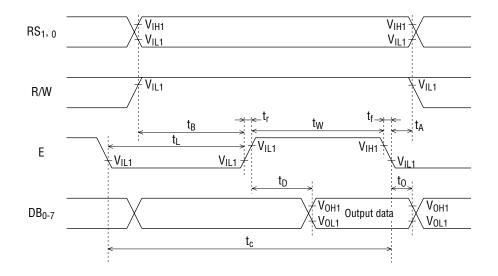

#### 2. Timing for output to the CPU (read operation)

|                                                     | 1              | 1    | (V <sub>DD</sub> = 4.5 1 | to 5.5V, Ta = -3 | 80 to +85°C) |

|-----------------------------------------------------|----------------|------|--------------------------|------------------|--------------|

| Parameter                                           | Symbol         | Min. | Тур.                     | Max.             | Unit         |

| R/W, RS <sub>0</sub> and RS <sub>1</sub> setup time | t <sub>B</sub> | 40   | _                        |                  | ns           |

| E "H" pulse width                                   | tw             | 220  | _                        | _                | ns           |

| R/W, RS <sub>0</sub> and RS <sub>1</sub> hold time  | t <sub>A</sub> | 10   | _                        | _                | ns           |

| E rise time                                         | tr             |      | —                        | 20               | ns           |

| E fall time                                         | t <sub>f</sub> | _    | —                        | 20               | ns           |

| E "L" pulse width                                   | tL             | 210  | _                        | —                | ns           |

| E cycle time                                        | t <sub>C</sub> | 500  | _                        | —                | ns           |

| $DB_0$ to $DB_7$ data ouput delay time              | t <sub>D</sub> | _    | —                        | 150              | ns           |

| $DB_0$ to $DB_7$ data ouput hold time               | to             | 20   | _                        | _                | ns           |

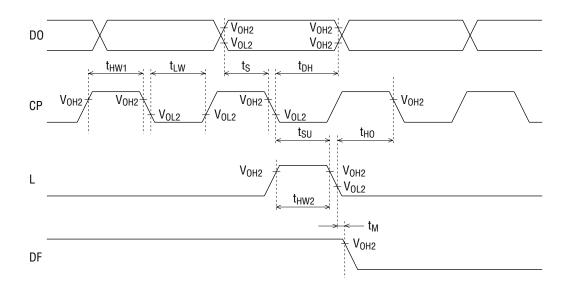

## 3. Timing for output to character extension IC

|                    |                  | 1     | (V <sub>DD</sub> = 4.5 1 | to 5.5V, Ta = -3 | 80 to +85°C) |

|--------------------|------------------|-------|--------------------------|------------------|--------------|

| Parameter          | Symbol           | Min.  | Тур.                     | Max.             | Unit         |

| CP "H" pulse width | t <sub>HW1</sub> | 800   | _                        | _                | ns           |

| CP "L" pulse width | t <sub>LW</sub>  | 800   | _                        | _                | ns           |

| DO setup time      | ts               | 300   | _                        | _                | ns           |

| DO hold time       | t <sub>DH</sub>  | 300   | _                        | _                | ns           |

| L clock setup time | t <sub>SU</sub>  | 500   | _                        | _                | ns           |

| L clock hold time  | t <sub>HO</sub>  | 100   | _                        | _                | ns           |

| L "H" pulse width  | t <sub>HW2</sub> | 800   | _                        | _                | ns           |

| DF delay time      | t <sub>M</sub>   | -1000 | _                        | 1000             | ns           |

## FUNCTIONAL DESCRIPTION

1. Instruction Register (IR), Data Register (DR), Contrast Register (CR)

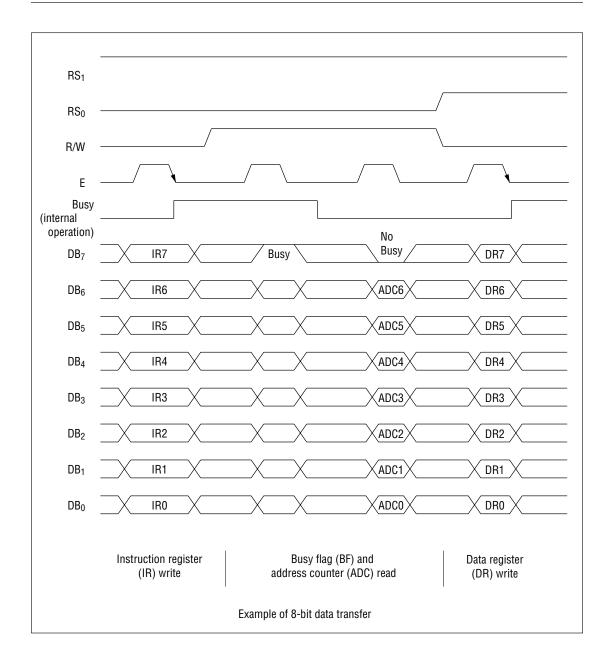

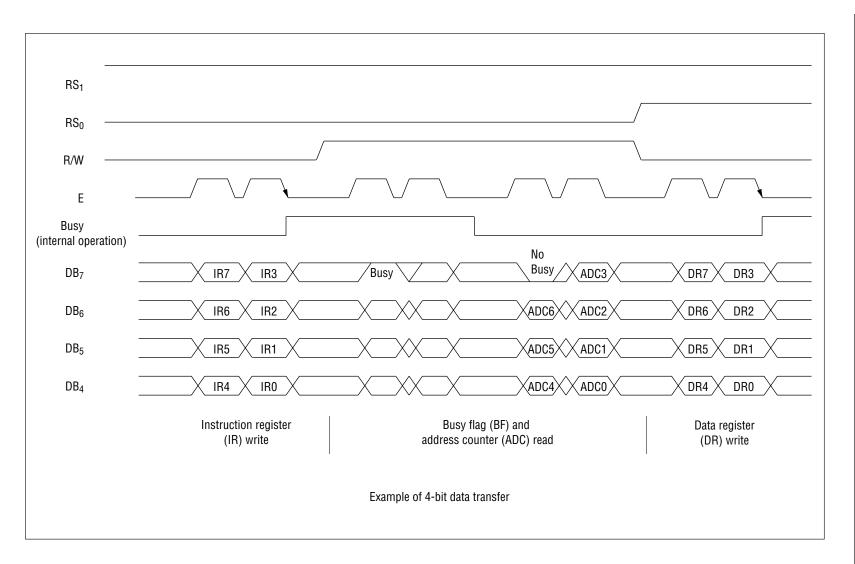

These three registers are selected by the register selector pins, RS<sub>0</sub> and RS<sub>1</sub>.

When  $RS_0$  and  $RS_1$  are "H" level input, the DR is selected and when  $RS_0 = "L"$  level input and  $RS_1 = "H"$ , the IR is selected. On the other hand, when  $RS_0$  and  $RS_1$  are "L" level input, the CR is selected. (When  $RS_0 = "H"$  level input and  $RS_1 = "L"$ , the registers are ignored.)

The IR is used to store the address codes for the display data RAM (DD RAM) or character generator RAM (CG RAM) and instruction codes.

The IR can be written into, but not be read out by the microcomputer (CPU).

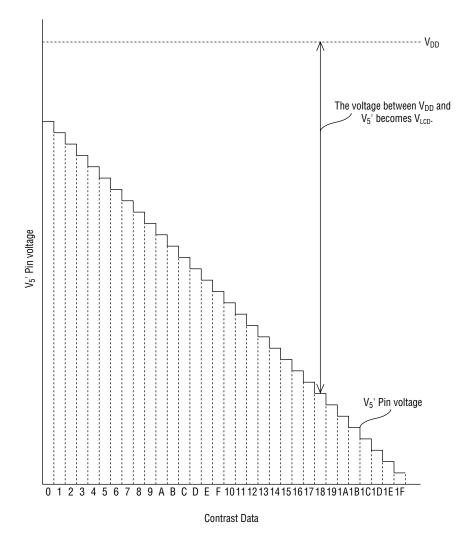

The CR can be used to read out and write. The CR values provide 0 to 1F (hexadecimal) and when this value is 0,  $V_{LCD}$  is lowest. On the other hand, when it is 1F, it is highest. (The initial value is 1F.) Therefore, the contrast can be adjusted by varying the CR value (providing that  $V_5$  and  $V_5$ ' are connected).

The DR is used to write into/read out the data to/from the DD RAM or CG RAM.

The data written to the DR by the CPU is automatically written to the DD RAM or CG RAM as an internal operation.

When an address code is written to the IR, the data (of the specified address) is automatically transferred from the DD RAM or CG RAM to the DR. By having the CPU subsequently read the DR (from the DR data), it is possible to verify the DD RAM or CG RAM data.

After the writing of the DR by the CPU, the DD RAM or CG RAM of the next address is selected to be ready for the next CPU writing. Likewise, after the reading out of the DR by the CPU, the DD RAM or CG RAM data is read out by the DR to be ready for the next CPU reading.

Write/read to and from the three registers is carried out by the READ/WRITE (R/W) pin.

| R/W | RS <sub>0</sub> | RS <sub>1</sub> | Function                                         |

|-----|-----------------|-----------------|--------------------------------------------------|

| L   | L               | Н               | IR write                                         |

| Н   | L               | Н               | Read of busy flag (BF) and address counter (ADC) |

| L   | Н               | Н               | DR write                                         |

| Н   | Н               | Н               | DR read                                          |

| L   | L               | L               | CR write                                         |

| Н   | L               | L               | CR read                                          |

Table 1 Register and R/W pins function table

#### 2. Busy Flag (BF)

When the busy flag output is at "H", it indicates that the MSM6562B-xx is engaged in internal operation.

When the busy flag is at "H" level, any new instruction is ignored.

When R/W = "H",  $RS_0 = "L"$ , and  $RS_1 = "H"$ , the busy flag is output from  $DB_7$ .

New instruction should be input when BF is "L" level.

When the busy flag is set to "H", the output code of the address counter (ADC) are undefined.

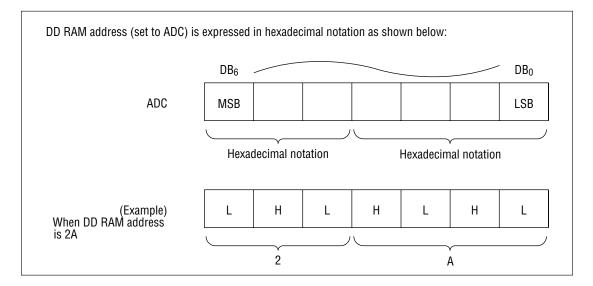

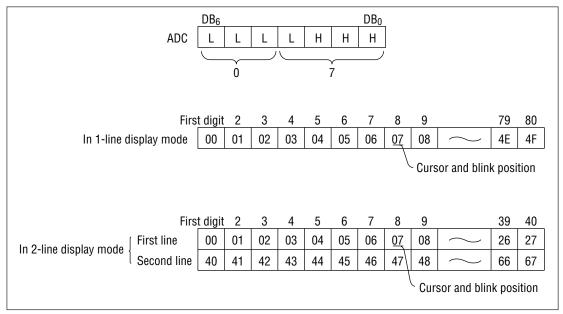

#### 3. Address Counter (ADC)

The address counter (ADC) allocates the address for the DD RAM and CG RAM and also for the cursor display.

When the instruction code for the DD RAM address or CG RAM address setting is input to the IR, after deciding whether it is the DD RAM or CG RAM, the address code is transferred from the IR to the ADC. After writing (reading) the display data to (from) the DD RAM or CG RAM, the ADC is automatically incremented (decremented) by 1 as its internal operation.

The data of the ADC is output to  $DB_0 - DB_6$  under the conditions that R/W = "H",  $RS_0 = "L"$ ,  $RS_1 = "H"$  and BF = "L".

#### 4. Timing Generator Circuit

This circuit generates timing signals used for internal operations upon receipt of CPU instruction. It also generates timing signals for activating such internal circuits as the DD RAM, CG RAM and CG ROM.

It is so designed that the internal operation caused by accessing from the CPU will not interfere with the internal operation caused by the LCD display.

Consequently, when data is written from the CPU to DD RAM no ill effect, e.g., flickering occurs in portions other than the display where the data is written.

In addition, the circuit generates transfer signals to the character extension IC (MSM5259).

#### 5. Display Data RAM (DD RAM)

This RAM is used to store the display data of 8-bit character codes (see Table 2). DD RAM address corresponds to the display position of the LCD. The correspondence between the two is described in the following.

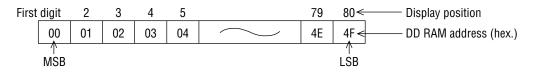

1-1) Correspondence between address and display position in the 1-line display mode

1-2) When the MSM6562B-xx alone is used, up to 20 characters can be displayed from the first digit to the twentieth digit.

| First c | digit | 2  | 3  | 4  |        | 19 | 20 |

|---------|-------|----|----|----|--------|----|----|

|         | 00    | 01 | 02 | 03 | $\sim$ | 12 | 13 |

When the display is shifted by instruction, the correspondence between the LCDdisplayposition and the DD RAM address changes as shown below:

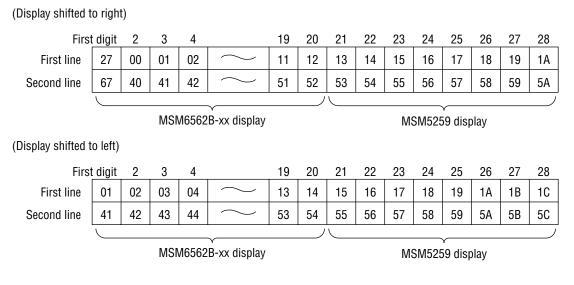

1-3) When the MSM6562B-xx is used with one MSM5259, up to 28 characters can be displayed from the first digit to the twenty-eighth digit as shown below:

| First | digit | 2  | 3   | 4       |              | 19 | 20 | 21 | 22 | 23  | 24     | 25      | 26  | 27 | 28 |

|-------|-------|----|-----|---------|--------------|----|----|----|----|-----|--------|---------|-----|----|----|

|       | 00    | 01 | 02  | 03      | $\sim$       | 12 | 13 | 14 | 15 | 16  | 17     | 18      | 19  | 1A | 1B |

|       |       |    |     |         | ×            |    | )  |    |    |     |        |         |     |    |    |

|       |       |    |     |         | ,<br>        |    |    |    |    |     | 0.4505 |         |     |    |    |

|       |       |    | MSN | /165621 | B-xx display |    |    |    |    | IV  | SM525  | b9 disp | lay |    |    |

|       |       |    | MSN | /165621 | B-xx display |    |    |    |    | IVI | SM525  | o9 disp | lay |    |    |

When the display is shifted by instruction, the correspondence between the LCD display and DD RAM address changes as shown below:

| st digit | t 2 | 3  | 4        |                     | 19                                                             | 20                                                                                   | 21                                                                                              | 22                                                                                                 | 23                                                                                                                    | 24                                                                                   | 25                                                                                                                                         | 26                                                                                                                       | 27                                                                                                                                | 28                                                                                                                                         |

|----------|-----|----|----------|---------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 4F       | 00  | 01 | 02       | $\sim$              | 11                                                             | 12                                                                                   | 13                                                                                              | 14                                                                                                 | 15                                                                                                                    | 16                                                                                   | 17                                                                                                                                         | 18                                                                                                                       | 19                                                                                                                                | 1A                                                                                                                                         |

|          |     |    |          |                     |                                                                | ر                                                                                    |                                                                                                 |                                                                                                    |                                                                                                                       |                                                                                      | ×                                                                                                                                          |                                                                                                                          |                                                                                                                                   |                                                                                                                                            |

|          |     | N  | NSM6     | 562B-xx disp        | lay                                                            |                                                                                      |                                                                                                 |                                                                                                    | MS                                                                                                                    | M525                                                                                 | 9 dis                                                                                                                                      | play                                                                                                                     |                                                                                                                                   |                                                                                                                                            |

|          |     |    |          |                     |                                                                | $\frown$                                                                             | $\frown$                                                                                        |                                                                                                    |                                                                                                                       |                                                                                      | <u> </u>                                                                                                                                   |                                                                                                                          |                                                                                                                                   | $\frown$                                                                                                                                   |

| 01       | 02  | 03 | 04       | $\langle$           | 13                                                             | 14                                                                                   | 15                                                                                              | 16                                                                                                 | 17                                                                                                                    | 18                                                                                   | 19                                                                                                                                         | 1A                                                                                                                       | 1B                                                                                                                                | 10                                                                                                                                         |

|          | 4F  |    | 4F 00 01 | 4F 00 01 02<br>MSM6 | 4F         00         01         02           MSM6562B-xx disp | 4F         00         01         02         11           MSM6562B-xx         display | 4F         00         01         02         11         12           MSM6562B-xx         display | 4F         00         01         02         11         12         13           MSM6562B-xx display | 4F         00         01         02         11         12         13         14           MSM6562B-xx         display | 4F     00     01     02     11     12     13     14     15       MSM6562B-xx display | 4F         00         01         02         11         12         13         14         15         16           MSM6562B-xx         MSM525 | 4F       00       01       02       11       12       13       14       15       16       17         MSM6562B-xx display | 4F       00       01       02       11       12       13       14       15       16       17       18         MSM6562B-xx display | 4F       00       01       02       11       12       13       14       15       16       17       18       19         MSM6562B-xx display |

1-4) Since the MSM6562B-xx has a DD RAM with a capacity of 80 characters, up to 8 devices of MSM5259 can be connected to MSM6562B-xx so that 80 characters can be displayed.

| First<br>digit 2 3 4 19 20 21 22 23 | 24 25 26 27     | 7 28 29 30                 | 77 78 79 80                                                                                    |

|-------------------------------------|-----------------|----------------------------|------------------------------------------------------------------------------------------------|

| 00 01 02 03 ~ 12 13 14 15 16        | 17 18 19 14     | A 1B 1C 1D ~~              | 4C 4D 4E 4F                                                                                    |

|                                     | ~               |                            |                                                                                                |

| MSM6562B-xx display MSM5            | 259 (1) display | MSM5259<br>(2)-(7) display | MSM5259<br>(8) display                                                                         |

|                                     |                 | SE                         | (Only the half of the<br>egment output pins,<br>O <sub>1</sub> to O <sub>20</sub> , are used.) |

2-1) Correspondence between address and display position in the 2-line display mode

| First       | digit | 2  | 3  | 4  | 5  |        | 39 | 40 ← Display position     |    |

|-------------|-------|----|----|----|----|--------|----|---------------------------|----|

| First line  | 00    | 01 | 02 | 03 | 04 | $\sim$ | 26 | 27 < DD RAM address (hex. | .) |

| Second line | 40    | 41 | 42 | 43 | 44 | $\sim$ | 66 | 67 <                      |    |

<sup>(</sup>Note) Note that the last address of the first line and the leading address of the second line are not consecutive.

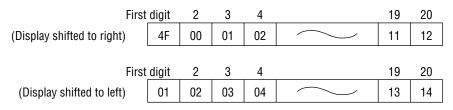

2-2) When the MSM6562B-xx alone is used, up to 40 characters (20 character × 2 lines) can be displayed from the first digit to the twentieth digit.

| First       | digit | 2  | 3  | 4  |           | 19 | 20 |

|-------------|-------|----|----|----|-----------|----|----|

| First line  | 00    | 01 | 02 | 03 | $\sim$    | 12 | 13 |

| Second line | 40    | 41 | 42 | 43 | $\langle$ | 52 | 53 |

When the display is shifted by instruction, the correspondence between the LCD display position and the DD RAM address changes as shown below:

|                            | First       | digit | 2  | 3  | 4  |           | 19 | 20 |

|----------------------------|-------------|-------|----|----|----|-----------|----|----|

|                            | First line  | 27    | 00 | 01 | 02 | $\langle$ | 11 | 12 |

| (Display shifted to right) | Second line | 67    | 40 | 41 | 42 | $\Big)$   | 51 | 52 |

|                            |             |       |    |    |    |           |    |    |

|                            | First       | digit | 2  | 3  | 4  |           | 19 | 20 |

|                            | First line  | 01    | 02 | 03 | 04 | $\langle$ | 13 | 14 |

| (Display shifted to left)  | Second line | 41    | 42 | 43 | 44 | $\langle$ | 53 | 54 |

2-3) When the MSM6562B-xx is used with one MSM5259, up to 56 characters (28 characters × 2 lines) can be displayed from the first digit to the twenty-eighth digit as shown below:

| First               | t digit | 2  | 3  | 4  |        | 19 | 20 | 21 | 22 | 23 | 24    | 25           | 26   | 27 | 28 |

|---------------------|---------|----|----|----|--------|----|----|----|----|----|-------|--------------|------|----|----|

| First line          | 00      | 01 | 02 | 03 | $\sim$ | 12 | 13 | 14 | 15 | 16 | 17    | 18           | 19   | 1A | 1B |

| Second line         | 40      | 41 | 42 | 43 | $\sim$ | 52 | 53 | 54 | 55 | 56 | 57    | 58           | 59   | 5A | 5B |

|                     |         |    |    |    |        |    | )  |    |    |    |       |              |      |    | J  |

| MSM6562B-xx display |         |    |    |    |        |    |    |    |    | MS | SM525 | ,<br>59 disp | olay |    |    |

When the display is shifted by instruction, the correspondence between the LCD display position and the DD RAM address changes as shown below:

2-4) Since the MSM6562B-xx has a DD RAM with a capacity of 80 characters, up to 3 devices of MSM5259 can be connected to the MSM6562B-xx in the 2-line display mode.

| First<br>digit | t 2 | 3   | 4    |           | 19  | 20 | 21 | 22 | 23  | 24  | 25  | 26   | 27   | 28 | 29 | 30   |                                                    | 37    | 38          | 39   | 40           |

|----------------|-----|-----|------|-----------|-----|----|----|----|-----|-----|-----|------|------|----|----|------|----------------------------------------------------|-------|-------------|------|--------------|

| 00             | 01  | 02  | 03   | $\langle$ | 12  | 13 | 14 | 15 | 16  | 17  | 18  | 19   | 1A   | 1B | 1C | 1D   | $\langle$                                          | 24    | 25          | 26   | 27           |

| 40             | 41  | 42  | 43   | $\langle$ | 52  | 53 | 54 | 55 | 56  | 57  | 58  | 59   | 5A   | 5B | 5C | 5D   | {                                                  | 64    | 65          | 66   | 67           |

| _              | N   | ISM | 6562 | 2B disp   | lay |    |    | MS | SM5 | 259 | (1) | disp | olay | ou |    | (Onl | 259<br>display<br>y the ha<br>i.e., O <sub>1</sub> | lf of | (3<br>the s | segm | play<br>ient |

#### 6. Character Generator ROM (CG ROM)

The CG ROM is used to generate  $5 \times 7$  dot (160 kinds) character patterns or  $5 \times 10$  dot (32 kinds) character patterns from an 8-bit DD RAM character code signal.

The correspondence of 8-bit character codes to character patterns is shown in Table 2. When the 8-bit character code of the CG ROM is written to the DD RAM, the character pattern of the CG ROM corresponding to the code is displayed on the LCD display position corresponding to the DD RAM address.

| Upper<br>Lower 4 bits<br>4 bits | MSB<br>0000   | 001 | 0   | 001 | 1  | 010 | 00         | 010 | 01             | 011 | 0         | 011           | 1            | 101 | 0          | 101 | 1          | 110 | 0                | 110 | )1          | 111        | 0    | 111 | 1   |

|---------------------------------|---------------|-----|-----|-----|----|-----|------------|-----|----------------|-----|-----------|---------------|--------------|-----|------------|-----|------------|-----|------------------|-----|-------------|------------|------|-----|-----|

| 0000<br>LSB                     | CG<br>RAM (1) |     |     | 0   | Ø  | @   | 3)         | Р   |                | ١   |           | р             | F=-          |     |            | _   |            | タ   | 5                | Ξ   | Ξ.          | α          | Ċ    | Р   | p   |

| 0001                            | (2)           | !   | !   | 1   | 1  | А   | <b>[-]</b> | Q   | Q              | a   | <u>.</u>  | q             | ·=ij         | o   | C!         | 7   | 7          | チ   | Ŧ                | 4   | í,          | ä          | ä    | q   |     |

| 0010                            | (3)           | "   | 11  | 2   | 2  | В   | E          | R   | R              | b   | <u>L-</u> | r             | }            | Γ   | I          | イ   | •1         | ッ   | Ņ                | ×   | ×           | β          | ß    | Θ   | 8   |

| 0011                            | (4)           | #   | 井   | 3   |    | С   | <b>I</b>   | S   | 5              | C   | <b>(</b>  | S             | <u> </u>     | J   | j          | ウ   | ┍┶╕        | テ   | · <del>7</del> - | Ŧ   | <b>4</b> =: | ε          | Ξ.   | ∞   | 67  |

| 0100                            | (5)           | \$  | ÷   | 4   | 4  | D   | D          | Т   | Ī              | d   |           | t             | ÷.           | •   | ••         | I   |            | ۲   | ŀ                | ヤ   | <b>†</b> 7  | μ          | ļ_4  | Ω   | 52  |

| 0101                            | (6)           | %   | 7   | 5   | 5  | Е   | <u> </u>   | U   |                | е   | e         | u             | i_4          | •   | =          | オ   | -4         | ナ   | - <b></b>        | ユ   | -1          | σ          | G    | ü   | I_4 |

| 0110                            | (7)           | &   | 8   | 6   | 6  | F   | <b>F</b>   | V   | Ų              | f   | Ŧ.        | ۷             | IJ,          | F   | ij         | ታ   | <u>]</u> ] | Ξ   | -                | Э   |             | ρ          | ρ    | Σ   | Ξ   |

| 0111                            | (8)           | ,   | 7   | 7   | 7  | G   | G          | W   | W              | g   | 53        | W             | IJ           | 7   | 77         | +   | =          | ヌ   | 37               | ラ   |             | g          | ġ    | π   | JT  |

| 1000                            | (1)           | (   | ζ   | 8   | 8  | Η   | ŀ-i        | Х   | X              | h   | 6-1       | Х             | ×            | イ   | . <b>4</b> | ク   | ]          | ネ   | *-<br>-*-        | IJ  | Ņ           | $\sqrt{-}$ | .,[" | X   | X   |

| 1001                            | (2)           | )   | )   | 9   | 9  | I   | I          | Y   | Y              | i   | i         | у             | <u>ہ۔</u>    | ウ   | <u></u> j  | ケ   | ·۲         | )   | J                | ル   | Iİ.         | -1         | -!   | y   | ii  |

| 1010                            | (3)           | *   | :4: | :   |    | J   | . <u> </u> | Ζ   | Z              | j   | j         | Z             | -7.          | Т   |            | ٦   |            | Л   | 1Ì               | V   | <b>.</b>    | j          | .1   | 千   | Ŧ   |

| 1011                            | (4)           | +   |     | ;   | 5  | Κ   | K          | [   | E              | k   | k         | {             | {            | オ   | 77         | サ   | ii.        | Ł   | i                |     |             | х          | ×    | 万   | 乃   |

| 1100                            | (5)           | ,   |     | <   | •: | L   | İ.         | ¥   | -11-1<br>-11-1 | I   | 1         |               | I            | ヤ   | 1-:        | シ   | Ξ.!        | フ   | 7                | ワ   | 7           | ¢          | ¢    | 円   | F9  |

| 1101                            | (9)           | -   |     | =   | == | М   | ŀi         | ]   |                | m   | m         | }             | }            | ב   | -1         | ス   | Z          | ^   | ^                | ン   |             | £          | Ł    | ÷   | •   |

| 1110                            | (7)           |     |     | >   | >  | N   | ŀŀ         | ٨   |                | n   | r 1       | $\rightarrow$ |              | Э   | 3          | セ   | 77         | ホ   | <b>i-</b> -      | ۲   |             | n          | F    |     |     |

| 1111                            | (8)           | /   | /   | ?   | ?  | 0   |            | _   |                | 0   | $\odot$   | ←             | - <b>£</b> - | ッ   | • • • •    | У   | •          | ੨   | ~?               | o   | Ei          | Ö          | Ö    |     |     |

Table 2 Character codes and character patterns of standard code (MSM6562B-01)

18/50

7. Character Generator RAM (CG RAM)

The CG RAM is used to display user's original character patterns other than those stored in the CG ROM.

The CG RAM has the capacity (64 bytes = 512 bits) to write 8 kinds for  $5 \times 7$  dots or 4 kinds for  $5 \times 10$  dots.

When displaying character patterns stored in the CG RAM, write 8-bit character codes (00 to 07 or 08 to 0F; hex.) shown on the left in Table 2 to the DD RAM. It is then possible to output the character pattern to the LCD display position corresponding to the DD RAM address.

The following is a description on how to write and read character patterns to and from the CG RAM.

- (1) When the character pattern is  $5 \times 7$  dots (see Table 3)

- Method of writing character pattern into the CG RAM by the CPU : The CG RAM address bits 0 to 2 correspond to the line position of the character pattern. First, set increment or decrement by the CPU, and then input the CG RAM address. After this, write character pattern into the CG RAM through DB<sub>0</sub> to DB<sub>7</sub> line by line.

$DB_0$  to  $DB_7$  correspond to the CG RAM data bits 0 to 7 in Table 3.

The display of the character pattern is turned on when "H" is set as input data, while it is turned off when "L" is set as the input data.

Since the ADC is automatically incremented or decremented by 1 after writing the data to the CG RAM, it is not necessary to set the CG RAM address again.

When performing a cursor indication, set to "0" all the input data for the line the CG RAM address bits 0 to 2 of which are all "1".

Although the CG RAM data bits  $0 \sim 4$  are output to the LCD as display data, the CG RAM data bits  $5 \sim 7$  are not. It is possible, however, to use the CG RAM as a data RAM.

• Method of displaying the CG RAM character pattern to the LCD : The CG RAM is selected when high-order 4 bits of the character code are all "L". Since bit 3 of the character code is invalid, the display of "0" in Table 3 is selected by character code "00" or "08" (hex.). When the 8-bit character code of the CG RAM is written to the DD RAM, the character pattern of the CG RAM is displayed on the LCD display position corresponding to the DD RAM address. (DD RAM data bits 0 to 2 correspond to CG RAM address bits 3 to 5.)

- (2) When the character pattern is  $5 \times 10$  dots (see Table 4).

- Method of writing character pattern into the CG RAM by the CPU :

The CG RAM address bits 0 to 3 correspond to the line position of the character pattern. First, set increment or decrement by the CPU, and then input the CG RAM address.

After this, write the character pattern into the CG RAM through  $DB_0$  to  $DB_7$  line by line.  $DB_0$  to  $DB_7$  correspond to the CG RAM data bits 0 to 7, in Table 4.

The display of the character pattern is turned on when "H" is set as the input data, while it is turned off when "L" is set as the input data.

Since the ADC is automatically incremented or decremented by 1 after writing the data to the CG RAM, it is not necessary to set the CG RAM address again.

When performing a cursor indication, set to "0" all the input data for the line the CG RAM address bits 0 to 2 are all "1".

CG RAM data is displayed on the LCD when the CG RAM data ranges from CG RAM data bits 0 to 4 and the CG RAM addresses (address bits 0 to 3) are "0" to "A" (hex.). Other CG RAM data is not displayed on the LCD (that is, when the CG RAM data ranges from CG RAM data bits 5 to 7 and the CG RAM addresses (address bits 0 to 3) are "B" to "F" (hex.)). It is possible, however, to read such CG RAM data through DB<sub>0</sub> to DB<sub>7</sub>.

• Method of displaying the CG RAM character pattern to the LCD : The CG RAM is selected when high-order 4 bits of the character code are all "L". Since bits 0 and 3 of the character code are invalid, the display of " $\beta$ " in Table 4 is selected by character codes "00", "01", "08" and "09" (hex.).

When the 8-bit character code of the CG RAM character code is written to the DD RAM, the character pattern of the CG RAM is displayed on the LCD display position corresponding to the DD RAM address.

(DD RAM data bits 1 to 2 correspond to CG RAM address bits 4 to 5.)

Table 3Example of the CG RAM data (character pattern) corresponding to the CG RAM<br/>addresses when the character pattern is 5×7 dots, and relationship between character<br/>patterns and the DD RAM data

| CG RAM address                                             | CG RAM data<br>(character pattern)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DD RAM data<br>(character code) |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|