# **MSM64167E**

### **User's Manual**

CMOS 4-bit microcontroller

FIRST EDITION ISSUE DATE: Dec. 1999

FEUL64167E-01

NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 1999 Oki Electric Industry Co., Ltd.

#### Introduction

The MSM64167E is a high-performance microcontroller that uses a 4-bit CPU core of nX-4/20 under Oki's original architecture to integrate peripheral functions.

This manual explains hardware of the MSM64167E.

For details of the nX-4/20 core instruction set, refer to the nX-4/20 Core Instruction Manual or nX-4/30 Core Instruction Manual.

#### Table of Contents

#### Chapter 1 Overview

| 1.1 | Overview                         | 1-1  |

|-----|----------------------------------|------|

| 1.2 | Features                         | 1-1  |

| 1.3 | Block Diagram                    | 1-3  |

| 1.4 | Pin Configuration                | 1-4  |

| 1.5 | Description of Pins              | 1-7  |

|     | 1.5.1 Description of Each Pin    | 1-7  |

|     | 1.5.2 Connections of Unused Pins | 1-11 |

| 1.6 | Basic Timing                     | 1-12 |

#### Chapter 2 CPU

| 2.1 | Overv                          | iew                                       | . 2-1 |  |  |

|-----|--------------------------------|-------------------------------------------|-------|--|--|

| 2.2 | 2.2 Configuration of Registers |                                           |       |  |  |

|     | 2.2.1                          | Registers A, B, H, L, X and Y             | . 2-3 |  |  |

|     | 2.2.2                          | Program Counter (PC)                      | . 2-4 |  |  |

|     | 2.2.3                          | Stack Pointer (SP)                        | . 2-4 |  |  |

|     | 2.2.4                          | Carry Flag (C)                            | . 2-4 |  |  |

| 2.3 | Memo                           | bry Space                                 | . 2-5 |  |  |

|     | 2.3.1                          | Program Memory                            | . 2-5 |  |  |

|     | 2.3.2                          | Data Memory                               | . 2-6 |  |  |

|     |                                | 2.3.2.1 Data Memory Area                  | . 2-6 |  |  |

|     |                                | 2.3.2.2 Bank Specification of Data Memory | . 2-7 |  |  |

|     |                                | 2.3.2.3 Addressing Modes of Data Memory   | . 2-8 |  |  |

|     |                                |                                           |       |  |  |

#### Chapter 3 CPU Control Functions

| 3.1 | Overv                   | iew                       | 3-1 |  |

|-----|-------------------------|---------------------------|-----|--|

| 3.2 | 2 System Reset Function |                           |     |  |

|     | 3.2.1                   | System Reset Mode         | 3-2 |  |

|     |                         | Status at System Reset    |     |  |

| 3.3 |                         | 1ode                      |     |  |

|     |                         | Halt Mode Register (HALT) |     |  |

|     |                         | Operation in Halt Mode    |     |  |

|     |                         | •                         |     |  |

#### Chapter 4 Interrupt (INTC)

| Overv   | riew                                              | 4-1                                                                                                                                                                                                                              |

|---------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interru | upt Sequence                                      | 4-3                                                                                                                                                                                                                              |

| Interru | upt Control Registers                             | 4-4                                                                                                                                                                                                                              |

| 4.3.1   | Interrupt Request Registers (IRQ0, IRQ1 and IRQ2) | 4-4                                                                                                                                                                                                                              |

| 4.3.2   | Interrupt Enable Registers (IE0, IE1 and IE2)     | 4-7                                                                                                                                                                                                                              |

| 4.3.3   | Master Interrupt Enable Register (MIEF)           | 4-9                                                                                                                                                                                                                              |

|         | Interro<br>Interro<br>4.3.1<br>4.3.2              | Overview<br>Interrupt Sequence<br>Interrupt Control Registers<br>4.3.1 Interrupt Request Registers (IRQ0, IRQ1 and IRQ2)<br>4.3.2 Interrupt Enable Registers (IE0, IE1 and IE2)<br>4.3.3 Master Interrupt Enable Register (MIEF) |

#### Chapter 5 Clock Generation Circuit (2CLK)

| 5.1 | Overview                                    | -1 |

|-----|---------------------------------------------|----|

| 5.2 | Configuration of Clock Generation Circuit5- | -1 |

| 5.3 | Operation of Clock Generation Circuit5-     | -2 |

| 5.4 | Frequency Control Register (FCON)5          | -2 |

| 5.5 | System Clock Switching Timing               | -3 |

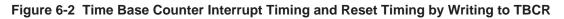

#### Chapter 6 Time Base Counter (TBC)

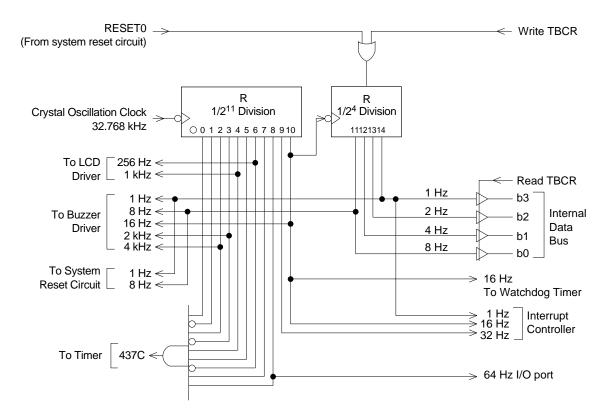

| 6.1 | Overview                           |

|-----|------------------------------------|

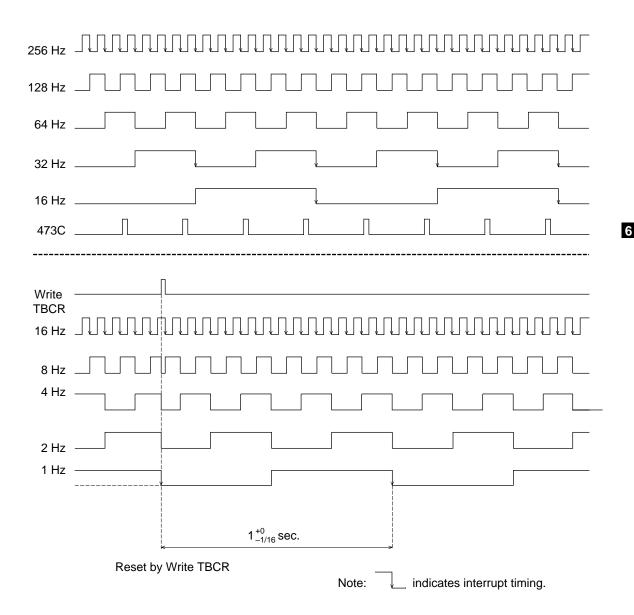

| 6.2 | Configuration of Time Base Counter |

|     | Operation of Time Base Counter     |

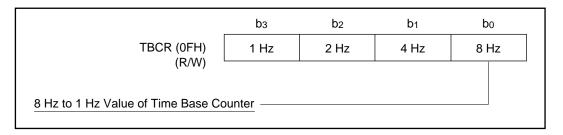

| 6.4 | Time Base Counter Register (TBCR)  |

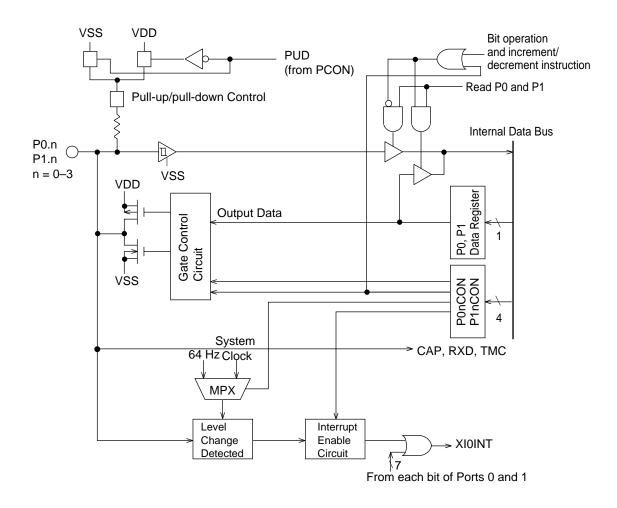

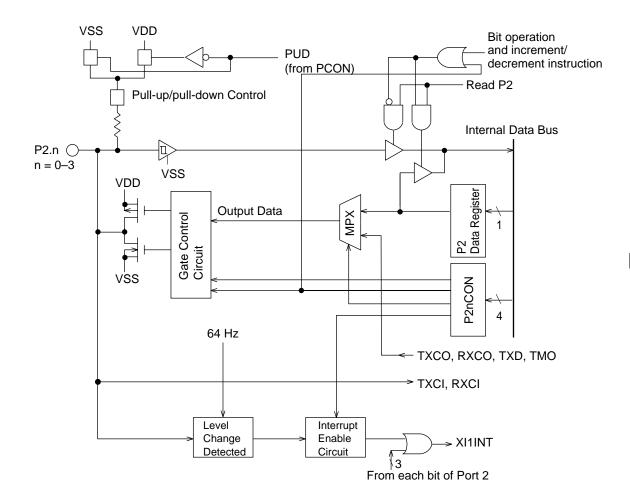

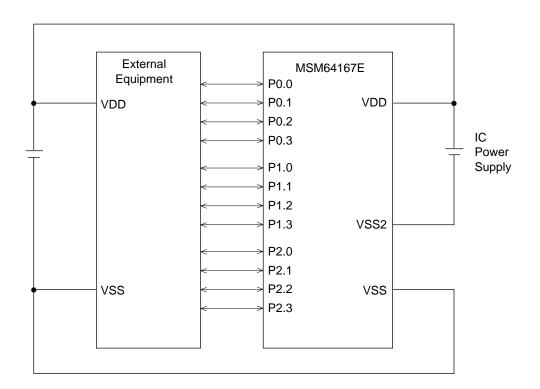

#### Chapter 7 Ports (P0, P1 and P2)

| 7.1 | Overv  | iew                                                               | . 7-1 |

|-----|--------|-------------------------------------------------------------------|-------|

| 7.2 | Port 0 | , Port 1 and Port 2 (P0.0–P0.3, P1.0–P1.3 and P2.0–P2.3)          | 7-2   |

|     | 7.2.1  | Configuration of Port 0, Port 1 and Port 2                        | 7-2   |

|     | 7.2.2  | Port 0, Port 1 and Port 2 Related Registers                       | 7-5   |

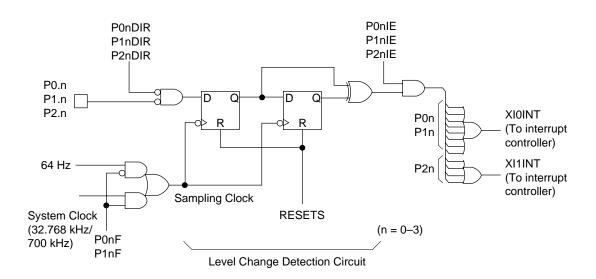

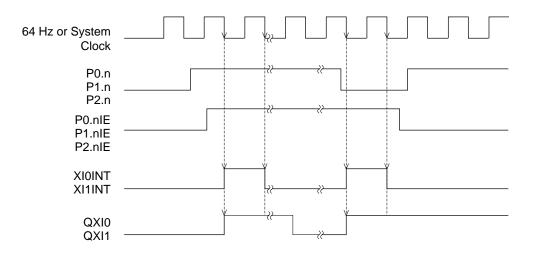

|     |        | External Interrupt Generation Timing of Port 0, Port 1 and Port 2 |       |

#### Chapter 8 Timer (TM)

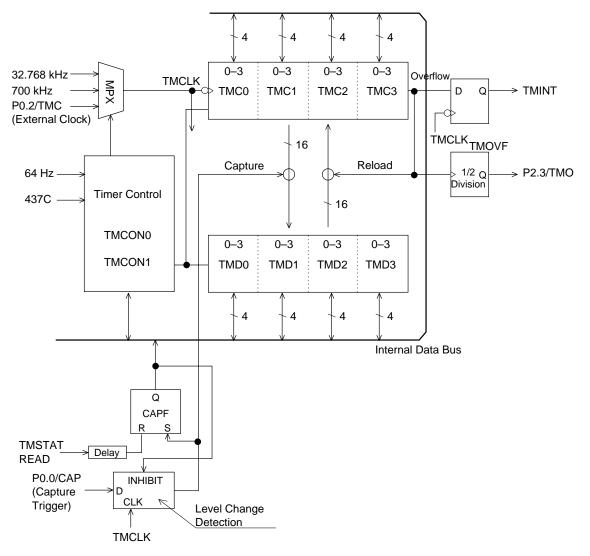

| 8.1 | Overv  | iew                                                              | 8-1  |

|-----|--------|------------------------------------------------------------------|------|

| 8.2 | Config | juration of Timer                                                | 8-1  |

| 8.3 | Opera  | tion of Timer                                                    | 8-2  |

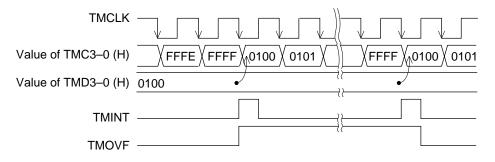

|     | 8.3.1  | Timer Clock (TMCLK)                                              | 8-2  |

|     | 8.3.2  | Timer Counter Registers 0–3 (TMC0–3)                             | 8-2  |

|     | 8.3.3  | Timer Data Registers 0-3 (TMD0-3)                                | 8-2  |

|     | 8.3.4  | Timer Interrupt Request (TMINT) and Timer Overflow Flag (TMOVF). | 8-2  |

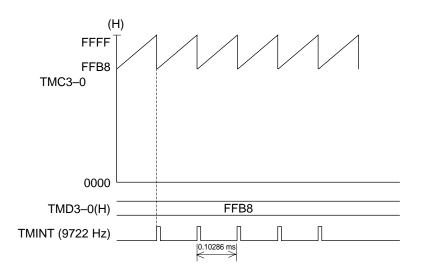

|     | 8.3.5  | Operation in Auto Reload Mode                                    | 8-3  |

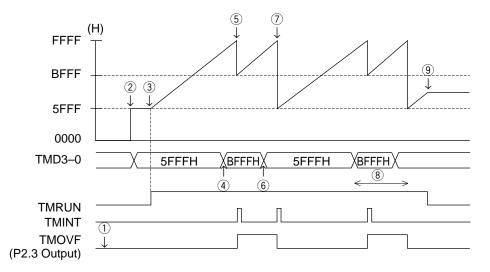

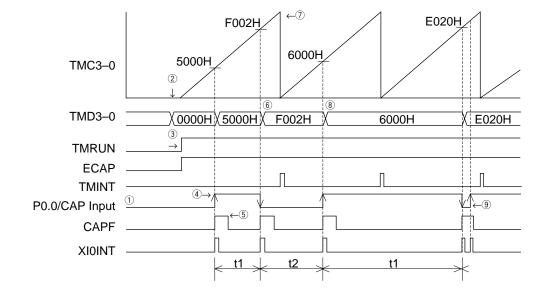

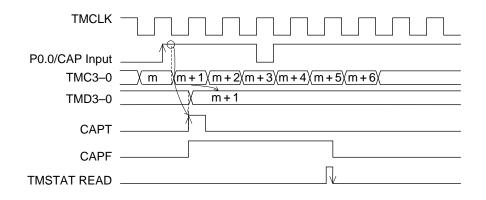

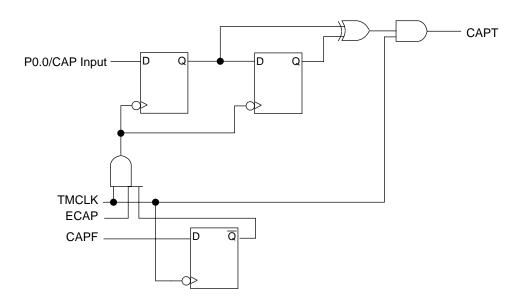

|     | 8.3.6  | Operation in Capture Mode                                        | 8-4  |

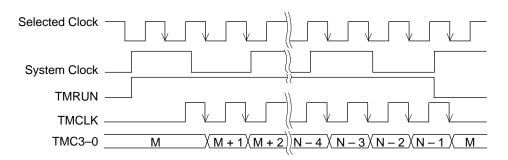

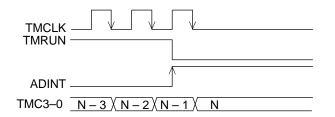

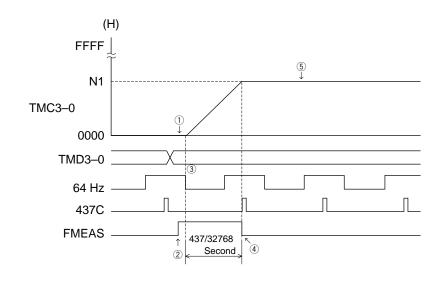

|     | 8.3.7  | Operation in Clock Frequency Measurement Mode                    | 8-7  |

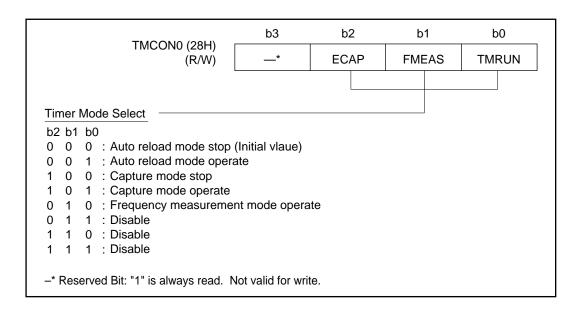

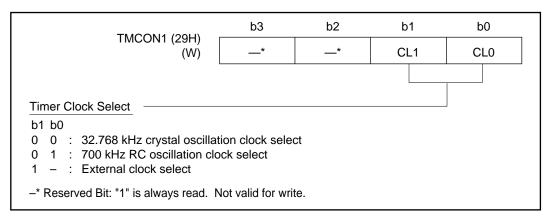

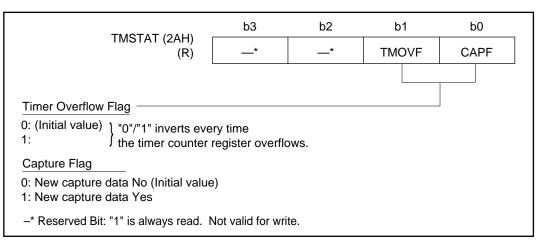

| 8.4 | Timer  | Related Registers                                                | 8-10 |

#### Chapter 9 Serial Port (SIOP)

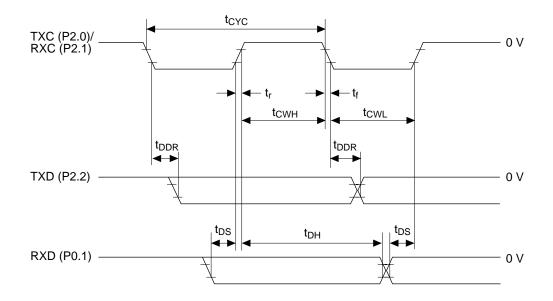

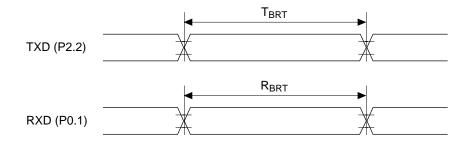

| 9.1 | Overview |                                                    |        |

|-----|----------|----------------------------------------------------|--------|

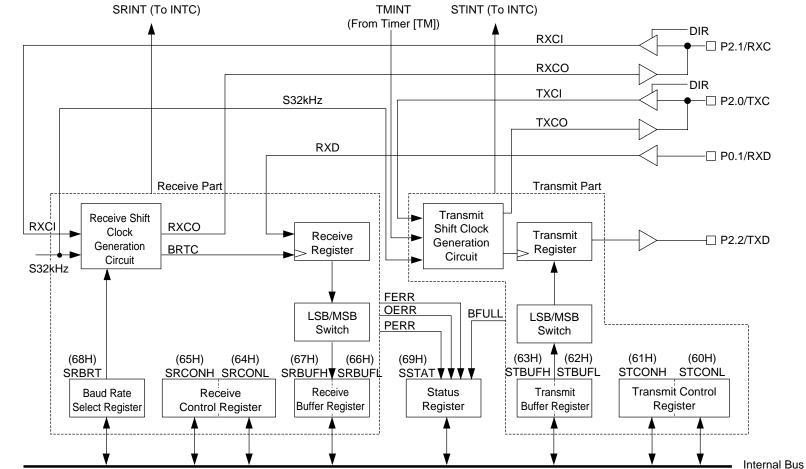

| 9.2 | Config   | guration of Serial Port                            | . 9-2  |

| 9.3 | Serial   | Port-Related Registers                             | . 9-4  |

|     | 9.3.1    | Transmit Control Register (STCONL, STCONH)         | . 9-4  |

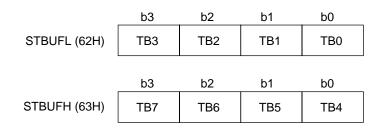

|     | 9.3.2    | Transmit Buffer Register (STBUFL, STBUFH)          | . 9-6  |

|     | 9.3.3    | Transmit Register                                  | . 9-6  |

|     | 9.3.4    | Receive Control Register (SRCONL, SRCONH)          | . 9-8  |

|     | 9.3.5    | Receive Register                                   | . 9-10 |

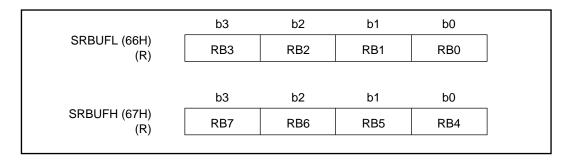

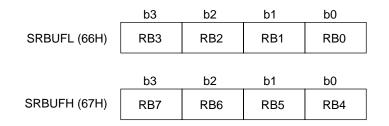

|     |          | Receive Buffer Register (SRBUFL, SRBUFH)           |        |

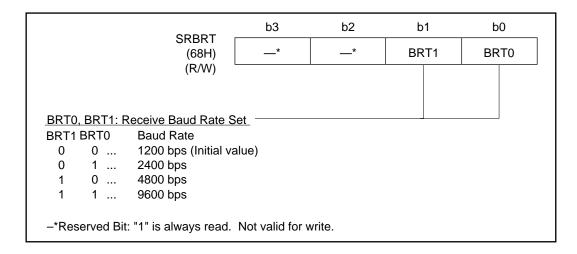

|     | 9.3.7    | Receive Baud Rate Setting Register (SRBRT)         | . 9-11 |

|     |          | Serial Status Register (SSTAT)                     |        |

| 9.4 | Opera    | ation of Serial Port                               | . 9-14 |

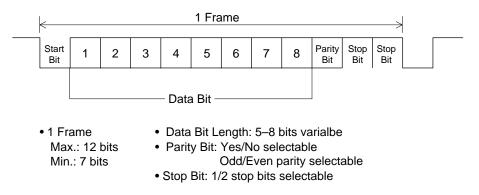

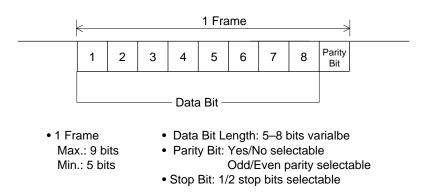

|     | 9.4.1    | Data Format                                        | . 9-14 |

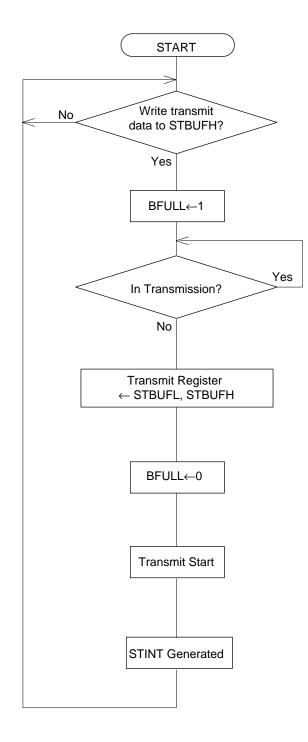

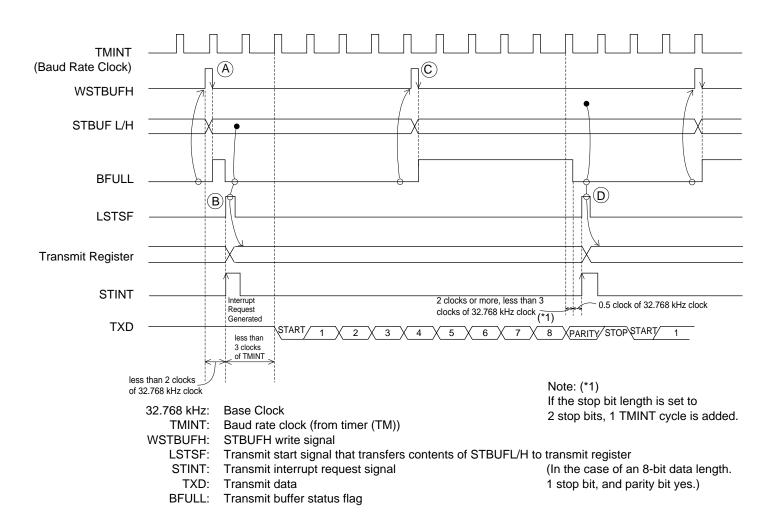

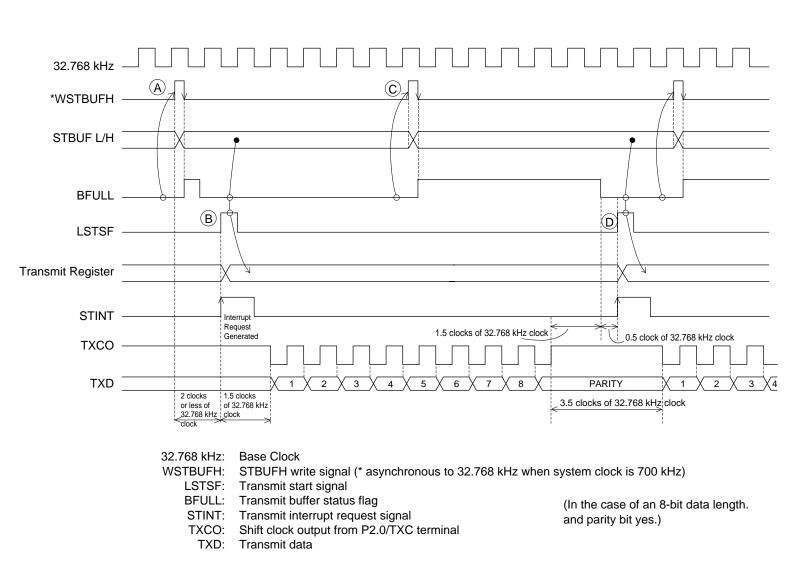

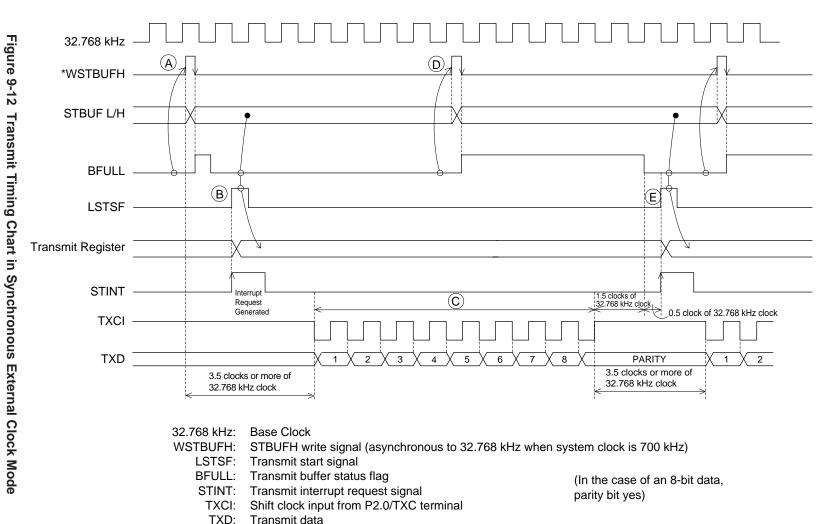

|     | 9.4.2    | Transmit Operation                                 | . 9-15 |

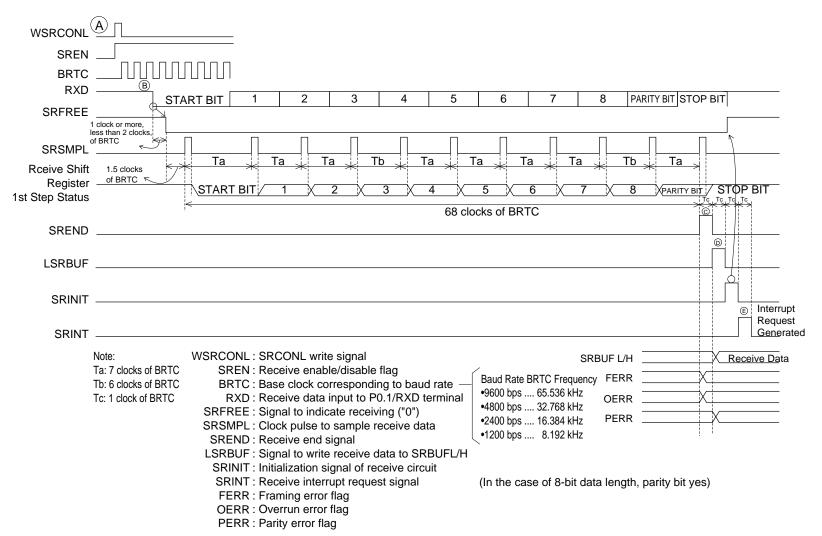

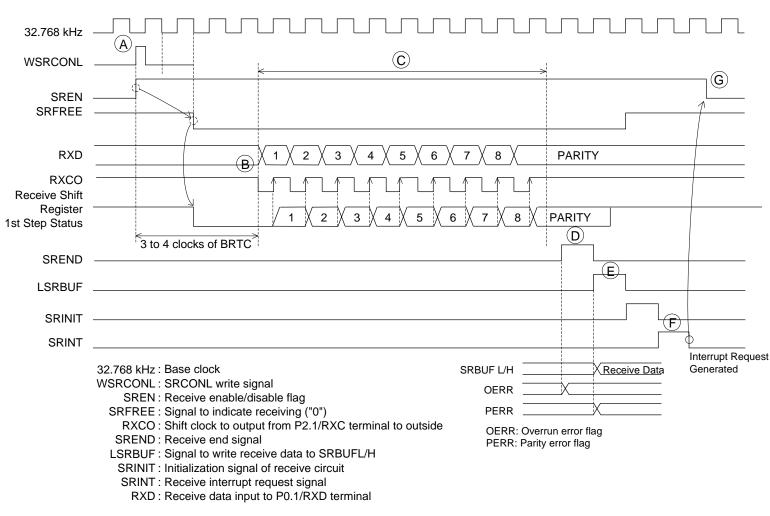

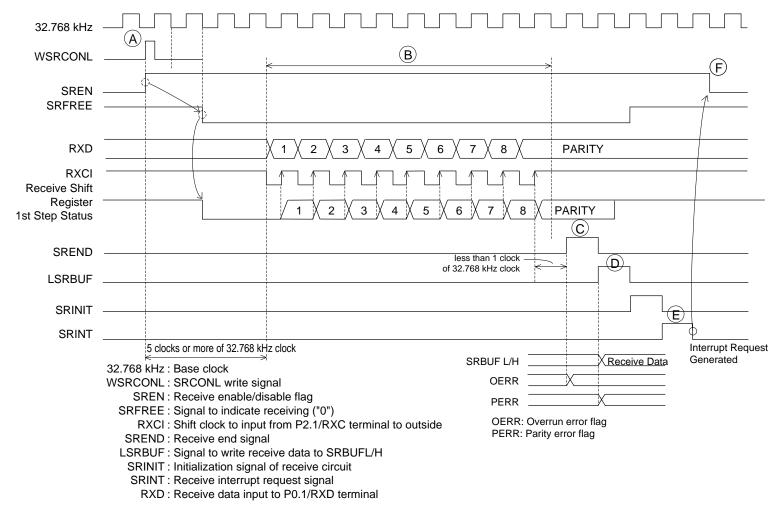

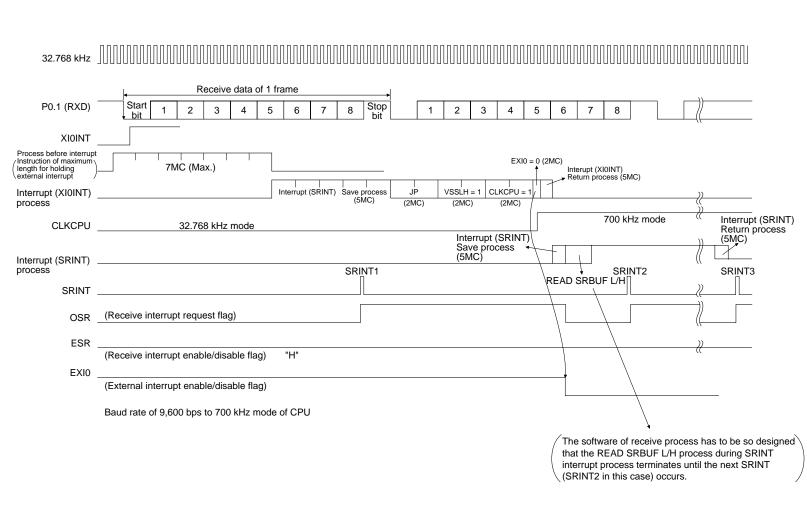

|     | 9.4.3    | Receive Operation                                  | . 9-21 |

| 9.5 | LSB F    | First/MSB First Switching of Transmit/Receive Data | . 9-27 |

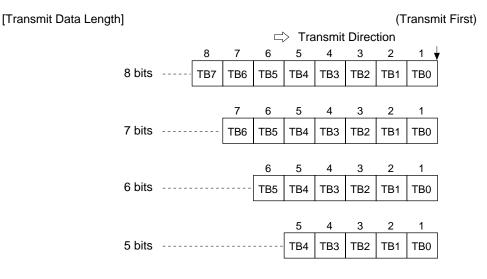

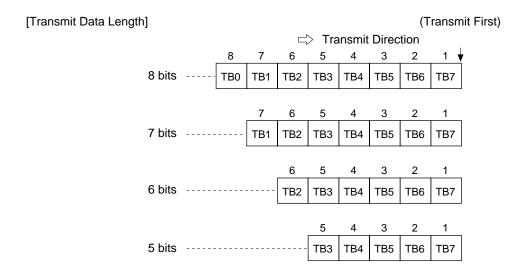

|     | 9.5.1    | LSB First/MSB First Switching of Transmit Data     | . 9-27 |

|     | 9.5.2    | LSB First/MSB First Switching of Receive Data      | . 9-29 |

|     |          |                                                    |        |

#### Chapter 10 Buzzer Driver (BD)

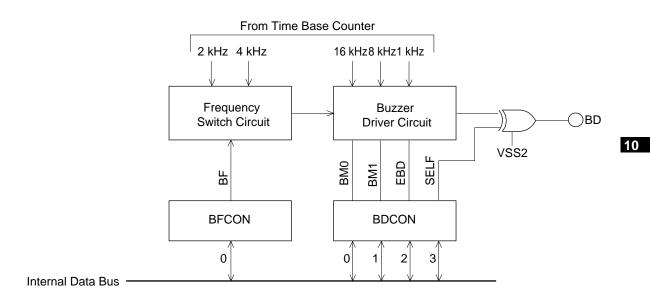

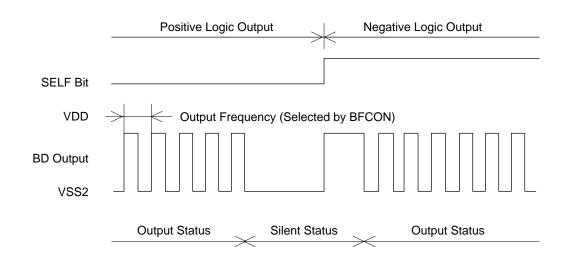

| 10.1 | Overview                                                              | 10-1 |

|------|-----------------------------------------------------------------------|------|

| 10.2 | Configuration of Buzzer Driver                                        | 10-1 |

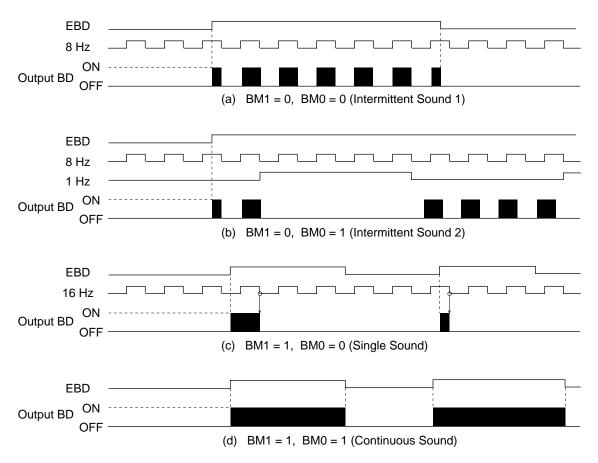

|      | Operation of Buzzer Driver                                            |      |

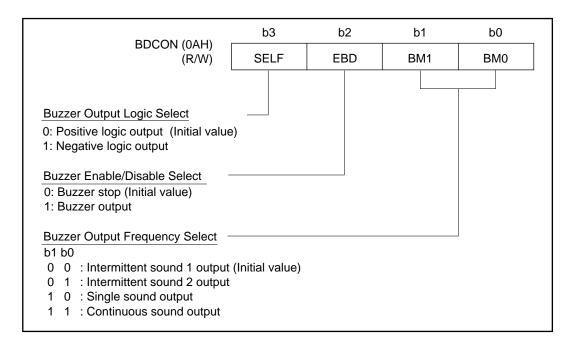

| 10.4 | Buzzer Driver-Related Registers                                       | 10-3 |

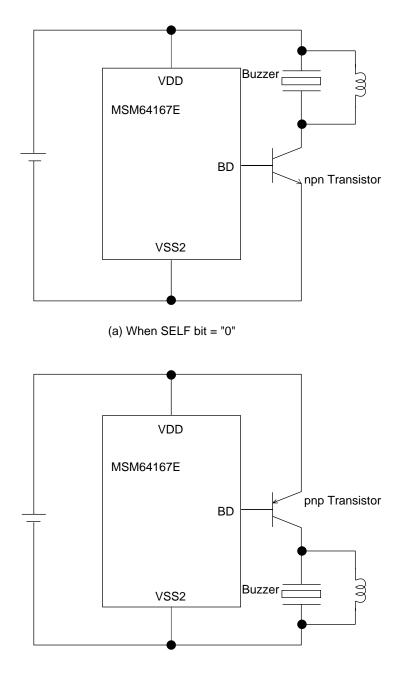

| 10.5 | Difference of Output Logic Depending on SELF Bit and External Circuit | 10-5 |

#### Chapter 11 Watchdog Timer (WDT)

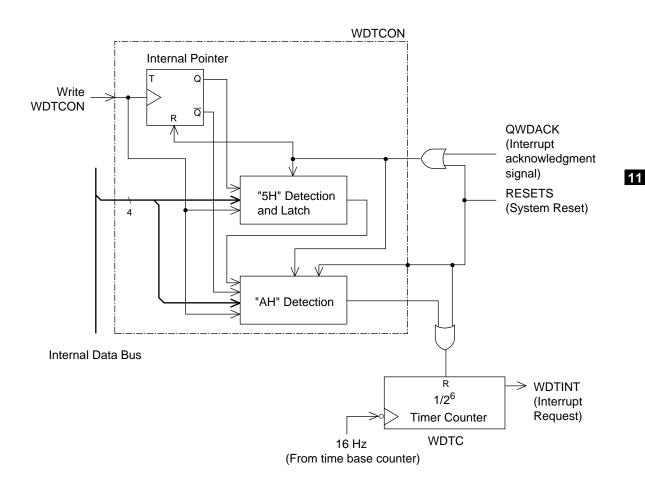

| 11.1 | Overview                                 | 11-1 |

|------|------------------------------------------|------|

| 11.2 | Configuration of Watchdog Timer          | 11-1 |

| 11.3 | Operation of Watchdog Timer              | 11-2 |

| 11.4 | Watchdog Timer Control Register (WDTCON) | 11-3 |

#### Chapter 12 A/D Converter (ADC)

| 12.1 | Overvie                      | w                                    | 12-1  |

|------|------------------------------|--------------------------------------|-------|

| 12.2 | Configu                      | ration of A/D Converter              | 12-1  |

| 12.3 | 3 Operation of A/D Converter |                                      |       |

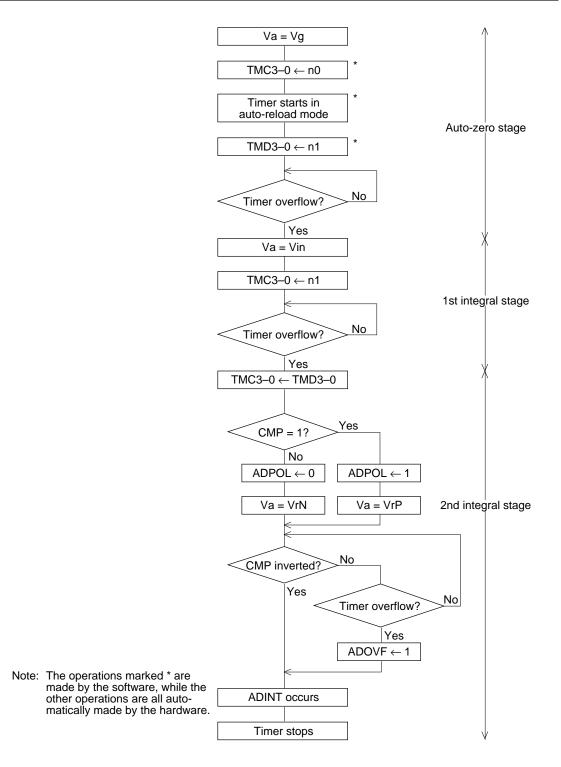

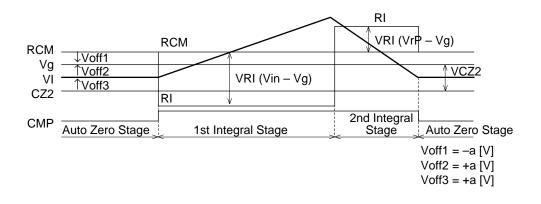

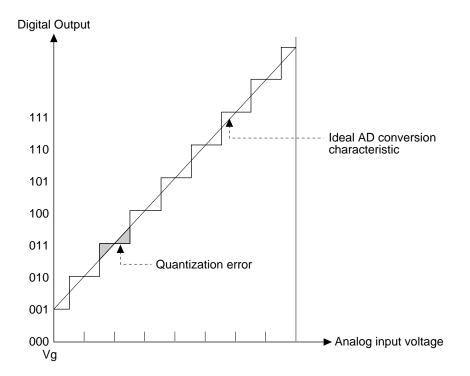

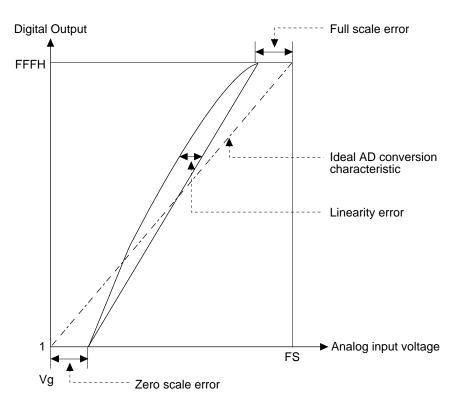

|      | 12.3.1                       | AD Conversion Operation              | 12-2  |

|      | 12.3.2                       | Input Voltage Overflow Flag (ADOVF)  | 12-7  |

|      | 12.3.3                       | Offset Compensation                  | 12-8  |

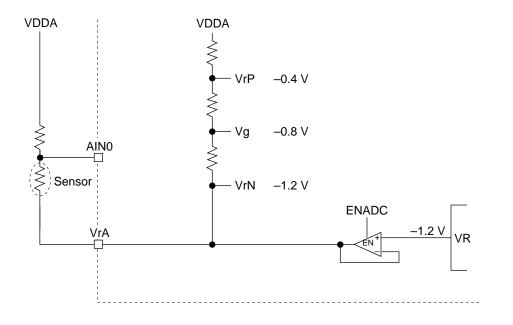

|      | 12.3.4                       | Reference Voltage Generation Circuit | 12-9  |

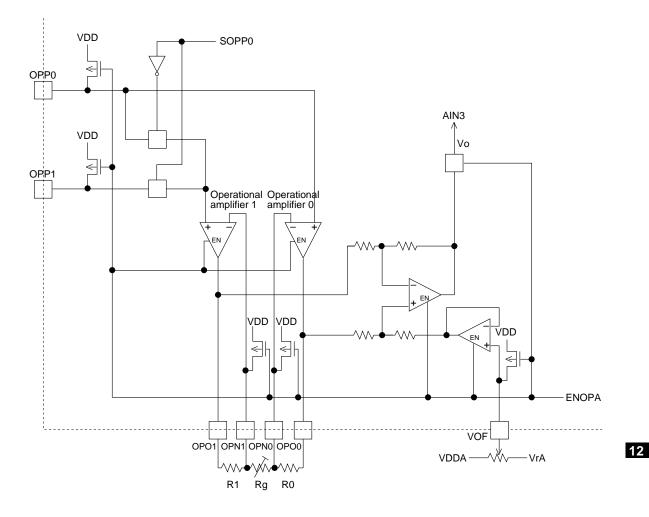

|      | 12.3.5                       | Voltage Amplification Circuit        | 12-10 |

|      | 12.3.6                       | Constant-Current Generation Circuit  | 12-13 |

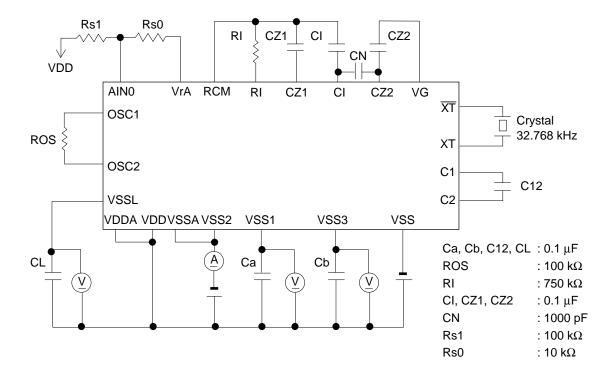

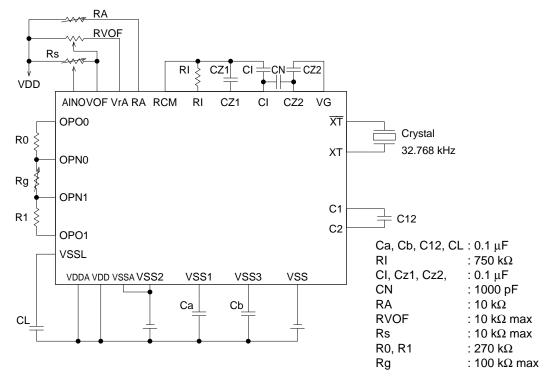

|      | 12.3.7                       | External Components                  | 12-14 |

|      | 12.3.8                       | Precautions in Use of A/D Converter  | 12-15 |

| 12.4 | A/D Cor                      | nverter-Related Registers            | 12-19 |

#### Chapter 13 LCD Driver (LCD)

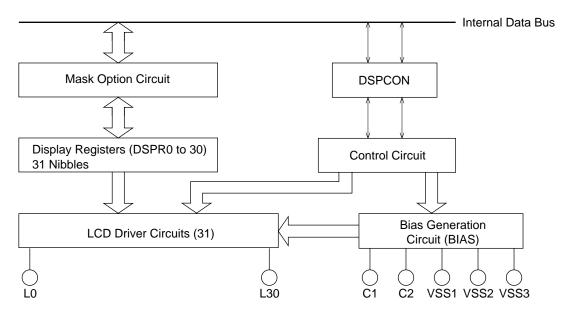

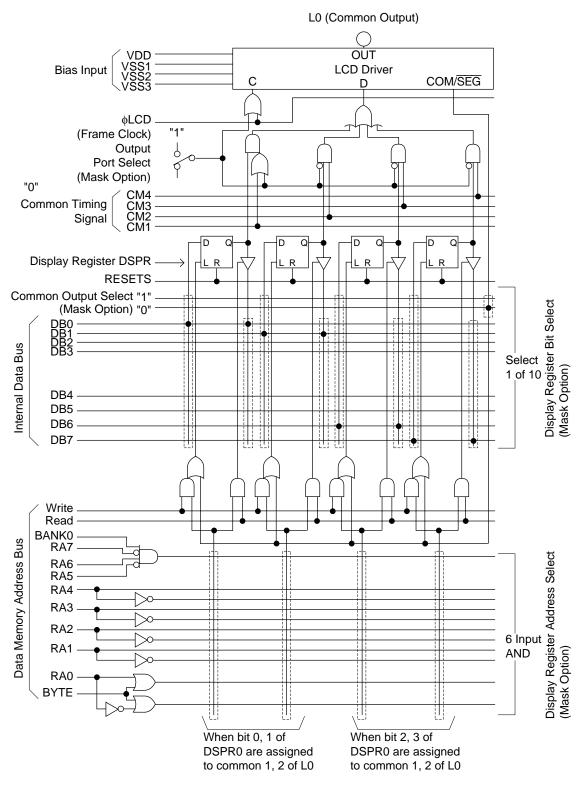

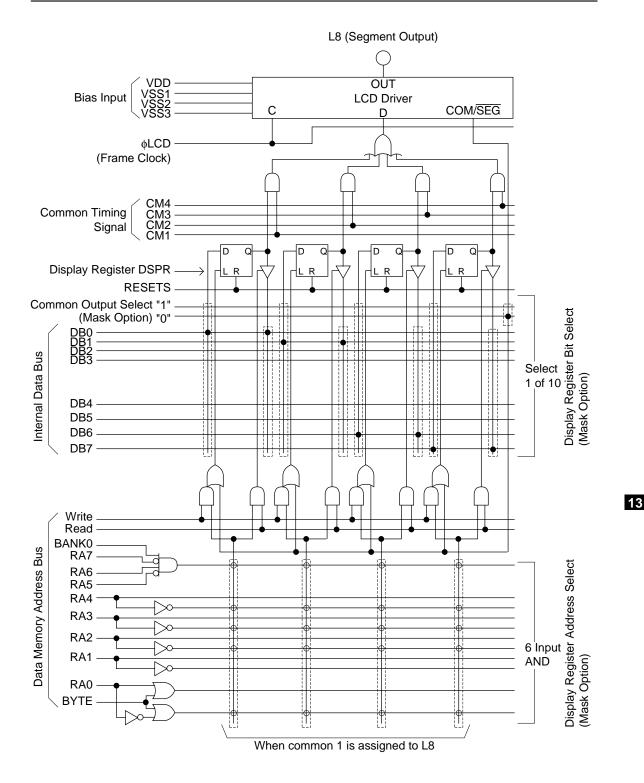

| 13.1 | Overview                               | 13-1 |

|------|----------------------------------------|------|

| 13.2 | Configuration of LCD Driver            | 13-1 |

| 13.3 | Operation of LCD Driver                | 13-4 |

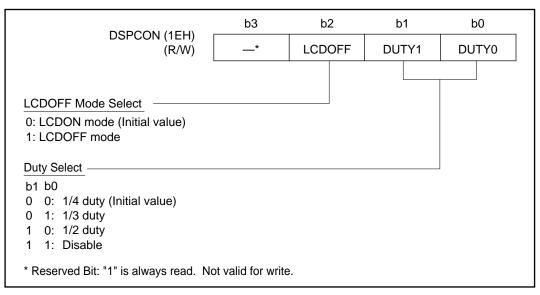

| 13.4 | Display Control Register (DSPCON)      | 13-4 |

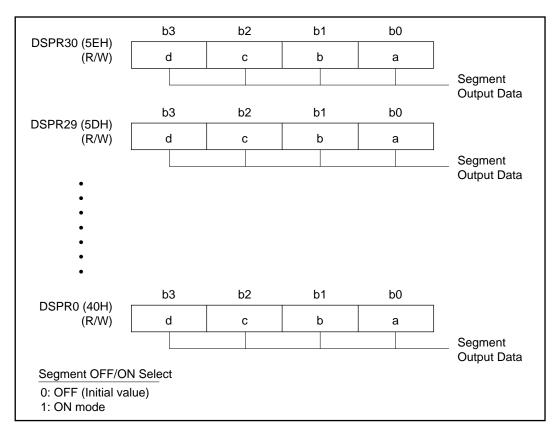

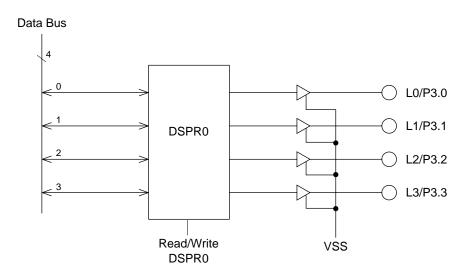

| 13.5 | Display Registers 0-30 (DSPR0-30)      | 13-5 |

| 13.6 | Output Port Selection by Mask Option   | 13-6 |

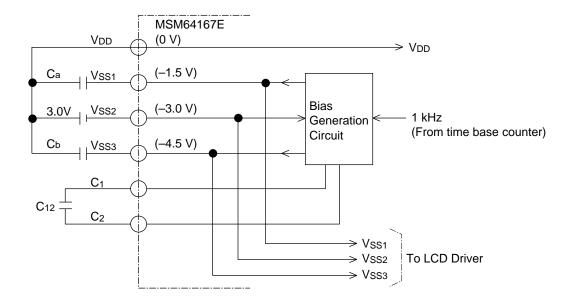

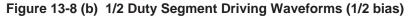

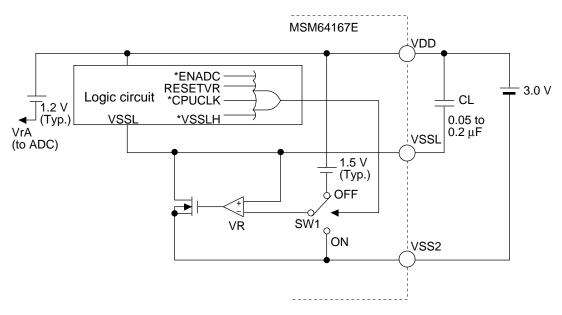

| 13.7 | Bias Generation Circuit for LCD Driver | 13-7 |

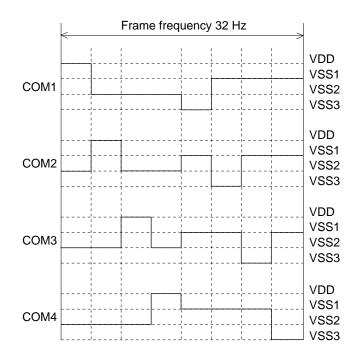

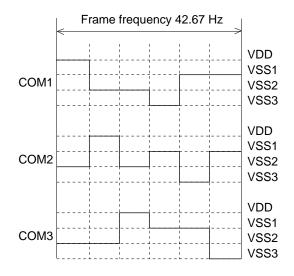

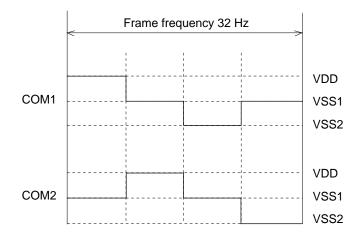

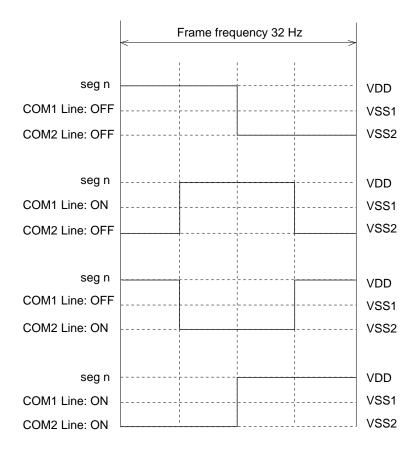

| 13.8 | LCD Driver Output Waveform             | 13-8 |

#### Chapter 14 Constant Voltage Generation Circuit (VR)

| 14.1 | Overview                                             | 14-1 |

|------|------------------------------------------------------|------|

| 14.2 | Configuration of Constant Voltage Generation Circuit | 14-1 |

| 14.3 | Operation of Constant Voltage Generation Circuit     | 14-2 |

| 14.4 | VSSL Control Register (VSSLCON)                      | 14-3 |

#### Chapter 15 Test Circuit (TST)

| 15.1 | Overview                              | 15-1 |

|------|---------------------------------------|------|

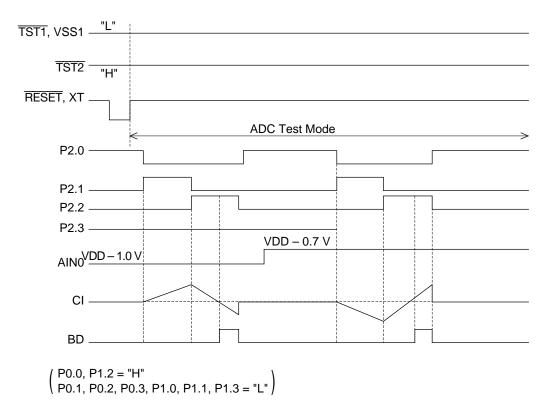

| 15.2 | Operation in ADC Test Mode            | 15-1 |

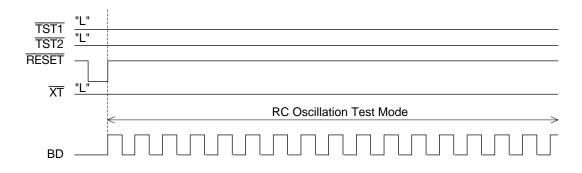

| 15.3 | Operation in RC Oscillation Test Mode | 15-2 |

#### Appendixes

| Appendix A | List of Special Function Registers    | Appendix-1  |

|------------|---------------------------------------|-------------|

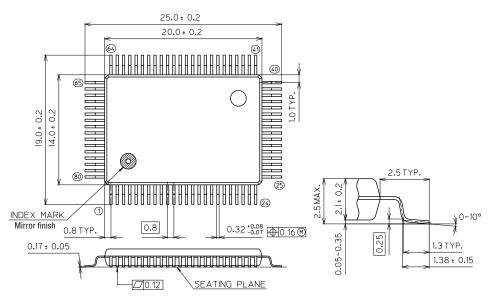

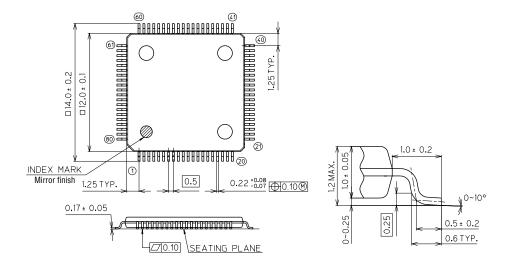

| Appendix B | Package Dimensions                    | Appendix-6  |

| Appendix C | Bonding Pad Coordinates               | Appendix-7  |

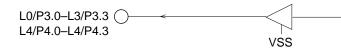

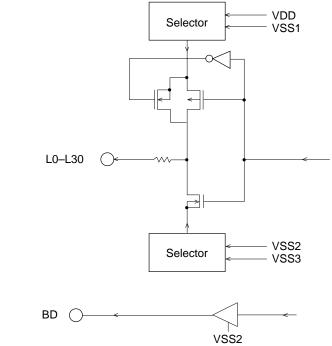

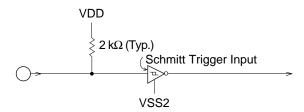

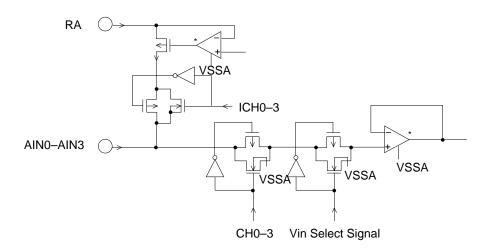

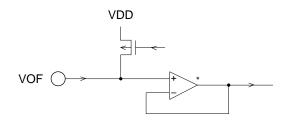

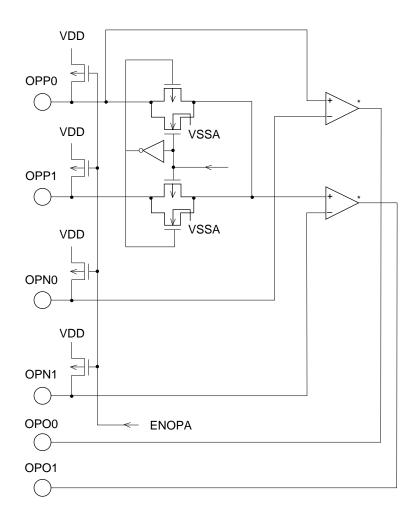

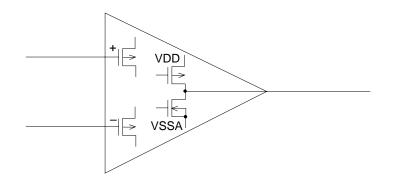

| Appendix D | Configuration of Input/Output Circuit | Appendix-8  |

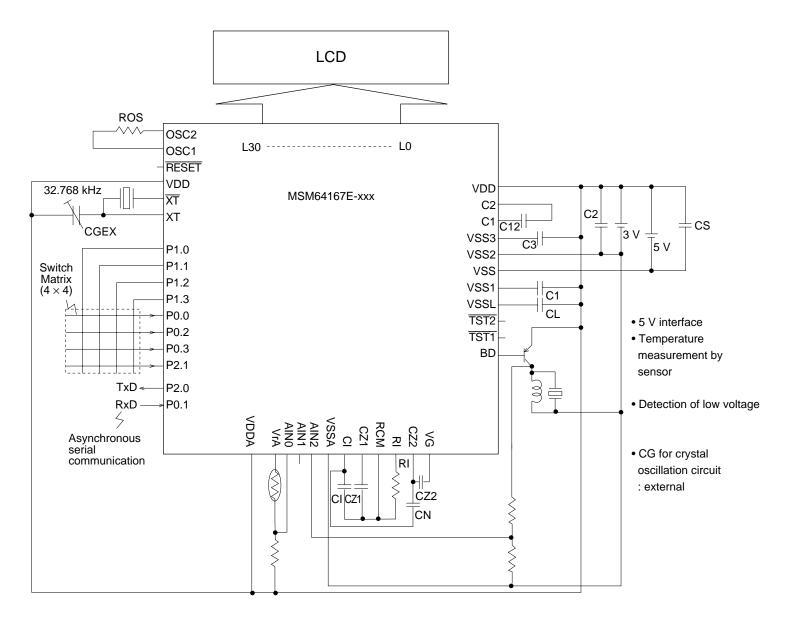

| Appendix E | Example of Applied Circuit            | Appendix-13 |

| Appendix F | Mask Options                          | Appendix-14 |

| Appendix G | Electrical Characteristics            | Appendix-19 |

| Appendix H | Instruction List                      | Appendix-33 |

Contents-6

| Chapter 1  | Overview                                 | 1  |

|------------|------------------------------------------|----|

|            |                                          | 2  |

| Chapter 2  | CPU                                      | 2  |

| Chapter 3  | CPU Control Functions                    | 3  |

| •          |                                          |    |

| Chapter 4  | Interrupt (INTC)                         | 4  |

| Chapter 5  | Clock Generation Circuit (2CLK)          | 5  |

| I          |                                          |    |

| Chapter 6  | Time Base Counter (TBC)                  | 6  |

| Chapter 7  | Ports (P0, P1 and P2)                    | 7  |

|            |                                          |    |

| Chapter 8  | Timer (TM)                               | 8  |

| Chapter 9  | Serial Port (SIOP)                       | 9  |

| Chapter 10 | Buzzer Driver (BD)                       | 10 |

|            |                                          |    |

| Chapter 11 | Watchdog Timer (WDT)                     | 11 |

| Chapter 12 | A/D Converter (ADC)                      | 12 |

| 01 / /0    |                                          | 13 |

| Chapter 13 | LCD Driver (LCD)                         | 13 |

| Chapter 14 | Constant Voltage Generation Circuit (VR) | 14 |

| Chapter 15 | Test Circuit (TST)                       | 15 |

|            |                                          |    |

| Appendixes |                                          |    |

## Chapter 1

Overview

#### **Chapter 1 Overview**

#### 1.1 Overview

The MSM64167E is a CMOS 4-bit one-chip microcontroller that has built-in 256-nibble RAM, 12 I/ O ports, buzzer output, a serial port, a dual slope type A/D converter, a 16-bit timer, and 31 LCD segment drivers.

The CPU uses a high-performance 4-bit CPU core of nX-4/20 with byte processing instructions and is best suited for applications such as thermometers, hygrometers and manometers because of the compact chip layout and ample peripheral functions.

#### 1.2 Features

- (1) Ample instruction set including byte arithmetic instructions

- 148 instructions

- Byte addition/subtraction, byte transfer and byte comparison instructions

- Bit operation instructions

- Data exchange instructions

- (2) Ample addressing modes

- Two kinds of indirect addressing modes using HL registers and XY registers

- Bit operations on entire data memory area

- Byte operations on entire data memory area

- (3) Operating frequencies

- Low speed clock: 32.768 kHz crystal oscillation

- High speed clock: 700 kHz, RC oscillation

- Minimum instruction execution time: 91  $\mu$ s @ 32.768 kHz system clock 4.3  $\mu$ s @ 700 kHz system clock

- (4) Internal program memory: 4064 bytes

- (5) Internal data memory: 256 nibbles

- (6) I/O ports: 12

- 4-bit input/output port (NMOS open drain output/CMOS output selectable, input with pull-down/pull-up resistance or high-impedance input selectable) ×3

- (7) Buzzer output: 1

- 4 output modes selectable

- (8) Serial port: 1

- Synchronous mode / asynchronous mode support

- Synchronous mode: 32.768 kHz/external clock

- Asynchronous mode: 9600 bps / 4800 bps / 2400 bps / 1200 bps

- (9) LCD driver: 31

- At 1/4 duty and 1/3 bias: 108 segments ( $27 \times 4$ )

- At 1/3 duty and 1/3 bias: 84 segments ( $28 \times 3$ )

- At 1/2 duty and 1/2 bias: 58 segments  $(29 \times 2)$

- Output port selectable by mask option for 8 drivers

- (10) Dual slope type A/D converter: 1

- Analog input: 4 channels

- Reference voltage internal generation

- Voice amplification circuit

- (11) Timer: 16-bit × 1

- Auto reload mode

- Capture mode

- Clock frequency measurement mode

- (12) Watchdog timer

- (13) Interrupt factors: 10

- 2 external factors, 3 time base factors, 1 timer factor, 2 serial port factors, 1 A/D converter factor and 1 watchdog timer factor

- (14) Power supply voltage

- 2.6 V to 3.6 V

- Low current consumption

- (15) Exterior

- Chip

- 80-pin flat package GA: QFP (QFP80-P-1420-0.80-BK) TB: TQFP (TQFP80-P-1212-0.50-K)

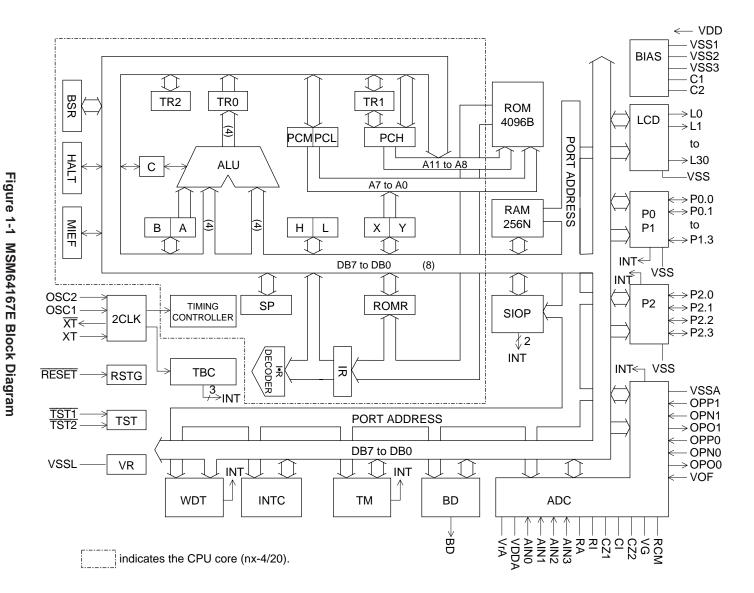

# 1.3 Block Diagram

Figure 1-1 shows the block diagram of the MSM64167E.

\_\_\_\_\_ မ

#### 1.4 Pin Configuration

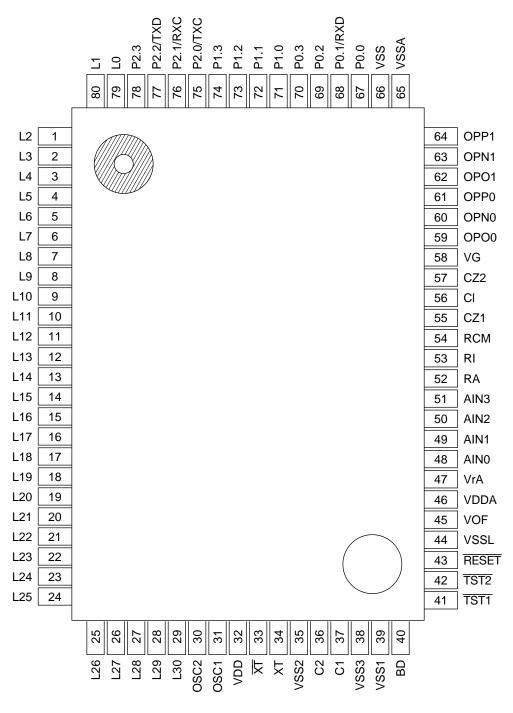

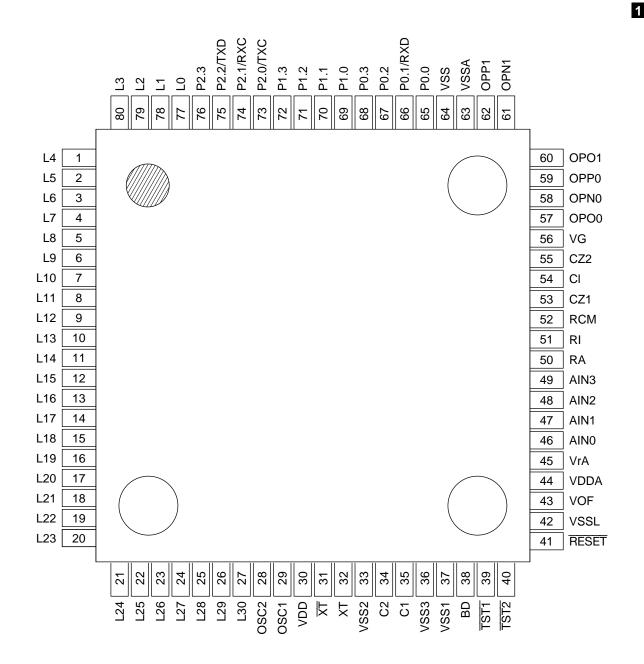

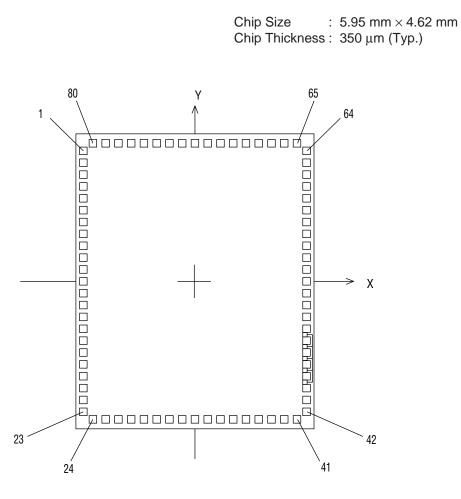

Figures 1-2 and 1-3 show the MSM64167E package pin configurations and Figure 1-4 is the top view of the chip.

Figure 1-2 MSM64167E-GA (QFP) Pin Configuration

Figure 1-3 MSM64167E-TB (TQFP) Pin Configuration

Note: The chip substrate voltage is  $V_{DD}$ .

Figure 1-4 MSM64167E Chip External View

#### 1.5 Description of Pins

#### 1.5.1 Description of Each Pin

Table 1-1 lists the MSM64167E pin basic functions and Table 1-2 the pin secondary functions.

|                | Pin Name | Pin | No. |         |     | Function                                          |

|----------------|----------|-----|-----|---------|-----|---------------------------------------------------|

| Classification |          | GA  | ΤВ  | Pad No. | I/O | Function                                          |

|                | VDD      | 32  | 30  | 32      | _   | 0 V power supply.                                 |

|                | VSS1     | 39  | 37  | 39      | _   | Bias output for driving LCD (-1.5 V).             |

|                | VSS2     | 35  | 33  | 35      | _   | Negative side power supply.                       |

|                |          |     |     |         |     | Bias output for driving LCD (-3.0 V).             |

|                | VSS3     | 38  | 36  | 38      | _   | Bias output for driving LCD (-4.5 V).             |

|                | VSS      | 66  | 64  | 66      | _   | Negative side power supply for input/output       |

|                |          |     |     |         |     | port interface.                                   |

| Power Supply   | C1       | 37  | 35  | 37      | _   | Capacitor connection for LCD driving bias         |

|                | C2       | 36  | 34  | 36      | —   | generation.                                       |

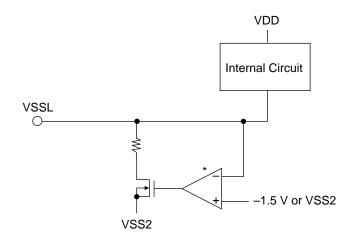

|                | VSSL     | 44  | 42  | 44      | —   | Negative side power supply pin for internal logic |

|                |          |     |     |         |     | (internally generated constant voltage).          |

|                | VSSA     | 65  | 63  | 65      | —   | Externally connects to VSS2 negative side power   |

|                |          |     |     |         |     | supply for A/D converter.                         |

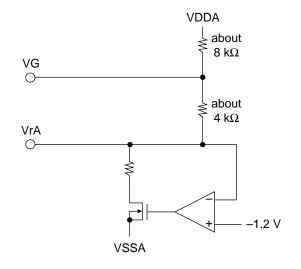

|                | VDDA     | 46  | 44  | 46      | —   | Externally connects to VDD.                       |

|                |          |     |     |         |     | 0 V power supply for A/D converter.               |

|                | ХТ       | 34  | 32  | 34      | Ι   | Low speed side clock oscillation input pin:       |

| Oscillation    | XT       | 33  | 31  | 33      | 0   | Connects to the crystal (32.768 kHz).             |

| Oscillation    | OSC1     | 31  | 29  | 31      | Ι   | High speed side clock pin:                        |

|                | OSC2     | 30  | 28  | 30      | 0   | Connects to the resistance for oscillation.       |

| Test           | TST1     | 41  | 39  | 41      | Ι   | Input pin for test:                               |

| Test           | TST2     | 42  | 40  | 42      | Ι   | Pulled-up to VDD internally.                      |

|                | RESET    | 43  | 41  | 43      | I   | System reset input:                               |

|                |          |     |     |         |     | When this pin becomes "H" level from "L" level,   |

| Reset          |          |     |     |         |     | the internal state is initialized and execution   |

|                |          |     |     |         |     | of an instruction starts from address 000H.       |

|                |          |     |     |         |     | Pulled-up to VDD internally.                      |

|                |          | Pin | No |         |     |                                                       |

|----------------|----------|-----|----|---------|-----|-------------------------------------------------------|

| Classification | Pin Name | GA  |    | Pad No. | I/O | Function                                              |

|                | P0.0     | 67  | 65 | 67      | I/O | 4-bit I/O Port (P0):                                  |

|                | P0.1     | 68  | 66 | 68      | I/O | 4-bit I/O port that can select I/O, pull-up/pull-down |

|                | P0.2     | 69  | 67 | 69      | I/O | resistance input/high impedance input, and NMOS       |

|                | P0.3     | 70  | 68 | 70      | I/O | open drain output/CMOS output for each bit by         |

|                |          |     |    |         |     | port 0 control registers 0-3 (P00CON-P03CON).         |

|                |          |     |    |         |     | External interrupt function is assigned to each pin.  |

|                | P1.0     | 71  | 69 | 71      | I/O | 4-bit I/O Port (P1):                                  |

|                | P1.1     | 72  | 70 | 72      | I/O | 4-bit I/O port that can select I/O, pull-up/pull-down |

| Port           | P1.2     | 73  | 71 | 73      | I/O | resistance input/high impedance input, and NMOS       |

|                | P1.3     | 74  | 72 | 74      | I/O | open drain output/CMOS output for each bit by         |

|                |          |     |    |         |     | port 1 control registers 0–3 (P10CON–P13CON).         |

|                |          |     |    |         |     | External interrupt function is assigned to each pin.  |

|                | P2.0     | 75  | 73 | 75      | I/O | 4-bit I/O Port (P2):                                  |

|                | P2.1     | 76  | 74 | 76      | I/O | 4-bit I/O port that can select I/O, pull-up/pull-down |

|                | P2.2     | 77  | 75 | 77      | I/O | resistance input/high impedance input, and NMOS       |

|                | P2.3     | 78  | 76 | 78      | I/O | open drain output/ CMOS output for each bit by        |

|                |          |     |    |         |     | port 2 control registers 0–3 (P20CON–P23CON).         |

|                |          |     |    |         |     | External interrupt function is assigned to each pin.  |

| Buzzer         | BD       | 40  | 38 | 40      | 0   | Output pin of buzzer driver.                          |

|                | AIN0     | 48  | 46 | 48      | I   | Analog voltage input pin. Can be selected             |

|                | AIN1     | 49  | 47 | 49      | I   | to constant current for each pin by AD                |

|                | AIN2     | 50  | 48 | 50      | I   | control register 0 (ADCON0).                          |

|                | AIN3     | 51  | 49 | 51      | I   |                                                       |

|                | RA       | 52  | 50 | 52      |     | Resistance connection pin for current adjustment.     |

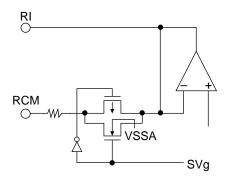

|                | RI       | 53  | 51 | 53      | _   | Resistance connection pin for integral.               |

|                | RCM      | 54  | 52 | 54      | —   | Common connection pin of resistance for integral,     |

|                |          |     |    |         |     | capacitor 1 for offset compensation, and capacitor    |

|                |          |     |    |         |     | integral.                                             |

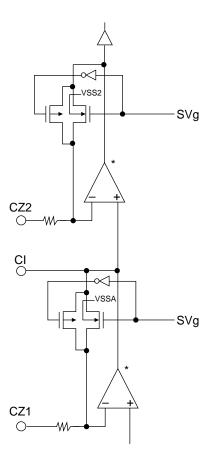

|                | CZ1      | 55  | 53 | 55      | —   | Connection pin of capacitor 1 for offset              |

| A/D            |          |     |    |         |     | compensation.                                         |

| Converter      | CI       | 56  | 54 | 56      | —   | Connection pin of capacitor for integral.             |

|                | CZ2      | 57  | 55 | 57      | —   | Connection pin of capacitor 2 for offset              |

|                | VG       | 58  | 56 | 58      | —   | compensation.                                         |

|                | VOF      | 45  | 43 | 45      | Ι   | Connection pin of resistance for voltage              |

|                |          |     |    |         |     | amplification circuit offset adjustment.              |

|                | OPP0     | 61  | 59 | 61      | I   | Analog micro-voltage input pin.                       |

|                | OPP1     | 64  | 62 | 64      | Ι   |                                                       |

|                | OPN0     | 60  | 58 | 60      |     | Connection pin of resistance for voltage              |

|                | OPN1     | 63  | 61 | 63      | Ι   | amplification rate adjustment.                        |

|                | OPO0     | 59  | 57 | 59      | 0   |                                                       |

|                | OPO1     | 62  | 60 | 62      | 0   |                                                       |

|                | VrA      | 47  | 45 | 47      | —   | Standard voltage for A/D converter                    |

|                |          |     |    |         |     | (internally generated constant voltage).              |

| Table 1-1 (b) | Pin Descriptions | (Basic Functions) |

|---------------|------------------|-------------------|

|---------------|------------------|-------------------|

| <b>a</b>       | Pin No.  |    | No. |         |     |                                            |

|----------------|----------|----|-----|---------|-----|--------------------------------------------|

| Classification | Pin Name |    | ΤВ  | Pad No. | I/O | Function                                   |

| LCD Driver     | LO       | 79 | 77  | 79      | 0   | LCD segment and common signal output pins. |

|                | L1       | 80 | 78  | 80      | 0   | Becomes output port by mask option.        |

|                | L2       | 1  | 79  | 1       | 0   |                                            |

|                | L3       | 2  | 80  | 2       | 0   |                                            |

|                | L4       | 3  | 1   | 3       | 0   |                                            |

|                | L5       | 4  | 2   | 4       | 0   |                                            |

|                | L6       | 5  | 3   | 5       | 0   |                                            |

|                | L7       | 6  | 4   | 6       | 0   |                                            |

|                | L8       | 7  | 5   | 7       | 0   | LCD segment and common signal output pins. |

|                | L9       | 8  | 6   | 8       | 0   |                                            |

|                | L10      | 9  | 7   | 9       | 0   |                                            |

|                | L11      | 10 | 8   | 10      | 0   |                                            |

|                | L12      | 11 | 9   | 11      | 0   |                                            |

|                | L13      | 12 | 10  | 12      | 0   |                                            |

|                | L14      | 13 | 11  | 13      | 0   |                                            |

|                | L15      | 14 | 12  | 14      | 0   |                                            |

|                | L16      | 15 | 13  | 15      | 0   |                                            |

|                | L17      | 16 | 14  | 16      | 0   |                                            |

|                | L18      | 17 | 15  | 17      | 0   |                                            |

|                | L19      | 18 | 16  | 18      | 0   |                                            |

|                | L20      | 19 | 17  | 19      | 0   |                                            |

|                | L21      | 20 | 18  | 20      | 0   |                                            |

|                | L22      | 21 | 19  | 21      | 0   |                                            |

|                | L23      | 22 | 20  | 22      | 0   |                                            |

|                | L24      | 23 | 21  | 23      | 0   |                                            |

|                | L25      | 24 | 22  | 24      | 0   |                                            |

|                | L26      | 25 | 23  | 25      | 0   |                                            |

|                | L27      | 26 | 24  | 26      | 0   |                                            |

|                | L28      | 27 | 25  | 27      | 0   |                                            |

|                | L29      | 28 | 26  | 28      | 0   |                                            |

|                | L30      | 29 | 27  | 29      | 0   |                                            |

#### Table 1-1 (c) Description of Pins (Basic Functions)

|                | D: 11    | Pin | No. | <b>_</b> | I/O | Function                                               |

|----------------|----------|-----|-----|----------|-----|--------------------------------------------------------|

| Classification | Pin Name | GA  | ΤВ  | Pad No.  |     |                                                        |

|                | P0.0     | 67  | 65  | 67       | Ι   | External interrupt input pins.                         |

|                | P0.1     | 68  | 66  | 68       |     | Interrupt is enabled by level change.                  |

|                | P0.2     | 69  | 67  | 69       |     |                                                        |

|                | P0.3     | 70  | 68  | 70       |     |                                                        |

| External       | P1.0     | 71  | 69  | 71       |     |                                                        |

| Interrupt      | P1.1     | 72  | 70  | 72       |     |                                                        |

|                | P1.2     | 73  | 71  | 73       |     |                                                        |

|                | P1.3     | 74  | 72  | 74       |     |                                                        |

|                | P2.0     | 75  | 73  | 75       |     |                                                        |

|                | P2.1     | 76  | 74  | 76       |     |                                                        |

|                | P2.2     | 77  | 75  | 77       |     |                                                        |

|                | P2.3     | 78  | 76  | 78       |     |                                                        |

|                | P0.1     | 68  | 66  | 68       | Ι   | Becomes receive data input pin (RXD) of serial port.   |

|                | P2.0     | 75  | 73  | 75       | I/O | Becomes transmit clock I/O pin (TXC) of serial port.   |

| Serial Port    |          |     |     |          |     |                                                        |

|                | P2.1     | 76  | 74  | 76       | I/O | Becomes receive clock output pin (RXC) of serial port. |

|                |          |     |     |          |     |                                                        |

|                | P2.2     | 77  | 75  | 77       | 0   | Becomes transmit data output pin (TXD) of serial port. |

|                | P0.0     | 67  | 65  | 67       | Ι   | Becomes capture trigger input pin of timer.            |

| Timer          | P0.2     | 69  | 67  | 69       | Ι   | Becomes external clock input pin (TMC) of timer.       |

|                | P2.3     | 78  | 76  | 78       | 0   | Becomes timer overflow flag output pin (TMO) of timer. |

#### Table 1-2 Description of Pins (Secondary Functions)

#### 1.5.2 Connections of Unused Pins

Table 1-3 shows unused pin connections.

| Pin          |                     | Recommended Pin Connection                                     |

|--------------|---------------------|----------------------------------------------------------------|

| OSC1         | Open                |                                                                |

| OSC2         | Open                |                                                                |

| TST1, TST2   | Open                |                                                                |

| RESET        | Open                |                                                                |

| P0.0 to P0.3 | When set to input:  | "L" level, "H" level or open (depends on input mode selection) |

|              | When set to output: | Open.                                                          |

| P1.0 to P1.3 | When set to input:  | "L" level, "H" level or open (depends on input mode selection) |

|              | When set to output: | Open.                                                          |

| P2.0 to P2.3 | When set to input:  | "L" level, "H" level or open (depends on input mode selection) |

|              | When set to output: | Open.                                                          |

| AIN0 to AIN3 | Open                |                                                                |

| VrA          | Open                |                                                                |

| VOF          | Open                |                                                                |

| RA           | Open                |                                                                |

| RI           | Open                |                                                                |

| RCM          | Open                |                                                                |

| CZ1, CZ2     | Open                |                                                                |

| VG           | Open                |                                                                |

| OPP0, OPP1   | Open                |                                                                |

| OPN0, OPN1   | Open                |                                                                |

| OPO0, OPO1   | Open                |                                                                |

| L0 to L30    | Open                |                                                                |

| BD           | Open                |                                                                |

#### Table 1-3 Connections of Unused Pins

#### 1.6 Basic Timing

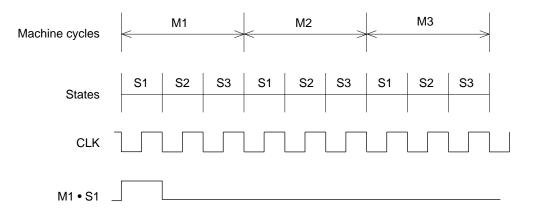

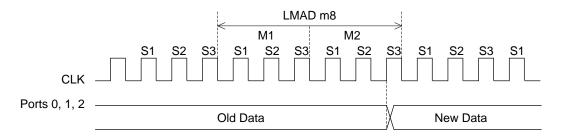

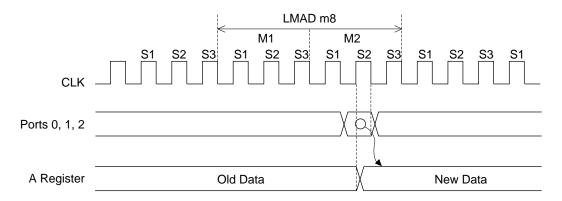

The MSM64167E generates a system clock (CLK) without dividing the 32.768 kHz oscillation clocks by XT and  $(\overline{XT})$  pins or 700 kHz RC oscillation clocks by OSC1 and OSC2 pins. A CLK signal phase matches the  $(\overline{XT})$  pin of OSC1 pin phase.

Each instruction is processed with a machine cycle unit, and executed between one machine cycle (minimum) and five machine cycles (maximum).

One machine cycle includes three intervals of S1–S3 states. "State" is defined as an interval from the fall edge of the system clock (CLK) to the next fall. The S1 state of the first machine cycle (M1) of an instruction is M1  $\cdot$  S1.

Figure 1-5 shows an example of the relationship among the system clock, states, and machine cycles.

Figure 1-5 Definition of Machine Cycle

# Chapter 2

#### Chapter 2 CPU

#### 2.1 Overview

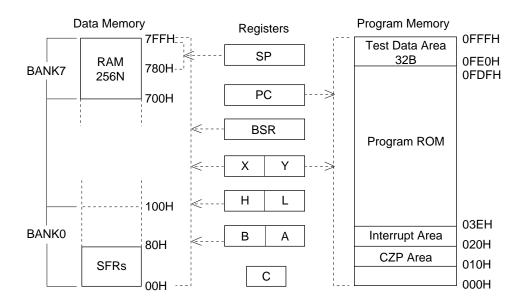

The instruction set of the MSM64167E is composed of 148 types of instructions that contain byte operations. The address space of the MSM64167E is divided into an 8-bit wide program memory area and a 4-bit wide data memory area.

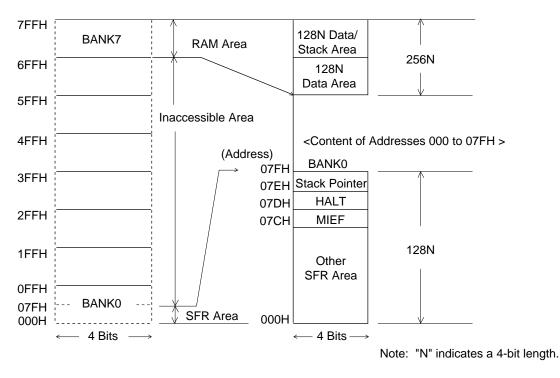

A program data area and a 32-byte test data area are assigned to the program memory area. The data memory area has a 256-nibble RAM assigned to Bank 7, and the special function registers (SFRs) are assigned to Bank 0.

Stacks for subroutines and interrupts are assigned to 128 nibbles from address 7FFH to address 780H in Bank 7 by the stack pointer. Figure 2-1 shows each register and memory space.

Figure 2-1 Registers and Memory Space

#### Notes:

- (1) Banks in data memory are specified by the bank select register (BSR). In other words, they are specified by the contents of the bank select registers (BSR0 and BSR1) and the state of the bank control flags (BCF and BEF).

- (2) The 32 bytes of 0FE0H–0FFFH of program memory are for the test data area and cannot be used as a program data area.

#### 2.2 Configuration of Registers

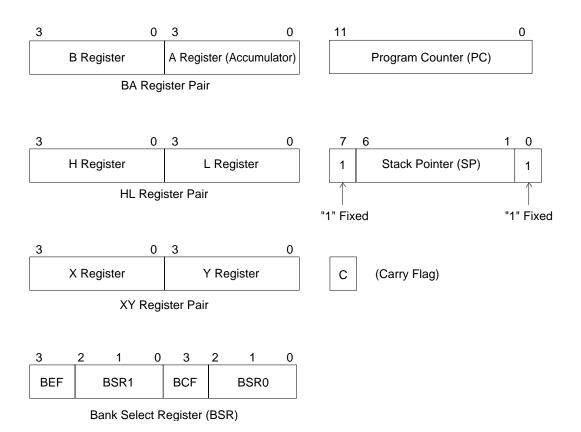

Figure 2-2 shows the configuration of registers of MSM64167E.

#### Figure 2-2 Configuration of MSM64167E Registers

#### 2.2.1 Registers A, B, H, L, X and Y

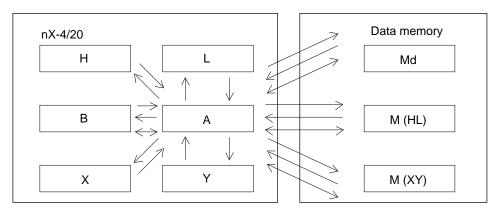

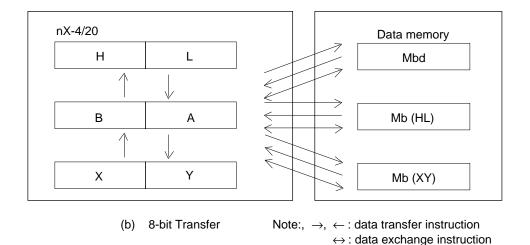

The A register (accumulator) is a central register of each operation processing. B, H, L, X and Y are working registers. B and A register pairs play a central role in processing byte data. H and L register pairs and X and Y register pairs are used for the indirect addressing of data memory and for the working registers of byte processing. Figure 2-3 shows the possible combination of data transfers between each register and data memory.

(a) 4-bit Transfer

Figure 2-3 Combination of Data Transfers between Registers

In Figure 2-3, "M" indicates data memory, "d" indicates direct addressing mode specification, "(HL)" and "(XY)" indicate indirect addressing mode specification, and "b" indicates byte data. Arrows indicate the direction of data transfer.

When an interrupt occurs, BA and HL register pairs are automatically saved to a stack.

#### 2.2.2 Program Counter (PC)

The program counter has 12 valid bits and can select a program memory area of 4K bytes.

#### 2.2.3 Stack Pointer (SP)

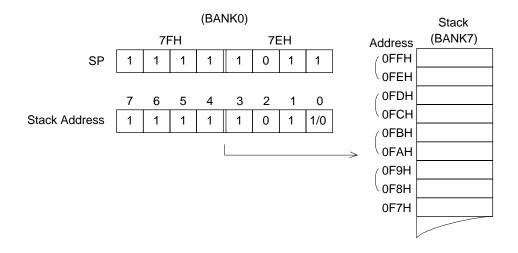

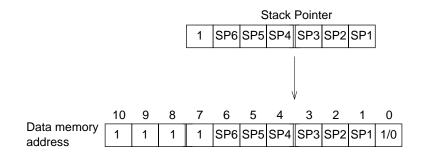

The stack pointer (SP) is a register used to indicate the first address of a stack, and is assigned from 7EH–7FH of data memory bank 0.

The least significant bit and most significant bit of SP is fixed to "1". The remaining 6 bits function as an up/down counter for byte processing, which is decremented when data is saved to the stack and incremented when returned from the stack.

At system reset, SP becomes "0FFH" and the stack addresses become 0FFH and 0FEH in Bank 7.

Use a byte processing instruction when modifying or reading out the contents of SP. The content of SP cannot be read/written by a 4-bit processing instruction.

Bits 0 and 7 of SP are ignored if data write instructions are used, and is always "1" if a data read instruction is used.

#### 2.2.4 Carry Flag (C)

A carry flag is a one-bit flag. A carry is loaded for an addition instruction, and a borrow is loaded for a subtraction instruction. When an interrupt occurs, a carry flag is automatically saved to a stack.

#### 2.3 Memory Space

#### 2.3.1 Program Memory

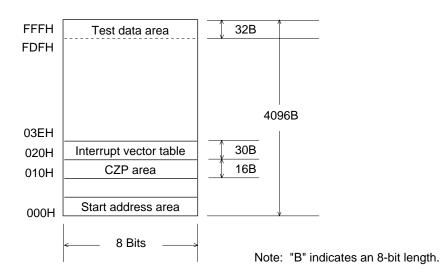

Program memory is a memory area for program data, interrupt area, the CZP area, the start address area and the test data area.

Data length is 8 bits with addresses 0-4095 assigned.

Figure 2-5 Program Memory Address Space

The address space of program memory is shown in Figure 2-5.

Address 0H is the instruction execution start address at system reset. CZP area from addresses 10H–1FH is the subroutine start address area for a 1-byte call instruction CZP. A maximum of 8 instructions can be assigned. The interrupt area is assigned from addresses 020H–03DH. Test data area is 32 bytes from addresses 0FE0H–0FFFH, and cannot be used as a program memory area.

For details on interrupts, refer to Chapter 4 "Interrupt" and related chapters for peripheral functions.

#### 2.3.2 Data Memory

#### 2.3.2.1 Data Memory Area

RAM and special function registers (SFRs) are assigned to data memory. Data memory is assigned to a different address than program memory. The data length is 4 bits (1 nibble). 256 nibbles is 1 bank unit. Data memory consists of two banks: one for the SFR area that uses part of Bank 0; and a RAM area that includes stacks of Bank 7.

Figure 2-6 Data Memory Address Space

Figure 2-6 shows the address space of data memory. The "stack area" is a data save area used for subroutines and interrupts, and is effective from the highest address of data memory address 7FFH, to a maximum 128N in the lower address direction.

Special function registers (SFRs) are assigned in the low order address direction from address 07FH of BANK 0. For addressing mode of the data memory space, the upper 3 bits of the 11 bits of the data memory address are determined by bank specification. The lower 8 bits are determined by either HL indirect addressing mode, XY indirect addressing mode or direct addressing mode.

However, addresses 0H–7FH of BANK 0 is a special area. If this area is specified by direct addressing mode when the bank common flag (BCF) is 1, Bank 0 is always selected. Bank specification is ignored only in this case.

#### 2.3.2.2 Bank Specification of Data Memory

Banks of data memory are specified by dedicated bank select registers (BSR0 and BSR1), the bank common flag (BCF) and by the bank enable flag (BEF). These registers and flags can be saved and resorted to the stack at the same time by the "PUSH BSR" and "POP BSR" instructions.

There are four modes to address internal banks of data memory: HL indirect addressing mode, XY indirect addressing mode, direct addressing mode and the stack indirect addressing mode. The bank specification method differs depending on the mode.

Table 2-1 shows the BCF and BEF function table. As shown in this table, the bank specification method is determined by BCF, BEF and addressing mode. "BSR0" and "BSR1" in the table indicate that a bank is specified by BSR0 and BSR1. In direct addressing mode, Bank 0 is always specified only when BCF = 1 and the addresses are specified as 0-7FH.

Table 2-2 shows the correspondence between the contents of BSR0 and BSR1 and the bank number.

| BCF | BEF | HL indirect addressing | XY indirect addressing | Direct addressing             | SP indirect addressing |  |

|-----|-----|------------------------|------------------------|-------------------------------|------------------------|--|

| 0   | 0   | BSR0                   | BSR0                   | BSR0                          | <bank7></bank7>        |  |

| 0   | 1   | BSR0                   | BSR1                   | BSR1                          |                        |  |

| 1   | 0   | BSR0                   | BSR0                   | When internal bank addresses  |                        |  |

|     |     |                        |                        | are 0 to 7FH: <bank0></bank0> |                        |  |

|     |     |                        |                        | When internal bank addresses  |                        |  |

|     |     |                        |                        | are 80 to FFH:BSR0            | e 80 to FFH:BSR0       |  |

| 1   | 1   | BSR0                   | BSR1                   | When internal bank addresses  |                        |  |

|     |     |                        |                        | are 0 to 7FH: <bank0></bank0> |                        |  |

|     |     |                        |                        | When internal bank addresses  |                        |  |

|     |     |                        |                        | are 80 to FFH:BSR1            |                        |  |

#### Table 2-1 Relationship between BCF, BEF and Bank Specification by Addressing Mode

#### Table 2-2 Correspondance between Contents of BSR0, BSR1 and Bank Number

| BSR0, BSR1 | Bank number | BSR0, BSR1 | Bank number |

|------------|-------------|------------|-------------|

| 0          | BANK0       | 4          | BANK0       |

| 1          | BANK7       | 5          | BANK7       |

| 2          | BANK0       | 6          | BANK0       |

| 3          | BANK7       | 7          | BANK7       |

#### 2.3.2.3 Addressing Modes of Data Memory

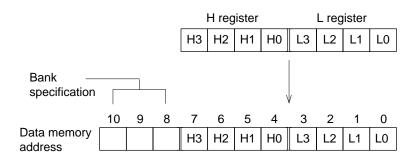

(1) HL indirect addressing mode

Internal bank addresses can be specified by an HL register pair.

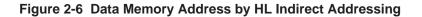

(2) XY indirect addressing mode

Internal bank addresses can be specified by an XY register pair.

Figure 2-7 Data Memory Address by XY Indirect Addressing

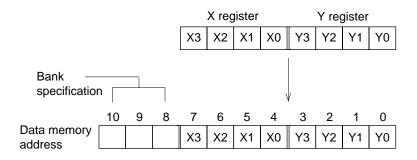

#### (3) Direct addressing mode

Internal bank addresses can be directly specified by 8-bit immediate data included in the instruction code.

#### Figure 2-8 Data Memory Address by Direct Addressing

(4) Stack pointer indirect addressing mode

Addresses in Bank 7 can be specified by stack pointer (SP). This mode is used for stack operation in "PUSH" and "POP" instructions, subroutine jumps, return instructions and interrupts.

Since data is always handled as 8 bits in this mode, bit 0 of this address is invalid. Although SP is 8 bits, the most significant bit and the least significant bit are fixed to "1". The remaining 6 bits function as an up/down counter.

#### Figure 2-9 Data Memory Address by Stack Pointer Indirect Addressing

## **Chapter 3**

3

# **CPU Control Functions**

### **Chapter 3 CPU Control Functions**

#### 3.1 Overview

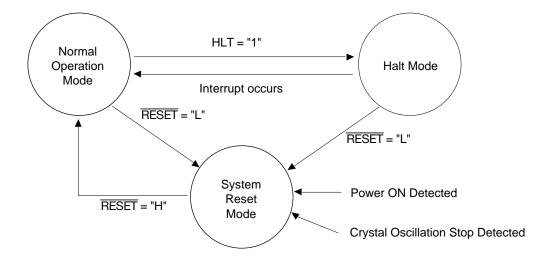

The MSM64167E has halt mode in addition to normal operation mode. Operation status can be classified as follows:

- Normal operation mode

- System reset mode

- Halt mode

Figure 3-1 shows the transition of each state.

Figure 3-1 Operation Status Transition Diagram

In normal operation mode, the CPU executes instructions successively. In system reset mode, the CPU enters system reset processing by reset input, and each register and pin are initialized to start execution of the instruction. After system reset processing, instruction execution starts from address 000H.

In halt mode, the CPU stops and instruction execution is interrupted. PC is not incremented. Although instruction execution stops, internal peripheral functions continue operation. To enter halt mode, set the HLT flag to "1".

Port and peripheral functions do not change even in halt mode.

#### 3.2 System Reset Function

#### 3.2.1 System Reset Mode

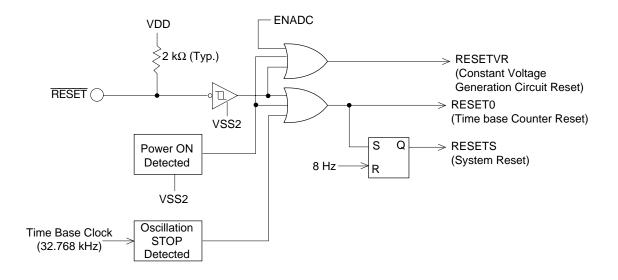

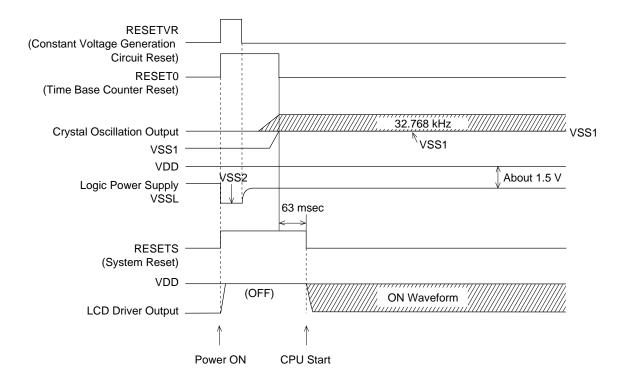

MSM64167E enters system reset mode if one of the following is met: a) power-on is detected, b) crystal oscillation STOP is detected, c) the  $\overrightarrow{\text{RESET}}$  pin is set to "L" level. In system clock mode, the following operation is performed:

- (1) CPU is initialized.

- (2) In power ON state, if the RESET pin is in "L" level, constant voltage generation circuit (VR) reaches excitation status.

- (3) Output of all LCD drivers are turned off at the VDD level. At about 63 ms after oscillation start, display wave forms are output to the LCD driver. (If not in LCD OFF mode)

- (4) All the special function registers (SFRs), other than TMD0-3, TMC0-3, are initialized.

After system reset, instruction execution starts from address 000H.

Figures 3-2 and 3-3 show the system reset generation circuit and each signal at system reset.

Figure 3-3 Each Signal at System Reset Generation

#### 3.2.2 Status at System Reset

Table 3-1 shows the status of the registers after system reset.

| Register/Flag                     | Value at system reset | Note                                           |

|-----------------------------------|-----------------------|------------------------------------------------|

| Program counter (PC)              | 000H                  |                                                |

| A register (A)                    | ОH                    |                                                |

| B register (B)                    | 0H                    |                                                |

| Carry flag (C)                    | 0                     |                                                |

| HL register pair (HL)             | 00H                   |                                                |

| XY register pair (XY)             | 00H                   |                                                |

| Stack pointer (SP)                | 0FFH                  |                                                |

| Bank select register 0 (BSR0)     | ОH                    |                                                |

| Bank select register 1 (BSR1)     | 0H                    |                                                |

| Bank common flag (BCF)            | 0                     |                                                |

| Bank enable flag (BEF)            | 0                     |                                                |

| Port 0 register (P0)              | 0H                    |                                                |

| Port 1 register (P1)              | 0H                    |                                                |

| Port 2 register (P2)              | 0H                    |                                                |

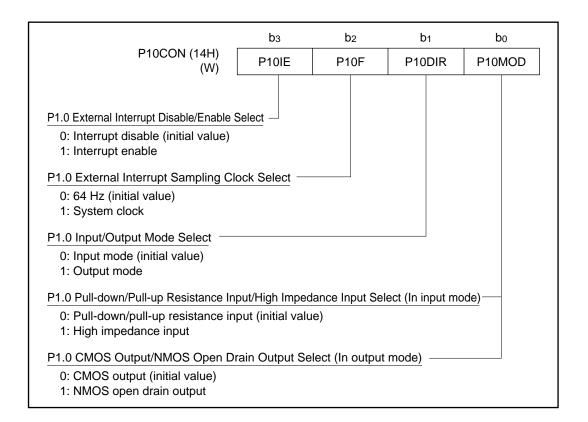

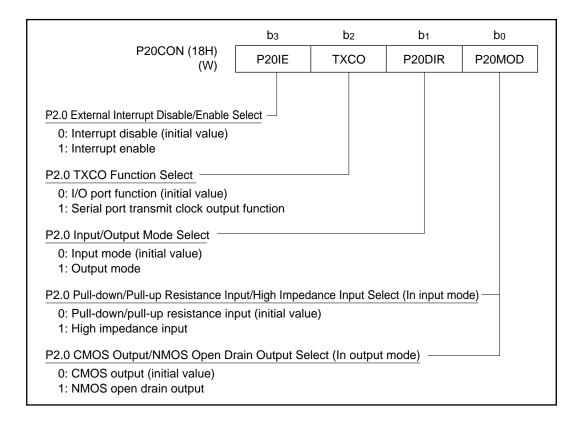

| Port 00 control register (P00CON) | ОH                    | Input mode, input with pull-up/pull-down       |

|                                   |                       | resistance, 64 Hz sampling, interrupt disabled |

| Port 01 control register (P01CON) | ОH                    | Input mode, input with pull-up/pull-down       |

|                                   |                       | resistance, 64 Hz sampling, interrupt disabled |

| Port 02 control register (P02CON) | ОH                    | Input mode, input with pull-up/pull-down       |

|                                   |                       | resistance, 64 Hz sampling, interrupt disabled |

| Port 03 control register (P03CON) | ОH                    | Input mode, input with pull-up/pull-down       |

|                                   |                       | resistance, 64 Hz sampling, interrupt disabled |

#### Table 3-1 (a) Initial Values at System Reset

| Register/Flag                                   | Value at system reset | Note                                           |

|-------------------------------------------------|-----------------------|------------------------------------------------|

| Port 10 control register (P10CON)               | ОН                    | Input mode, input with pull-up/pull-down       |

|                                                 |                       | resistance, 64 Hz sampling, interrupt disabled |

| Port 11 control register (P11CON)               | ОH                    | Input mode, input with pull-up/pull-down       |

|                                                 |                       | resistance, 64 Hz sampling, interrupt disabled |

| Port 12 control register (P12CON)               | ОH                    | Input mode, input with pull-up/pull-down       |

|                                                 |                       | resistance, 64 Hz sampling, interrupt disabled |

| Port 13 control register (P13CON)               | ОH                    | Input mode, input with pull-up/pull-down       |

|                                                 |                       | resistance, 64 Hz sampling, interrupt disabled |

| Port 20 control register (P20CON)               | ОH                    | Input mode, input with pull-up/pull-down       |

|                                                 |                       | resistance, 64 Hz sampling, interrupt disabled |

| Port 21 control register (P21CON)               | ОH                    | Input mode, input with pull-up/pull-down       |

|                                                 |                       | resistance, 64 Hz sampling, interrupt disabled |

| Port 22 control register (P22CON)               | ОH                    | Input mode, input with pull-up/pull-down       |

|                                                 |                       | resistance, 64 Hz sampling, interrupt disabled |

| Port 23 control register (P23CON)               | ОН                    | Input mode, input with pull-up/pull-down       |

|                                                 |                       | resistance, 64 Hz sampling, interrupt disabled |

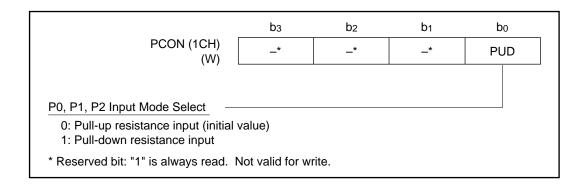

| Port control register (PCON)                    | 0EH                   | P0, P1, P2 input with pullup resistance        |

| Frequency control register (FCON)               | 0EH                   | Crystal oscillation clock                      |

| Buzzer driver control register                  | OН                    | Positive logic output, Buzzer disabled,        |

| (BDCON)                                         |                       | intermittent sound 1 output                    |

| Buzzer frequency control register               | 0EH                   | Buzzer frequency 4 kHz                         |

| (BFCON)                                         |                       |                                                |

| Display control register (DSPCON)               | 8H                    | 1/4 duty                                       |

| Display control registers 0 to 30 (DSPR0 to 30) | 0Н                    |                                                |

#### Table 3-1 (b) Initial Values at System Reset

|                                    | Value at     |                                |

|------------------------------------|--------------|--------------------------------|

| Register/Flag                      | system reset | Note                           |

| Timer data register 0 (TMD0)       | Undefined    |                                |

| Timer data register 1 (TMD1)       | Undefined    |                                |

| Timer data register 2 (TMD2)       | Undefined    |                                |

| Timer data register 3 (TMD3)       | Undefined    |                                |

| Timer counter register 0 (TMC0)    | Undefined    |                                |

| Timer counter register 1 (TMC1)    | Undefined    |                                |

| Timer counter register 2 (TMC2)    | Undefined    |                                |

| Timer counter register 3 (TMC3)    | Undefined    |                                |

| Timer control register 0 (TMCON0)  | ОH           | Auto reload mode, counter stop |

| Timer control register 1 (TMCON1)  | ОH           | TMCLK = 32.768 kHz             |

| Timer status register (TMSTAT)     | ОH           |                                |

| AD control register 0 (ADCON0)     | ОH           |                                |

| AD control register 1 (ADCON1)     | 1H           |                                |

| AD control register 2 (ADCON2)     | 8H           |                                |

| Transmit control register (L)      | он           |                                |

| (STCONL)                           |              |                                |

| Transmit control register (H)      | он           |                                |

| (STCONH)                           |              |                                |

| Transmit buffer register (L)       | он           |                                |

| (STBUFL)                           |              |                                |

| Transmit buffer register (H)       | он           |                                |

| (STBUFH)                           |              |                                |

| Receive control register (L)       | ОH           |                                |

| (SRCONL)                           |              |                                |

| Receive control register (H)       | ОН           |                                |

| (SRCONH)                           |              |                                |

| Receive baud rate setting register | 0CH          |                                |

| (SRBRT)                            |              |                                |

| Status Register (SSTAT)            | ОH           |                                |

#### Table 3-1 (c) Initial Values at System Reset

| Register/Flag                       | Value at system reset | Note                  |

|-------------------------------------|-----------------------|-----------------------|

| Watchdog timer control register     |                       | Stop                  |

| (WDTCON)                            |                       |                       |

| VSSL control register (VSSLCON)     | 0EH                   | VDD – 1.5 V level     |

| Interrupt request register 0 (IRQ0) | ОH                    |                       |

| Interrupt request register 1 (IRQ1) | ОH                    |                       |

| Interrupt request register 2 (IRQ2) | 0CH                   |                       |

| Interrupt enable register 0 (IE0)   | ОH                    | Interrupt disalbed    |

| Interrupt enable register 1 (IE1)   | ОH                    | Interrupt disabled    |

| Interrupt enable register 2 (IE2)   | 0EH                   | Interrupt disabled    |

| Halt mode register (HALT)           | 0EH                   | Normal operation mode |

| Master interrupt enable register    | 0EH                   | Interrupt disabled    |

| (MIEF)                              |                       |                       |

#### Table 3-1 (d) Initial Values at System Reset

**Note:** System reset has priority over all processings, stopping previous processing. Therefore, the content of RAM, TMD0–TMD3, and TMC0–TMC3, not initialized at system reset, is not guaranteed.

#### 3.3 Halt Mode

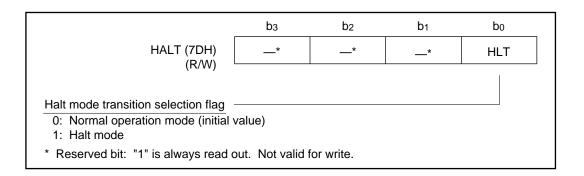

#### 3.3.1 Halt Mode Register (HALT)

This is a special function register (SFR) that controls conversion to halt mode.

#### Bit 0: HLT

Flag to enter halt mode. If the HLT flag is set to "1", CPU enters halt mode at the first machine cycle of the next instruction.

#### 3.3.2 Operation in Halt Mode

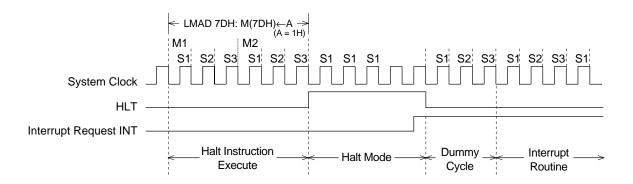

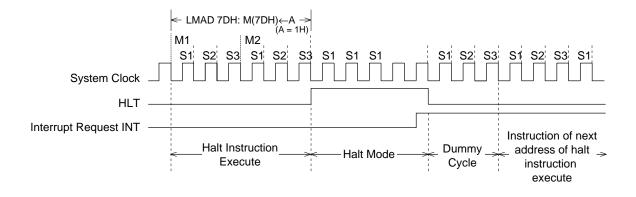

If an instruction to set an HLT flag to "1" is executed, the CPU enters halt mode at the first machine cycle of the next instruction. However, if in interrupt request status, the CPU does not enter halt mode.

In halt mode, oscillation and time base counter operations continue, and the CPU repeats fetching next instruction at S1 state.

Either system reset or an interrupt can release halt mode (reset HLT flag). If halt mode is released by an interrupt, set the interrupt enable flag used for release to "1" before entering halt mode.

Figure 3-4 shows the timing to enter halt mode and the release timing of halt mode by an interrupt.

Instruction execution after the release differs depending on the status of the master interrupt enable flag (MI). If the MI flag is "1", instruction execution restarts from the interrupt processing routine after one dummy cycle, as shown in Figure 3-4. If the MI flag is "0", instruction execution restarts from the next address of the halt instruction without a dummy cycle.

**Note:** To release halt mode, the individual interrupt enable flag must be set to "1", regardless of the MI flag state. If the individual interrupt enable flag is set to "0", the HLT flag cannot be reset, because of the interrupt request signal that corresponds to the enable flag.

If an individual interrupt enable flag was set, the interrupt request flag is set to "1", even if the MI flag is "0" when halt mode was released by an interrupt.

Figure 3-4 Timing of Halt Mode Set and Halt Mode Reset by Interrupt (when the MI flag = 1)

Figure 3-5 Timing of Halt Mode Set and Halt Mode Reset by Interrupt (when the MI flag = 0)

## Chapter 4

4

# Interrupt (INTC)

### Chapter 4 Interrupt (INTC)

#### 4.1 Overview

The MSM64167E has two external interrupt factors from ports and eight internal interrupt factors, totaling 10 interrupt factors (10 vector addresses). Of these 10 interrupt factors, only the watchdog timer interrupt cannot be disabled (non-maskable interrupt). Enable/disable of the other nine interrupts are controlled by the master interrupt enable flag (MI) and each interrupt enable register (IE0, IE1, IE2). If interrupt conditions are met, the program branches to vector addresses determined for each interrupt factor, and enters an interrupt routine.

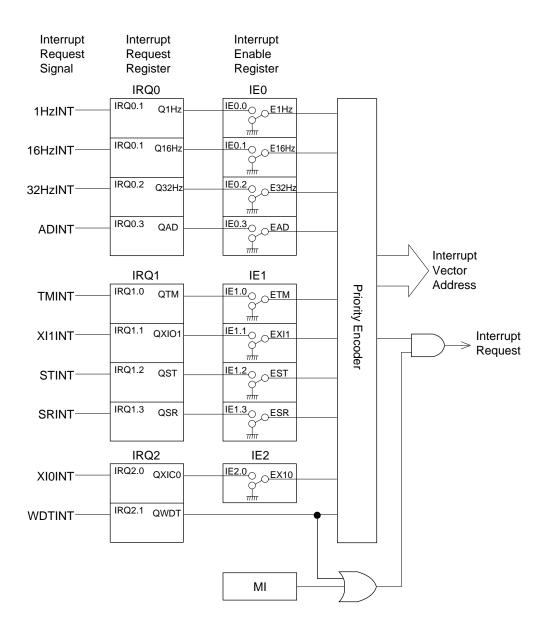

Table 4-1 lists interrupt factors. Figure 4-1 shows an interrupt control equivalent circuit.

| No. | Interrupt Factor               | Abbreviated Name | Vector Address |

|-----|--------------------------------|------------------|----------------|

| 1   | Watchdog timer interrupt       | WDTINT           | 03BH           |

| 2   | External 0 interrupt (P0, P1)  | XI0INT           | 038H           |

| 3   | Serial port receive interrupt  | SRINT            | 035H           |

| 4   | Serial port transmit interrupt | STINT            | 032H           |

| 5   | External 1 interrupt (P2)      | XI1INT           | 02FH           |

| 6   | Timer interrupt                | TMINT            | 02CH           |

| 7   | A/D converter interrupt        | ADINT            | 029H           |

| 8   | 32 Hz interrupt                | 32HzINT          | 026H           |

| 9   | 16 Hz interrupt                | 16HzINT          | 023H           |

| 10  | 1 Hz interrupt                 | 1HzINT           | 020H           |

#### Table 4-1 Interrupt Factors

If interrupt factors are generated at the same time, the interrupt with the bigger vector address has execution priority (WDTINT has the highest priority). For details on each interrupt operation, see Chapter 6 "Time Base Counter", Chapter 7 "Ports", Chapter 8 "Timer", Chapter 9 "Serial Port", Chapter 11 "Watchdog Timer" and Chapter 12 "A/D Converter".

**Note:** Interrupt requests generated under the following conditions are temporarily held.

- When skip conditions are established after executing a skip instruction. (A skip operation requires the same time as a machine cycle to execute the instruction to be skipped. Therefore such an interrupt request is held for the same length of time as a machine cycle to execute the instruction to be skipped.)

- 2) When LAI and LLI instructions (vertical stack instructions) are executed.

- 3) When ADCS and SUBCS instructions are executed.

If the next instruction does not satisfy the above conditions, interrupt requests that are held under the above conditions are accepted after the instruction is executed.

Figure 4-1 Interrupt Control Equivalent Circuit

#### 4.2 Interrupt Sequence

If interrupt conditions are met and the interrupt is accepted, the next interrupt process starts immediately after the executing instruction at that time ends, or immediately after one machine cycle (dummy cycle) if in halt mode.

Conversion to an interrupt routine is performed in five machine cycles after executing the following processes.

- (1) MI flag is reset to "0".

- (2) Content of PC, A, B, H and L registers and carry flag (C) are saved to a stack.

- (3) The stack pointer (SP) is decremented by 4. (SP  $\leftarrow$  SP 4)

- (4) Vector address is loaded to program counter (PC). At the same time, the interrupt request flag corresponding to the interrupt is reset.

Figure 4-2 shows the content of a stack after an interrupt is generated.

|                  |      | BANK7 |    |   |     |

|------------------|------|-------|----|---|-----|

|                  |      | 3     | 2  | 1 | 0   |

| Position of SP   |      | 0     | 1  | 1 | 1   |

| before interrupt | OFEH | PC11  | to | D | PC8 |

|                  | 0FDH | PC7   | to | o | PC4 |

|                  | OFCH | PC3   | to | C | PC0 |

|                  | _2   |       | E  | 3 |     |

|                  | 0FAH |       | A  | Ą |     |

|                  | 0F9H |       | F  | 1 |     |

|                  | 0F8H |       | L  | _ |     |

| Position of SP   | 0F7H |       |    |   |     |

| after interrupt  | 0F6H |       |    |   |     |

|                  | -    |       |    |   |     |

Figure 4-2 Content of Stack after Interrupt is Generated

Use an RTI instruction to return from interrupt routine.

The return cycle is performed in five machine cycles. The following processes are executed.

- (1) Content of PC, A, B, H and L registers and carry flag (C) are returned from a stack.

- (2) The stack pointer (SP) is incremented by 4. (SP  $\leftarrow$  SP + 4)

- (3) MI flag is set to "1".

#### 4.3 Interrupt Control Registers

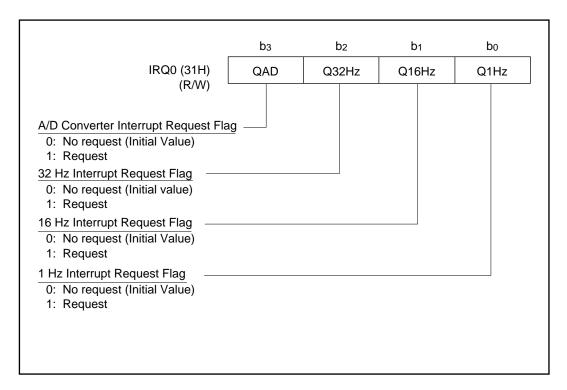

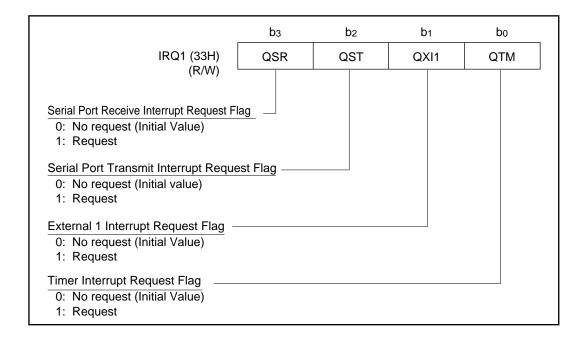

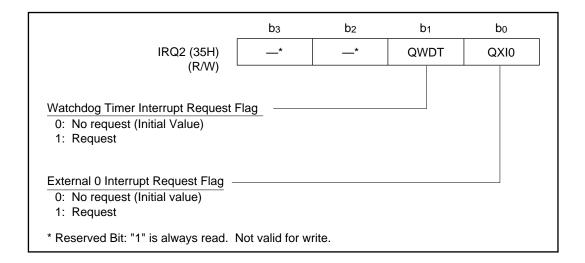

#### 4.3.1 Interrupt Request Registers (IRQ0, IRQ1 and IRQ2)

Interrupt request registers (IRQ0, IRQ1 and IRQ2) are 4-bit registers. If an interrupt request is generated, the corresponding bit is set to "1" at the first S1 state. If an interrupt was enabled by an interrupt enable register (IE0 to 2) at this time, an interrupt is requested to the CPU. The watchdog timer, however, has no interrupt mask function by an interrupt enable register.

A software interrupt occurs by writing "1" to an interrupt request register.

If an interrupt is accepted, corresponding bits to IRQ0, IRQ1, and IRQ2 are reset to "0" by hardware during an interrupt conversion cycle.

IRQ0, IRQ1, and IRQ2 are initialized to 0H at system reset.

Bit 3: QAD

Set to "1" by counter over flow signal of A/D converter.

Bit 2: Q32Hz

Set to "1" at fall of 32 Hz of time base counter.

Bit 1: Q16Hz

Set to "1" at fall of 16 Hz of time base counter.

Bit 0: Q1Hz

Set to "1" at fall of 1 Hz of time base counter.

#### Bit 3: QSR

Set to "1" if receive data of serial port is set to receive register.

#### Bit 2: QST

Set to "1" if transmit data of serial port is set to transmit register.

#### Bit 1: QXI1

Set to "1" by change of input level of P2.0–P2.3.

#### Bit 0: QTM

Set to "1" by overflow of timer.

#### Bit 1: QWDT

Set to "1" by overflow of watchdog timer. Interrupt cannot be disabled by interrupt enable register.

#### Bit 0: QXI0

Set to "1" by change of input level of P0.0–P0.3 and P1.0–P1.3.

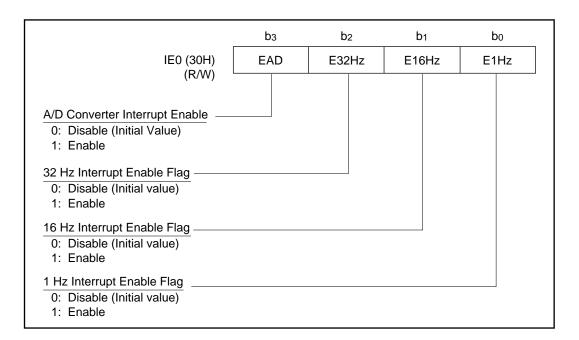

#### 4.3.2 Interrupt Enable Registers (IE0, IE1 and IE2)

Interrupt enable registers (IE0, IE1 and IE2) are 4-bit registers that determine whether each interrupt is requested to the CPU, depending on the logical product with the corresponding bits of interrupt request registers (IRQ0, IRQ1 and IRQ2).

If multiple interrupts are requested to the CPU at the same time, the interrupt with the highest priority (bigger vector address) shown in Table 4-1, and other interrupt requests are held.

During an interrupt conversion cycle, the mask interrupt enable flag (MI) is cleared to "0", but each IE0 to 2 bit is not.

Held interrupt requests are held until the MI flag is set to "1" when processing an accepted interrupt request. If interrupt processing is ended by an RTI instruction, the MI flag is automatically set, and held interrupt requests are accepted.

Interrupt enable registers (IE0 to 2) can be rewritten only when the master enable flag (MI) is reset to "0".

#### MSM64167E User's Manual Chapter 4 Interrupt (INTC)

|                                                                                            | bз     | b2  | b1   | bo         |

|--------------------------------------------------------------------------------------------|--------|-----|------|------------|

| IE1 (32H)                                                                                  | ESR    | EST | EXI1 | ETM        |

| (R/W)<br>Serial Port Receive Interrupt Enable F<br>0: Disable (Initial Value)<br>1: Enable | -lag — |     |      |            |

| Serial Port Transmit Interrupt Enabl<br>0: Disable (Initial value)<br>1: Enable            | e Flag |     |      |            |

| External 1 Interrupt Enable Flag —<br>0: Disable (Initial value)<br>1: Enable              |        |     |      |            |

| Timer Interrupt Enable Flag<br>0: Disable (Initial value)<br>1: Enable                     |        |     |      |            |

|                                                                                            |        | ha  |      | ha         |

| IE2 (34H)                                                                                  | b3     | b2  | b1   | b0<br>EXI0 |

| (R/W)<br>External 0 Interrupt Enable Flag —                                                |        |     |      |            |

0: Disable (Initial Value)

1: Enable

\* Reserved Bit: "1" is always read. Not valid for write.

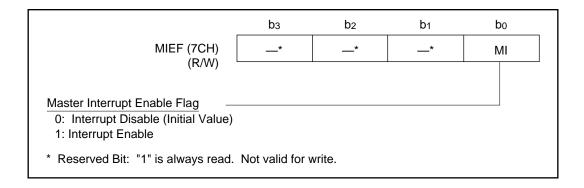

#### 4.3.3 Master Interrupt Enable Register (MIEF)

The MI flag in the master interrupt enable register (MIEF) controls disable/enable of all interrupts except the watchdog timer interrupt. If the MI flag is set to "1", an interrupt is enabled, and if reset to "0", interrupt is disabled. The MI flag is reset to "0" during an interrupt conversion cycle when an interrupt is accepted, and is set to "1" by executing an RTI instruction, a return instruction from an interrupt processing routine.

By setting the MI flag to "1" during an interrupt processing routine, multiple interrupt processing is possible.

Table 4-2 shows interrupt related registers.

| Register Name                    | Symbol | Address | Read/Write | Value at System Reset |

|----------------------------------|--------|---------|------------|-----------------------|

| Interrupt Enable Register 0      | IE0    | 30H     | R/W        | 0H                    |

| Interrupt Request Register 0     | IRQ0   | 31H     | R/W        | 0H                    |

| Interrupt Enable Register 1      | IE1    | 32H     | R/W        | 0H                    |

| Interrupt Request Register 1     | IRQ1   | 33H     | R/W        | 0H                    |

| Interrupt Enable Register 2      | IE2    | 34H     | R/W        | 0EH                   |

| Interrupt Request Register 2     | IRQ2   | 35H     | R/W        | 0CH                   |

| Master Interrupt Enable Register | MIEF   | 7CH     | R/W        | 0EH                   |

#### Table 4-2 Interrupt Related Registers

## Chapter 5

# **Clock Generation Circuit (2CLK)**

### Chapter 5 Clock Generation Circuit (2CLK)

#### 5.1 Overview

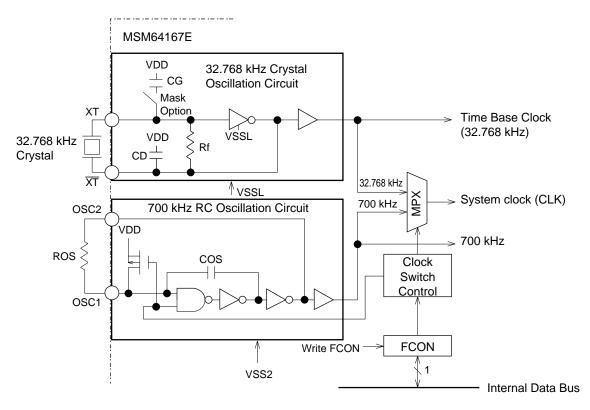

The clock generation circuit (2CLK) is comprised of a 32.768 kHz crystal oscillation circuit, a 700 kHz RC oscillation circuit and a clock control component, generating a system clock (CLK), crystal oscillation clock (32.768 kHz) and a RC oscillation clock (700 kHz).

The system clock is the basic operation clock for the CPU. The crystal oscillation clock is the basic operation clock for the time base counter and for the buzzer driver. The crystal oscillation clock and the RC oscillation clock can be the timer clock source supplying the timer.

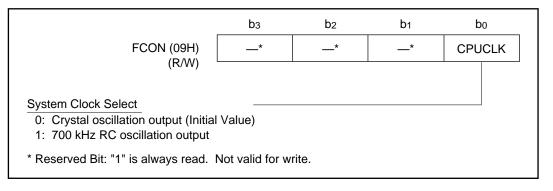

The frequency of the system clock can be switched to either 32.768 kHz, the crystal oscillation circuit output, or to 700 kHz, the output of the RC oscillation circuit.

**Note:** The oscillation frequency of the RC oscillation circuit fluctuates depending on the value of external resistance (ROS), operating power voltage (VSS2), ambient temperature (Ta), etc. For explanatory purposes, this manual regards the output of the RC oscillation circuit as 700 kHz.

#### 5.2 Configuration of Clock Generation Circuit

Figure 5-1 shows the configuration of the clock generation circuit.

Figure 5-1 Configuration of Clock Generation Circuit

#### 5.3 Operation of Clock Generation Circuit

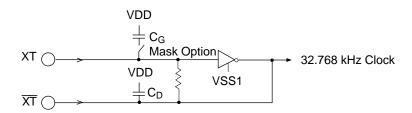

The 32.768 kHz crystal oscillation circuit oscillates by an external 32.768 kHz crystal. When this frequency is finely adjusted by an external capacitor, the internal capacity (CG) can be cut off by a mask option.

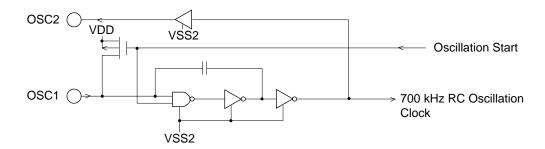

The 700 kHz RC oscillation circuit oscillates by external resistance (ROS). The RC oscillation circuit operates only when the system clock is selected to the 700 kHz RC oscillation clock, or when it is set to the RC oscillation test mode. Otherwise oscillation stops.

For details on test functions, see Chapter 15, Test Circuit.

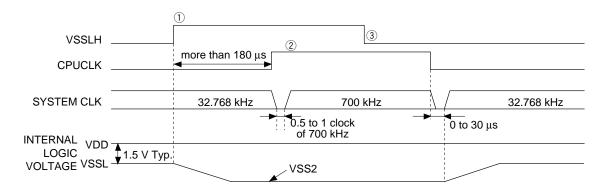

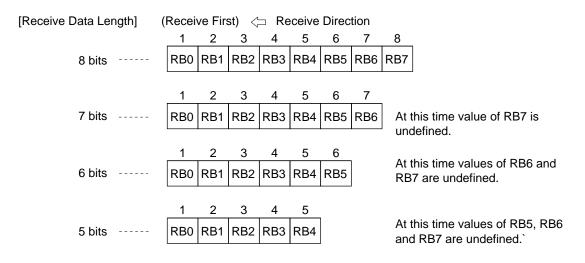

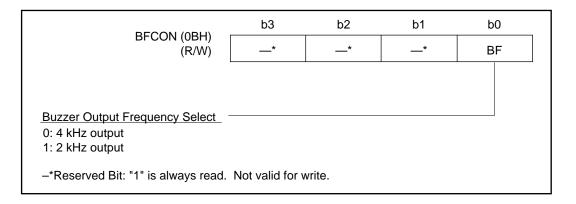

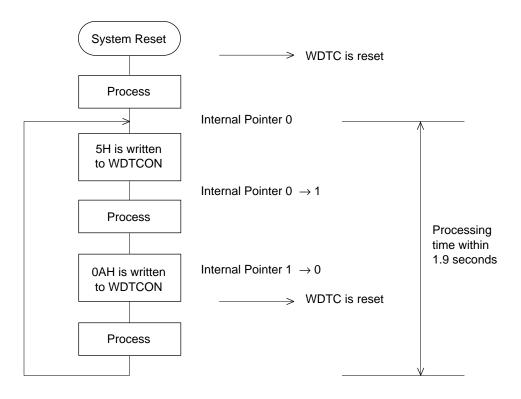

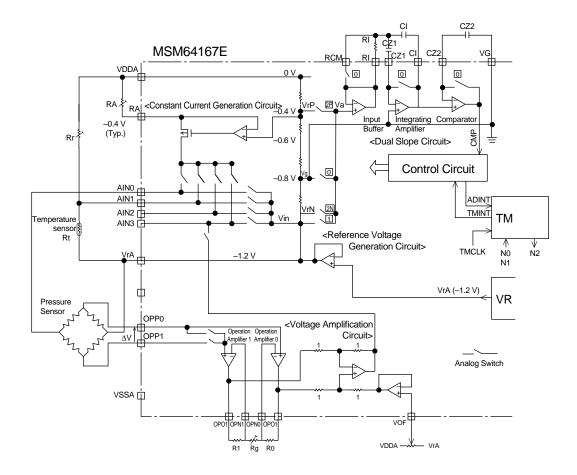

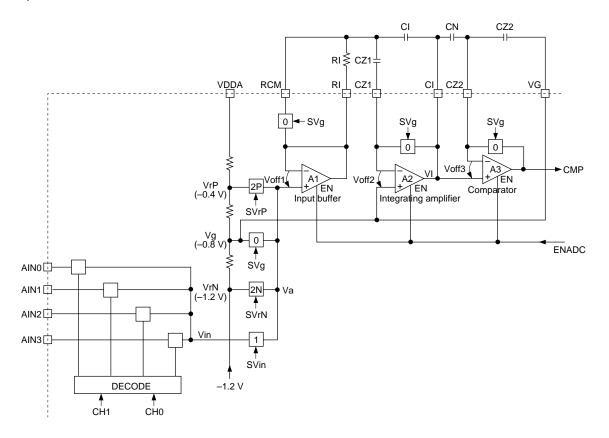

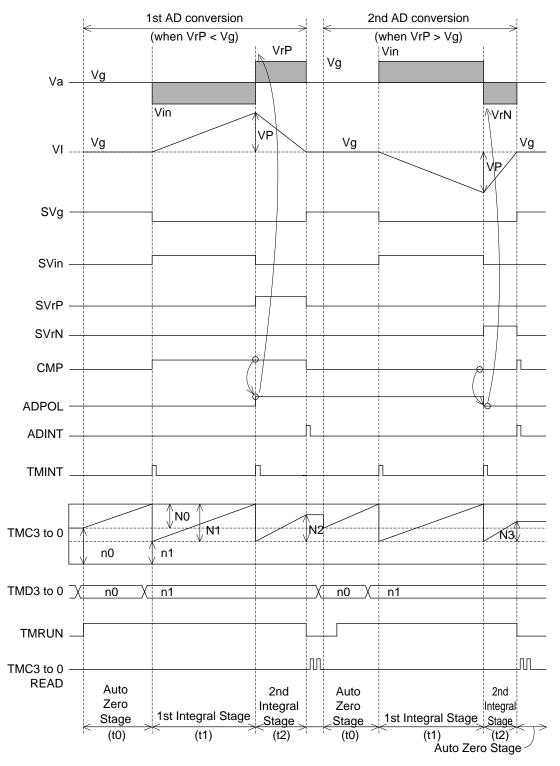

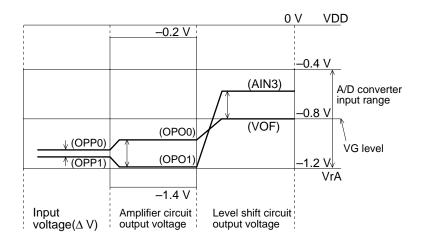

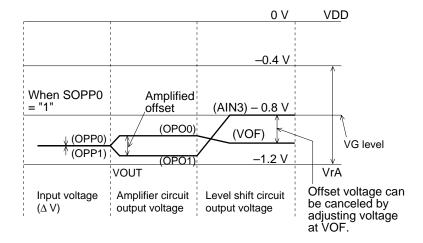

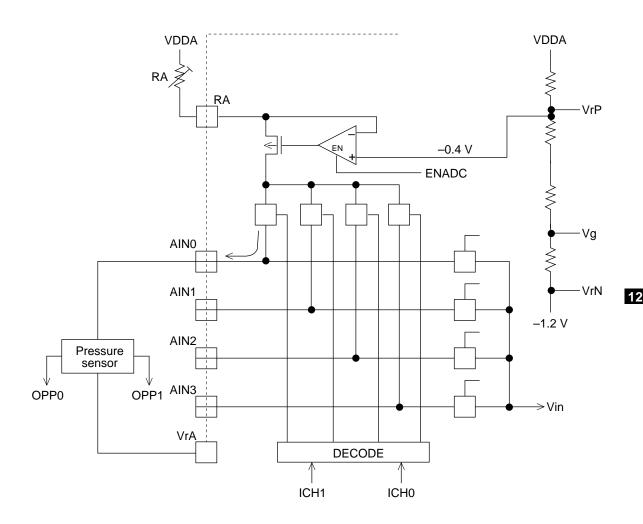

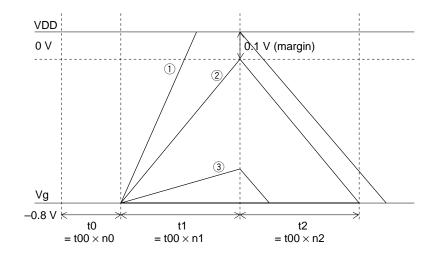

The system clock is selected by the frequency control register (FCON). If bit 0 (CPUCLK) of FCON is reset to "0", the output of crystal oscillation circuit (32.768 kHz) becomes the system clock. If CPUCLK is set to "1", the output of the RC oscillation circuit (700 kHz) becomes the system clock. Even if the RC oscillation circuit is selected, the crystal oscillation circuit does not stop oscillation.