# **OKI** Semiconductor

This version: Jan. 1998 Previous version: Dec. 1996

## MSM514212

5,048-Word × 8-Bit Line Memory

#### **DESCRIPTION**

The OKI MSM514212 is a high-performance serial-line memory. It is designed for use in NTSC, PAL or SECAM Video line buffer applications such as digital comb filters in TVs/VTRs, IDTV (Improved Definition Television), time based correction, or other applications that use serial data including facsimiles, digital copy machines, etc. High-reliability and low-power consumption are accomplished by using CMOS dynamic memory cells.

It has separate 8-bit-wide serial input and serial output ports that use independent data clocks to support asynchronous read and write operations. Different clock rates are also supported that allow alternate data rates between input and output data streams.

A wide range of variable delay bits (40 bits to 5,048 bits) are supported offering greater design flexibility. Internal logic keeps all asynchronous accesses from being delayed by arbitrating the data storage, and data retrieval requirements to provide maximum performance at all times.

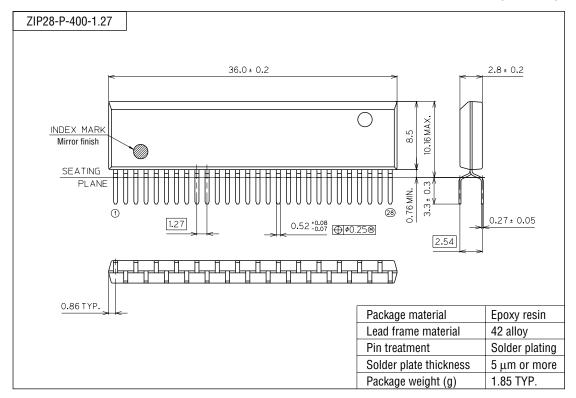

All input and output signals are TTL compatible, and the MSM514212 is packaged in a standard 400 mil 28-pin plastic ZIP.

#### **FEATURES**

Single power supply: 5 V ±10%

Capacity: 5,048 words × 8 bits

Access: I/O asynchronous

Access time: 28 ns (min.)Cycle time: 28 ns (min.)

• Delay bits: Variable (40 to 5,048)

Low current consumption: 30 mA (max.)

Operating voltage range: 4.5 V to 5.5 V

Operating temperature range: 0°C to 70°C

Package :

28-pin 400 mil plastic ZIP (ZIP28-P-400-1.27) (Product : MSM514212-xxZS) xx indicates speed rank.

#### PRODUCT FAMILY

| Family       | Cycle Time (Min.) | Access Time (Min.) | Power Dissipation (Max.) |

|--------------|-------------------|--------------------|--------------------------|

| MSM514212-28 | 28 ns             | 28 ns              | 230 mA                   |

| MSM514212-34 | 34 ns             | 34 ns              | 200 mA                   |

| MSM514212-50 | 50 ns             | 40 ns              | 170 mA                   |

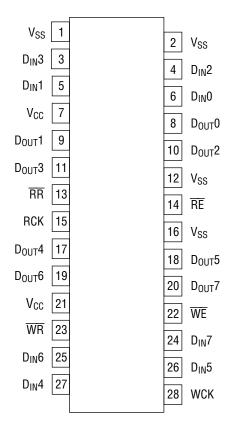

## PIN CONFIGURATION (TOP VIEW)

28-Pin Plastic ZIP

| Pin Name               | Function            |  |  |  |  |

|------------------------|---------------------|--|--|--|--|

| WCK                    | Write Clock         |  |  |  |  |

| WR                     | Write Address Reset |  |  |  |  |

| WE                     | Write Enable        |  |  |  |  |

| D <sub>IN</sub> 0 - 7  | Data Input          |  |  |  |  |

| RCK                    | Read Clock          |  |  |  |  |

| RR                     | Read Address Reset  |  |  |  |  |

| RE                     | Read Enable         |  |  |  |  |

| D <sub>OUT</sub> 0 - 7 | Data Output         |  |  |  |  |

| V <sub>CC</sub>        | Power Supply (5 V)  |  |  |  |  |

| V <sub>SS</sub>        | Ground (0 V)        |  |  |  |  |

Note: The same power supply voltage must be provided to every  $V_{CC}$  pin, and the same GND voltage level must be provided to every  $V_{SS}$  pin.

**BLOCK DIAGRAM**

#### $D_{OUT}0$ $D_{0UT}1$ $D_{OUT}2$ $D_{0UT}3$ $D_{\underset{\bigcirc}{O}}$ D<sub>OUT</sub>5 $D_{0 \cup T} 6$ D<sub>OUT</sub>7 Read Timing RCK Controller Data-out Data-out Data-out Data-out Data-out Data-out Data-out Data-out -⊙ <u>RE</u> Buffer Buffer Buffer Buffer Buffer Buffer Buffer Buffer Read Reset $\overline{RR}$ Controller 32-Word 32-Word 32-Word 32-Word 32-Word 32-Word 32-Word 32-Word Data Register Read/Write 5032 5032 5032 5032 5032 5032 5032 5032 Read/Write Χ Memory Memory Memory Memory Memory Memory Memory Memory Controller Select Controller Decoder Array Array Array Array Array Array Array Array 32-Word 32-Word 32-Word 32-Word 32-Word 32-Word 32-Word 32-Word Data Register Write Reset $V_{BB}$ 0-Controller Generator 16-Word 16-Word 16-Word 16-Word 16-Word 16-Word 16-Word 16-Word Sub-Register Sub-Register Sub-Register Sub-Register Sub-Register Sub-Register Sub-Register Sub-Register 16-Word 16-Word 16-Word 16-Word 16-Word 16-Word 16-Word 16-Word Sub-Register Sub-Register Sub-Register Sub-Register Sub-Register Sub-Register Sub-Register Sub-Register Write Timing WCK O Controller Data-in Data-in Data-in Data-in Data-in Data-in Data-in Data-in → WE Buffer Buffer Buffer Buffer Buffer Buffer Buffer Buffer Ó Ó Ó 0 Q Ó Ó Ò $D_{IN}0$ $D_{IN}1$ $D_{IN}2$ $D_{IN}3$ $D_{IN}4$ $D_{IN}5$ D<sub>IN</sub>6 $D_{IN}7$

#### **ELECTRICAL CHARACTERISTICS**

## **Absolute Maximum Ratings**

| Parameter                   | Symbol           | Condition         | Rating      | Unit |

|-----------------------------|------------------|-------------------|-------------|------|

| Pin Voltage Relative to Vss | VT               | at Ta = 25°C, Vss | -1.0 to 7.0 | V    |

| Power Supply Voltage        | Vcc              | at Ta = 25°C, Vcc | -1.0 to 7.0 | V    |

| Circuit Output Current      | Ιo               | Ta = 25°C         | 20          | mA   |

| Operating Temperature       | T opr            | _                 | 0 to 70     | °C   |

| Storage Temperature         | T <sub>stg</sub> | _                 | -55 to 150  | °C   |

## **Recommended Operating Conditions**

| Parameter            | Symbol          | Condition | Min. | Тур. | Max. | Unit |

|----------------------|-----------------|-----------|------|------|------|------|

| Power Supply Voltage | Vcc             | _         | 4.5  | 5.0  | 5.5  | V    |

| Input High Voltage   | V <sub>IH</sub> | _         | 2.4  | _    | 5.5  | V    |

| Input Low Voltage    | V <sub>IL</sub> | _         | -1.5 | _    | 0.8  | V    |

| Temperature Around   | Та              | _         | 0    | _    | 70   | °C   |

## **DC Characteristics (On the Recommended Operating Conditions)**

| Parameter                 | Symbol          | Condition                                    | Min. | Тур. | Max. | Unit |

|---------------------------|-----------------|----------------------------------------------|------|------|------|------|

| Power Supply Current      | I <sub>CC</sub> | _                                            | _    | _    | 30   | mA   |

| Input Leakage Current     | I <sub>1</sub>  | $V_I = 0$ to Vcc, Other pins are 0 V         | -10  | _    | 10   | μA   |

| Output Leakage Current    | Io              | $V_O = 0$ to 5.5 V, $D_{OUT}$ high impedance | -10  | _    | 10   | μA   |

| Output High Level Voltage | Vон             | I <sub>OH</sub> = -1 mA                      | 2.4  | _    | _    | V    |

| Output Low Level Voltage  | VoL             | I <sub>OL</sub> = 2 mA                       |      | _    | 0.4  | V    |

## Capacitance

$(V_{CC} = 5 \text{ V} \pm 10\%, \text{ Ta} = 25^{\circ}\text{C}, \text{ f} = 1 \text{ MHz})$

| Parameter          | Symbol | Condition | Min. | Тур. | Max. | Unit |

|--------------------|--------|-----------|------|------|------|------|

| Input Capacitance  | Сі     | _         | _    | _    | 5    | pF   |

| Output Capacitance | Со     | _         | _    | _    | 7    | pF   |

## **AC Characteristics (On the Recommended Operating Conditions)**

| Parameter                              | Symbol            | -2   | 28   | -34  |      | -50  |      | Unit |

|----------------------------------------|-------------------|------|------|------|------|------|------|------|

|                                        |                   | Min. | Max. | Min. | Max. | Min. | Max. |      |

| Write Clock Cycle Time                 | t wck             | 28   | 1980 | 34   | 1980 | 50   | 1980 | ns   |

| Write Clock Pulse Width                | t wcw             | 11   | _    | 14   | _    | 20   | _    | ns   |

| Write Clock Precharge Time             | t wcp             | 11   | _    | 14   | _    | 20   | _    | ns   |

| Read Clock Cycle Time                  | t RCK             | 28   | 1980 | 34   | 1980 | 50   | 1980 | ns   |

| Read Clock Pulse Width                 | t <sub>RCW</sub>  | 11   | _    | 14   |      | 20   | _    | ns   |

| Read Clock Precharge Time              | t <sub>RCP</sub>  | 11   | _    | 14   | _    | 20   | _    | ns   |

| Access Time                            | t AC              | _    | 28   | _    | 34   | _    | 40   | ns   |

| Cycle Access Time Right After Reset    | t ACR             | _    | 28   | _    | 34   |      | 40   | ns   |

| Output Hold Time                       | t он              | 5    | _    | 5    | _    | 5    | _    | ns   |

| Output Hold Time Right After Reset     | t ohr             | 5    | _    | 5    | _    | 5    | _    | ns   |

| Output Low Impedance Period            | t <sub>LZ</sub>   | 5    | 28   | 5    | 34   | 5    | 40   | ns   |

| Output High Impedance Period           | t <sub>HZ</sub>   | 5    | 28   | 5    | 34   | 5    | 40   | ns   |

| Input Data Setup Time                  | t DS              | 11   | _    | 14   | _    | 15   | _    | ns   |

| Input Data Hold Time                   | t DH              | 5    | _    | 5    | _    | 5    | _    | ns   |

| WR/RR Setup Time from WCK/RCK          | t RS              | 11   | _    | 14   | _    | 15   | _    | ns   |

| WR/RR Hold Time from WCK/RCK           | t <sub>RH</sub>   | 5    | _    | 5    | _    | 5    | _    | ns   |

| WR/RR Nonselective Time 1 from         | t <sub>RN1</sub>  | 5    | _    | 5    | _    | 5    | _    | ns   |

| WCK/RCK                                |                   |      |      |      |      |      |      |      |

| WR/RR Nonselective Time 2 from WCK/RCK | t <sub>RN2</sub>  | 11   | _    | 14   | _    | 15   | _    | ns   |

| WE Setup Time from WCK                 | t wes             | 11   | _    | 14   | _    | 15   | _    | ns   |

| WE Hold Time from WCK                  | t weh             | 5    | _    | 5    |      | 5    | _    | ns   |

| WE Nonselective Time 1 from WCK        | t WEN1            | 5    | _    | 5    | _    | 5    | _    | ns   |

| WE Nonselective Time 2 from WCK        | t WEN2            | 11   | _    | 14   | _    | 15   | _    | ns   |

| RE Setup Time from RCK                 | t RES             | 11   | _    | 14   | _    | 15   | _    | ns   |

| RE Hold Time from RCK                  | t REH             | 5    | _    | 5    | _    | 5    | _    | ns   |

| RE Nonselective Time 1 from RCK        | t REN1            | 5    | _    | 5    | _    | 5    | _    | ns   |

| RE Nonselective Time 2 from RCK        | t REN2            | 11   | _    | 14   | _    | 15   | _    | ns   |

| WE High Level Period                   | t wew             | 0    | _    | 0    | _    | 0    | _    | ns   |

| RE High Level Period                   | t REW             | 0    | _    | 0    | _    | 0    | _    | ns   |

| WR Low Level Period (Write Reset       | t                 | 0    |      |      |      | 0    |      | nc   |

| Period)                                | t <sub>RSTW</sub> | 0    |      | 0    |      | 0    |      | ns   |

| WR Low Level Period (Read Reset        | t =               | 0    |      | _    |      | _    |      | no   |

| Period)                                | t <sub>RSTR</sub> | 0    | _    | 0    | _    | 0    | _    | ns   |

| Transition Time                        | t T               | 3    | 35   | 3    | 35   | 3    | 35   | ns   |

Notes:

1. The input voltage reference levels stipulated in the timing specification are  $V_{IH} = 3.0 \text{ V}$  and  $V_{IL} = 0 \text{ V}$ . The  $t_T$  is the transition time between  $V_{IH} = 3.0 \text{ V}$  and  $V_{IL} = 0 \text{ V}$

- 2. Rise and fall time  $t_T$  of all the cycles is specified as 5 ns.

- 3. During asynchronous execution of write and read operation, the difference between the write address and read address must be greater than 40.

- 4. Since the MSM514212 uses a dynamic memory cell, it can read the data of the written address within 10 ms after the write cycle at that address is completed.

- 5. The load condition for measurement is based on 1 TTL + 30 pF.

- 6. All the potential to the power supply/grounding terminals needs to be supplied.

## **SIGNAL DESCRIPTIONS**

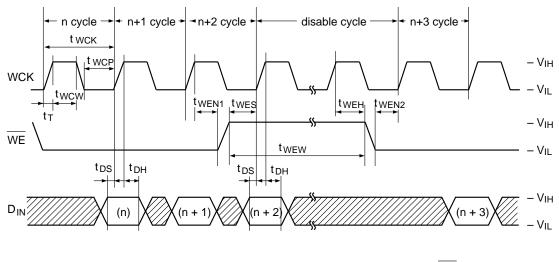

#### Data Inputs (D<sub>IN</sub>0 - D<sub>IN</sub>7)

Data on these inputs is shifted in on the rising edge of WCK while  $\overline{WE}$  is held at a low level. The data setup and hold times  $t_{DS}$  and  $t_{DH}$  are referenced to the rising edge of WCK.

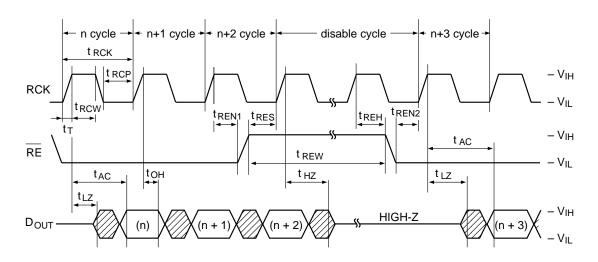

#### Data Outputs (D<sub>OUT</sub>0 - D<sub>OUT</sub>7)

Data is shifted out on these outputs during the rising edge of RCK while  $\overline{RE}$  is held at a low level. The data becomes valid after the access time interval  $t_{AC}$  which begins at the rising edge of RCK.

## Write Address Pointer Reset (WR)

If  $\overline{WR}$  is brought to a low level, the next rising edge of WCK resets the write address pointer to the first address location. The write address pointer is automatically reset when the last address location (5048) is clocked. The  $\overline{WR}$  setup, and hold times  $t_{RS}$  and  $t_{RH}$  are referenced to the rising edge of WCK. Each write operation, which begins after  $\overline{WR}$ , must contain at least 18 active write cycles, i.e. WCK cycles while  $\overline{WE}$  is high.

### Read Address Pointer Reset (RR)

If RR is brought to a low level, the next rising edge of RCK resets the read address pointer to the first address location. The read address pointer is automatically reset when the last address location (5048) is clocked. The  $\overline{RR}$  setup, and hold times  $t_{RS}$  and  $t_{RH}$  are referenced to the rising edge of WCK. Each read operation, which begins after  $\overline{RR}$ , must contain at least 18 active read cycles, i.e. RCK cycles while  $\overline{RE}$  is high.

### Write Enable (WE)

This pin is used as a gating function for the WCK input. If  $\overline{\text{WE}}$  is held low, normal write cycles can occur. If  $\overline{\text{WE}}$  is brought to a high level before the next rising edge of WCK, all subsequent write cycles will be inhibited, and the write address pointer remains unchanged. The  $\overline{\text{WE}}$  setup and hold times  $t_{\text{WES}}$  and  $t_{\text{WEH}}$  are referenced to the rising edge of WCK.

#### Read Enable (RE)

This pin is used as a gating function for the RCK input. If RE is brought to a high level before the next rising edge of RCK, all subsequent read cycles are inhibited, and the read address pointer remains unchanged. The data outputs will tri-state after the output buffer turn off delay time  $t_{\rm HZ}$ , which begins at the rising edge of RCK. After the disabled cycles are completed, and the RE signal is brought back to a low level, the data output buffers are re-enabled by the next rising edge of RCK. The RE setup, and hold times  $t_{\rm RES}$  and  $t_{\rm REH}$  are referenced to the rising edge of RCK.

#### Write Clock (WCK)

The rising edge of the WCK input latches the data into the internal registers, and also increments the write address pointer when WE is held low.

#### Read Clock (RCK)

The rising edge of the RCK input shifts out the data from the internal registers and increments the read address pointer when  $\overline{\text{RE}}$  is held low.

#### **OPERATION MODE**

#### **Write Cycle**

When  $\overline{\text{WE}}$  input is enabled (at the "L" level), the write cycle is executed by synchronizing it with the WCK clock input. Read and write data is processed by the same clock in the write cycle to carry out the video processing. Data is input after a delay of oneline (5048 bits) is input at the rising edge of the clock in the write cycle.

In addition, when the length of the delay is controlled by  $\overline{\text{WE}}$ , the value of the delay bits is from 40 to 5048. The  $\overline{\text{WR}}$  operation must be performed now to write the last data to memory cell.

#### **Read Cycle**

When  $\overline{RE}$  input is enabled (at the "L" level), the read cycle is executed by synchronizing it with the RCK clock input. Data is output at  $t_{AC}$  (or  $t_{ACR}$ ). In addition, when the length of the delay is controlled by  $\overline{RE}$ , the value of the delay bits is from 40 to 5048.

## Write Reset Cycle Read Reset Cycle

When the power supply is on, the address values of the read and write address pointers are at random. Thus, each pointer must be initialized by the  $\overline{RR}$  signal and the  $\overline{WR}$  signal beforehand. Data can be input (to address 0) with the first cycle after this reset operation.

#### Power-up and Initialization

On power-up, the device is designed to begin proper operation after at least 100  $\mu$ s after V<sub>CC</sub> has stabilized to a value within the range of recommended operating conditions. After this 100  $\mu$ s stabilization interval, the following initialization sequence must be performed.

Because the read and write address counters are not valid after power-up, a minimum of 18 dummy write operations (WCK cycles) and read operations (RCK cycles) must be performed, followed by a  $\overline{WR}$  operation and an  $\overline{RR}$  operation, to properly initialize the write and the read address pointer. Dummy write cycles/ $\overline{WR}$  and dummy read cycles/ $\overline{RR}$  may occur simultaneously. If these dummy read and write operations start while  $V_{CC}$  and/or the substrate voltage has not stabilized, it is necessary to perform an  $\overline{RR}$  operation plus a minimum of 18 RCK cycles plus another  $\overline{RR}$  operation, and a  $\overline{WR}$  operation plus a minimum of 18 WCK cycles plus another  $\overline{WR}$  operation to properly initialize read and write address pointers.

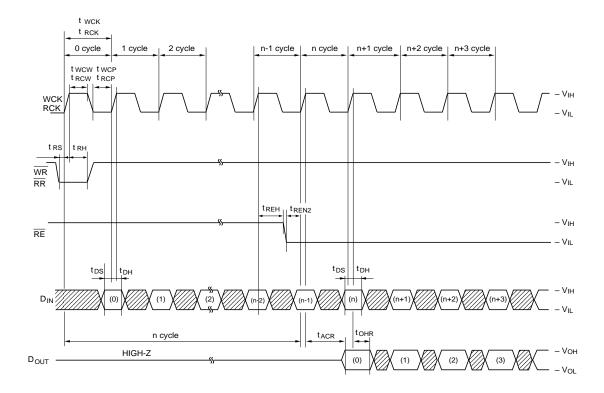

#### **TIMING WAVEFORM**

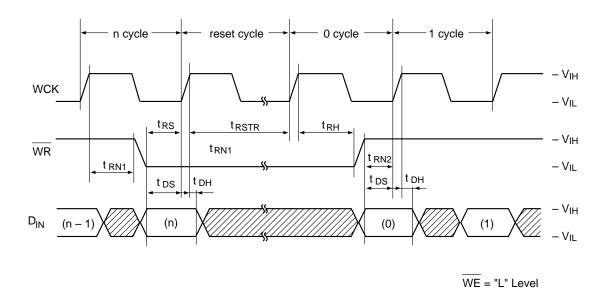

## **Write Cycle**

WR = "H" Level

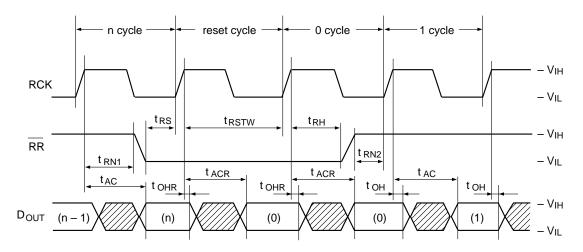

## **Read Cycle**

RR = "H" Level

#### **Write Reset Cycle**

#### **Read Reset Cycle**

RE = "L" Level

**Note:** In the write reset and read reset cycles, the reset cycle (for the duration of  $t_{RSTW}$ ,  $t_{RSTR}$ ) is not necessarily required for the reset operation.

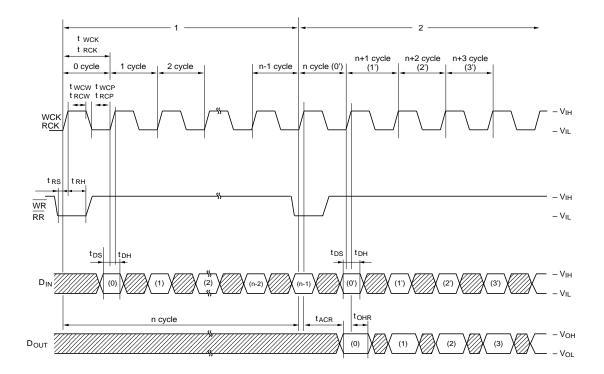

## n Bit Delay Line Timing (1)

$\overline{RE}$ ,  $\overline{WE}$  = "L" Level

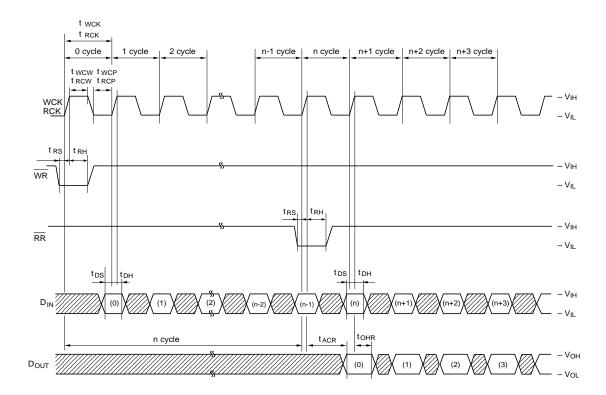

## n Bit Delay Line Timing (2)

$\overline{RE}$ ,  $\overline{WE}$  = "L" Level

#### n Bit Delay Line Timing (3)

$\overline{\text{WE}}$  = "L" Level

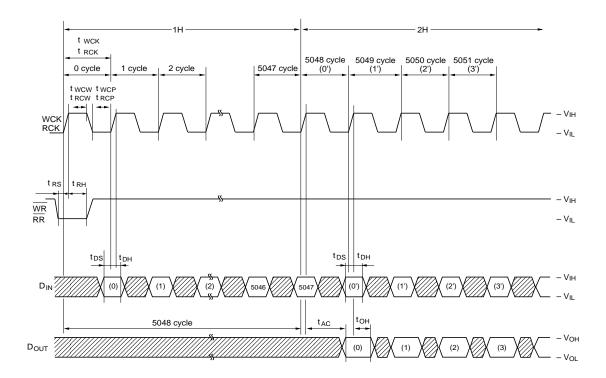

## 1 H Delay Line Timing

$\overline{RE}$ ,  $\overline{WE}$  = "L" Level

## **PACKAGE DIMENSIONS**

(Unit: mm)