## **OKI** Semiconductor

# ML670100 Users' Manual

Version 1.0 of April, 1999

#### NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit and assembly designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. OKI assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to: traffic control, automotive, safety, aerospace, nuclear power control, and medical, including life support and maintenance.

- 7. Certain products in this document may need governmental approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 1998 OKI ELECTRIC INDUSTRY CO., LTD.

ARM, Thumb and ARM POWERED logo are the registered trademarks of ARM Ltd. ARM7TDMI and EmbeddedICE are the trademarks of ARM Ltd.

The signal names of negative logic are being changed to nXXX from XXX in this users manual.

## Contents

| 1   | Overv                                                  | view                                                   |      |  |  |  |  |  |

|-----|--------------------------------------------------------|--------------------------------------------------------|------|--|--|--|--|--|

| 1.1 | Features                                               |                                                        |      |  |  |  |  |  |

| 1.2 | Block [                                                | ock Diagram                                            |      |  |  |  |  |  |

| 1.3 | Pins                                                   |                                                        | 1-5  |  |  |  |  |  |

|     | 1.3.1                                                  | Pin Layout                                             | 1-5  |  |  |  |  |  |

|     | 1.3.2                                                  | Pin Functions                                          | 1-6  |  |  |  |  |  |

|     | 1.3.3                                                  | Treatment of Unused Pins                               | 1-10 |  |  |  |  |  |

|     | 1.3.4                                                  | Configurations of Pins and I/O ports                   | 1-11 |  |  |  |  |  |

| 2   | CPU                                                    |                                                        | 2-1  |  |  |  |  |  |

| 2.1 | CPU O                                                  | perating States                                        | 2-2  |  |  |  |  |  |

| 2.2 | Switchi                                                | ing State                                              | 2-2  |  |  |  |  |  |

| 2.3 | Memor                                                  | Memory Formats                                         |      |  |  |  |  |  |

| 2.4 | Instruct                                               | tion Length                                            | 2-3  |  |  |  |  |  |

| 2.5 | Instruction Length 2- Data Types 2- Operating Modes 2- |                                                        |      |  |  |  |  |  |

| 2.6 | Operat                                                 |                                                        |      |  |  |  |  |  |

| 2.7 | Registe                                                | ers                                                    | 2-3  |  |  |  |  |  |

|     | 2.7.1                                                  | The ARM state register set                             | 2-4  |  |  |  |  |  |

|     | 2.7.2                                                  | The THUMB state register set                           | 2-6  |  |  |  |  |  |

|     | 2.7.3                                                  | The relationship between ARM and THUMB state registers | 2-7  |  |  |  |  |  |

|     | 2.7.4                                                  | Accessing Hi registers in THUMB state                  | 2-7  |  |  |  |  |  |

| 2.8 | The Pr                                                 | ogram Status Registers                                 | 2-8  |  |  |  |  |  |

|     | 2.8.1                                                  | The condition code flags                               | 2-8  |  |  |  |  |  |

|     | 2.8.2                                                  | The control bits                                       | 2-8  |  |  |  |  |  |

| 2.9 | Except                                                 | ions                                                   | 2-9  |  |  |  |  |  |

|     | 2.9.1                                                  | Action on entering an exception                        | 2-10 |  |  |  |  |  |

|     | 2.9.2                                                  | Action on leaving an exception                         | 2-10 |  |  |  |  |  |

|     | 2.9.3                                                  | Exception entry/exit summary                           | 2-10 |  |  |  |  |  |

|     | 2.9.4                                                  | FIQ                                                    | 2-11 |  |  |  |  |  |

|     | 2.9.5                                                  | IRQ                                                    | 2-11 |  |  |  |  |  |

|     | 2.9.6                                                  | Software interrupt                                     | 2-12 |  |  |  |  |  |

|      | 2.9.7    | Undefined instruction                   | 2-12 |

|------|----------|-----------------------------------------|------|

|      | 2.9.8    | Exception vectors                       | 2-12 |

|      | 2.9.9    | Exception priorities                    | 2-13 |

| 2.10 | Reset    |                                         | 2-13 |

|      |          |                                         |      |

| 3    | CPU (    | Control Functions                       | 3-1  |

| 3.1  | Overvi   | ew                                      | 3-2  |

|      | 3.1.1    | Pins                                    | 3-2  |

|      | 3.1.2    | Control Registers                       | 3-3  |

| 3.2  | Control  | Registers                               | 3-3  |

|      | 3.2.1    | Standby Control Register (SBYCON)       | 3-3  |

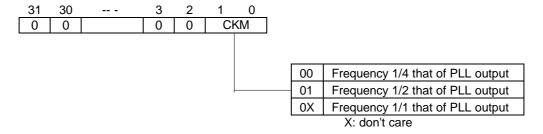

|      | 3.2.2    | Clock Control Register (CKCON)          | 3-4  |

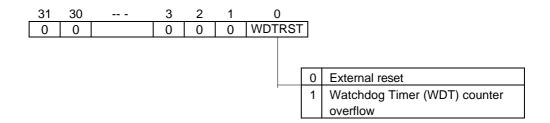

|      | 3.2.3    | Reset Status Register (RSTST)           | 3-5  |

| 3.3  | System   | Resets                                  | 3-6  |

|      | 3.3.1    | External Reset Signal (nRST)            | 3-6  |

|      | 3.3.2    | Watchdog Timer (WDT) Counter Overflow   | 3-6  |

| 3.4  | Clock S  | Signals                                 | 3-7  |

| 3.5  | Standb   | y Mode                                  | 3-8  |

| 4    | Interru  | upt Controller                          | 4-1  |

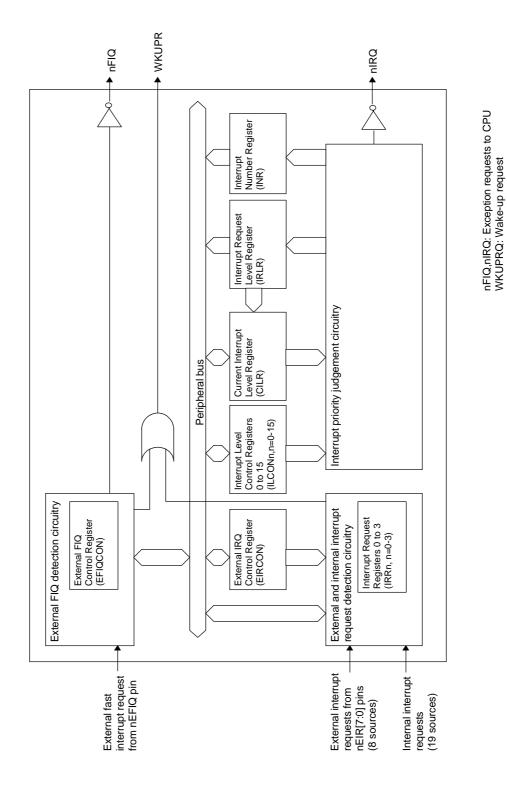

| 4.1  | Overvi   | ew                                      | 4-2  |

|      | 4.1.1    | Block Diagram                           | 4-2  |

|      | 4.1.2    | Pins                                    | 4-4  |

|      | 4.1.3    | Control Registers                       | 4-4  |

| 4.2  | Interrup | ot Sources                              | 4-5  |

|      | 4.2.1    | External Fast Interrupt Requests        | 4-5  |

|      | 4.2.2    | External Interrupt Requests             | 4-5  |

|      | 4.2.3    | Internal Interrupt Requests             | 4-6  |

|      | 4.2.4    | Interrupt Source Mappings               | 4-6  |

| 4.3  | Control  | Registers                               | 4-8  |

|      | 4.3.1    | Interrupt Number Register (INR)         | 4-8  |

|      | 4.3.2    | Current Interrupt Level Register (CILR) | 4-8  |

|      | 4.3.3    | Interrupt Request Level Register (IRLR) | 4-9  |

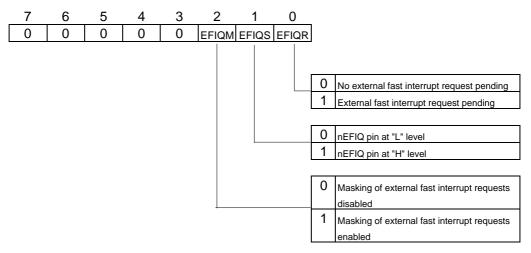

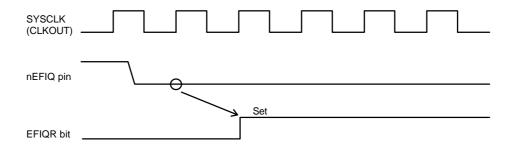

|      | 4.3.4    | External FIQ Control Register (EFIQCON) | 4-10 |

|     | 4.3.5    | External IRQ Control Register (EIRCON)                        | 4-11 |

|-----|----------|---------------------------------------------------------------|------|

|     | 4.3.6    | Interrupt Request Registers 0 to 3 (IRRn, n=0 - 3)            | 4-12 |

|     | 4.3.7    | Interrupt Level Control Registers 0 to 15 (ILCONn, n=0 - 15)  | 4-12 |

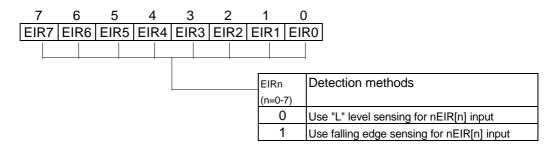

| 4.4 | Interrup | ot Processing                                                 | 4-14 |

|     | 4.4.1    | External Fast Interrupt Requests                              | 4-14 |

|     | 4.4.2    | External and Internal Interrupt Requests                      | 4-14 |

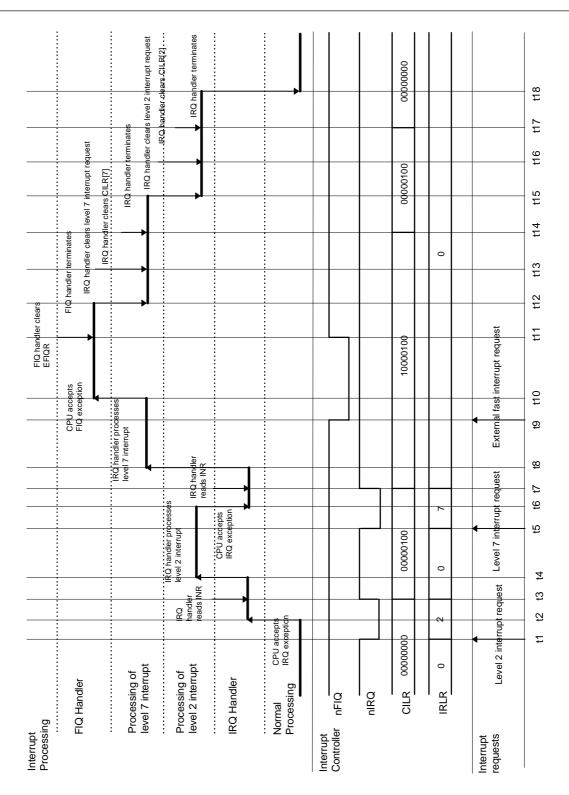

| 4.5 | Sampli   | ng Timing for External Interrupt Requests                     | 4-20 |

| 4.6 | Interrup | ot Response Times                                             | 4-21 |

| 5   | I/O Po   | orts                                                          | 5-1  |

| 5.1 | Overvi   | ew                                                            | 5-2  |

|     | 5.1.1    | Control Registers                                             | 5-4  |

| 5.2 | Control  | Registers                                                     | 5-5  |

|     | 5.2.1    | Port Output Registers 0 to 8 (POn, n=0 - 8)                   | 5-5  |

|     | 5.2.2    | Port Input Registers 0 to 8 (PIn, n=0 - 8)                    | 5-5  |

|     | 5.2.3    | Port Mode Registers 0 to 8 (PMn, n=0 - 8)                     | 5-6  |

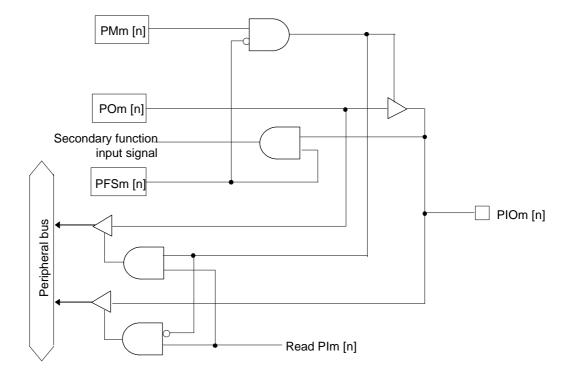

|     | 5.2.4    | Port Function Selection Registers 0 to 5, 7(PFSn, n=0 - 5, 7) | 5-6  |

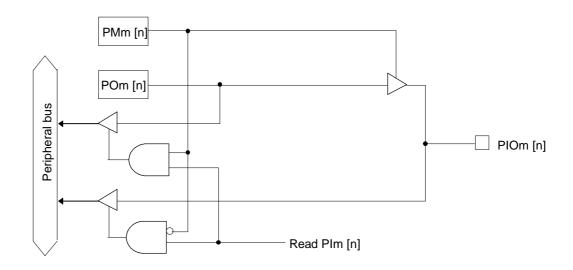

| 5.3 | I/O Por  | t Operation                                                   | 5-9  |

|     | 5.3.1    | Configuration after System Reset                              | 5-9  |

|     | 5.3.2    | Reading from I/O Ports                                        | 5-9  |

|     | 5.3.3    | Writing to I/O Ports                                          | 5-9  |

| 6   | Time     | Base Generator                                                | 6-1  |

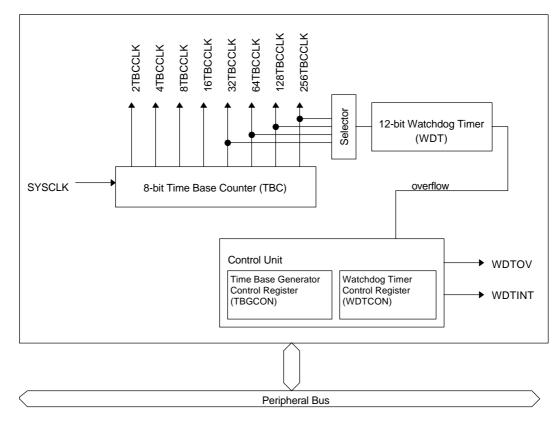

| 6.1 | Overvi   | ew                                                            | 6-2  |

|     | 6.1.1    | Block Diagram                                                 | 6-2  |

|     | 6.1.2    | Control Registers                                             | 6-3  |

| 6.2 | Control  | Registers                                                     | 6-4  |

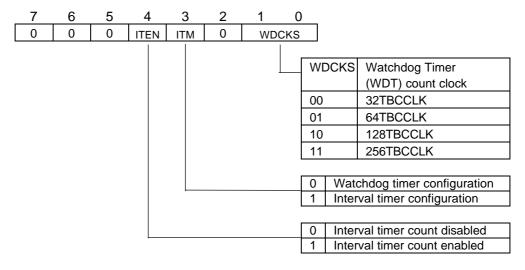

|     | 6.2.1    | Watchdog Timer Control Register (WDTCON)                      | 6-4  |

|     | 6.2.2    | Time Base Generator Control Register (TBGCON)                 | 6-4  |

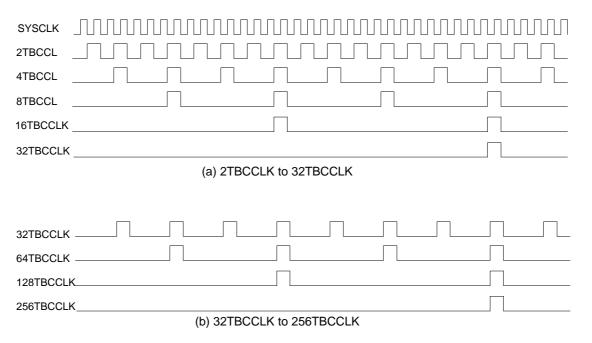

| 6.3 | Time B   | ase Generator (TBG) Operation                                 | 6-6  |

|     | 6.3.1    | Time Base Counter (TBC)                                       | 6-6  |

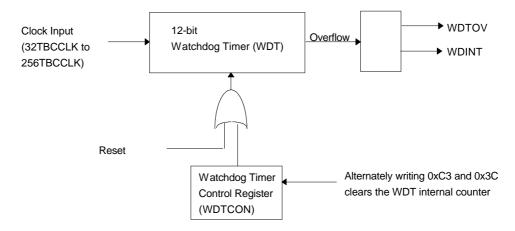

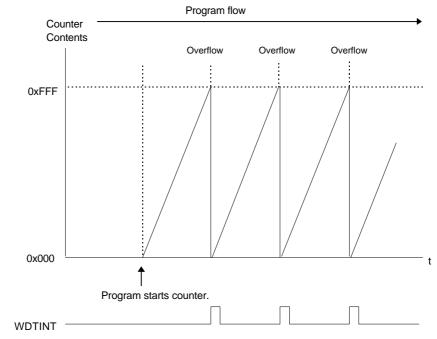

|     | 6.3.2    | Watchdog Timer (WDT)                                          | 6-7  |

|     | 6.3.3    | Time to Overflow                                              | 6-8  |

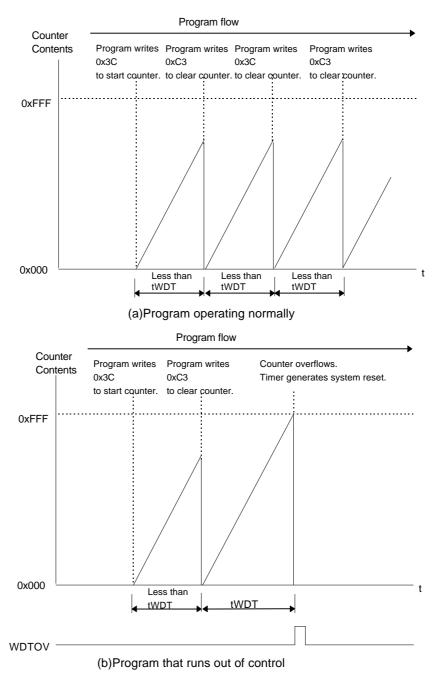

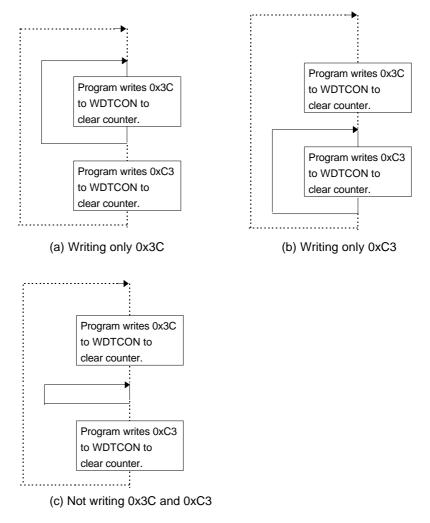

|     | 6.3.4    | WDT Watchdog Timer Operation                                  | 6-8  |

|     | 6.3.5    | WDT Interval Timer Operation                            | 6-11 |  |  |  |  |

|-----|----------|---------------------------------------------------------|------|--|--|--|--|

| 7   | Flexib   | ole Timer                                               | 7-1  |  |  |  |  |

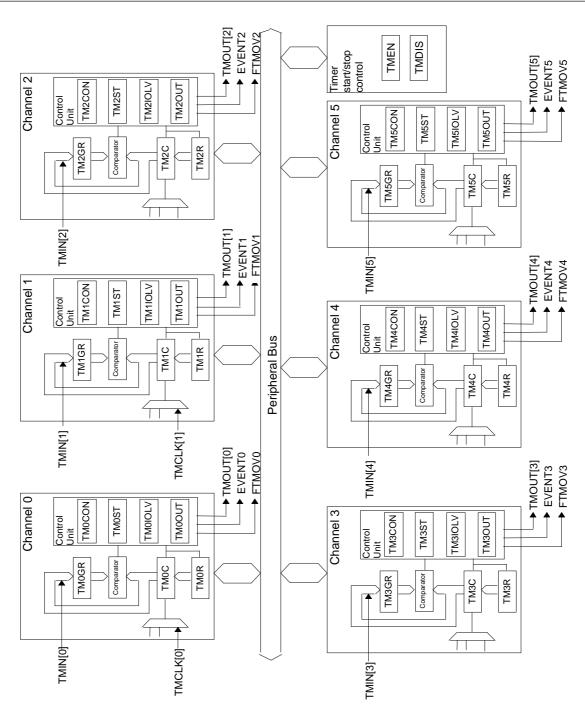

| 7.1 | Overvi   | Overview                                                |      |  |  |  |  |

|     | 7.1.1    | Block Diagram                                           | 7-2  |  |  |  |  |

|     | 7.1.2    | Pins                                                    | 7-4  |  |  |  |  |

|     | 7.1.3    | Control Registers                                       | 7-4  |  |  |  |  |

| 7.2 | Contro   | I Registers                                             | 7-6  |  |  |  |  |

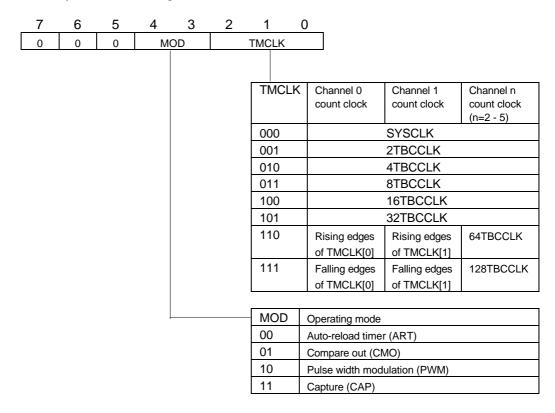

|     | 7.2.1    | Timer Control Registers 0 to 5 (TMnCON, n=0 - 5)        | 7-6  |  |  |  |  |

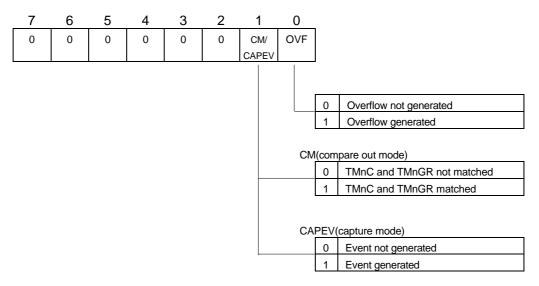

|     | 7.2.2    | Timer Status Registers 0 to 5 (TMnST, n=0 - 5)          | 7-7  |  |  |  |  |

|     | 7.2.3    | Timer Counters 0 to 5 (TMnC, n=0 - 5)                   | 7-8  |  |  |  |  |

|     | 7.2.4    | Timer Registers 0 to 5 (TMnR, n=0 - 5)                  | 7-9  |  |  |  |  |

|     | 7.2.5    | Timer General-Purpose Registers 0 to 5 (TMnGR, n=0 - 5) | 7-9  |  |  |  |  |

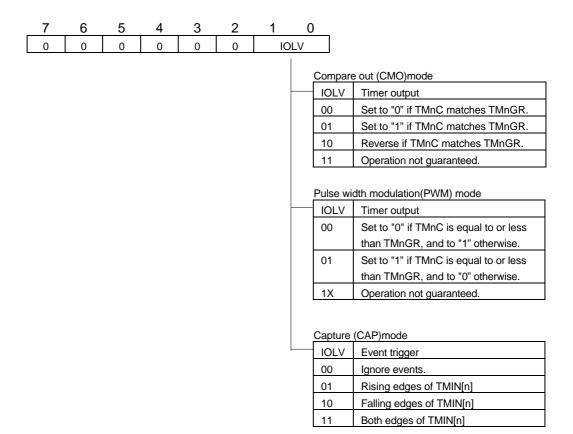

|     | 7.2.6    | Timer I/O Level Registers 0 to 5 (TMnIOLV, n=0 - 5)     | 7-10 |  |  |  |  |

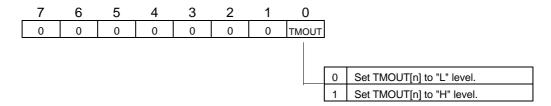

|     | 7.2.7    | Timer Output Registers 0 to 5 (TMnOUT, n=0 - 5)         | 7-12 |  |  |  |  |

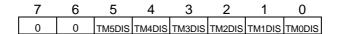

|     | 7.2.8    | Timer Enable Register (TMEN)                            | 7-13 |  |  |  |  |

|     | 7.2.9    | Timer Disable Register (TMDIS)                          | 7-13 |  |  |  |  |

| 7.3 | Flexible | e Timer (FTM) Operation                                 | 7-14 |  |  |  |  |

|     | 7.3.1    | Selecting Count Clock and Starting/Stopping Timers      | 7-14 |  |  |  |  |

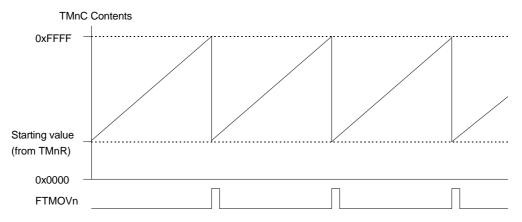

|     | 7.3.2    | Auto-Reload Timer (ART) Mode                            | 7-15 |  |  |  |  |

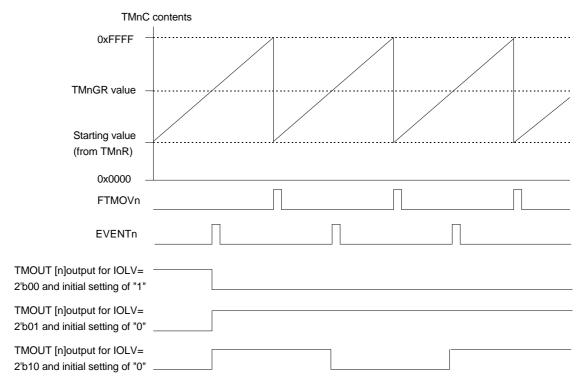

|     | 7.3.3    | Compare Out (CMO) Mode                                  | 7-15 |  |  |  |  |

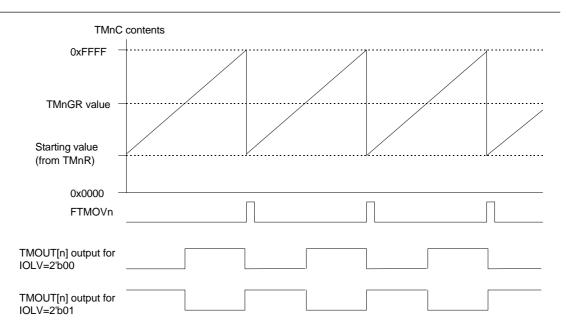

|     | 7.3.4    | Pulse Width Modulation (PWM) Mode                       | 7-16 |  |  |  |  |

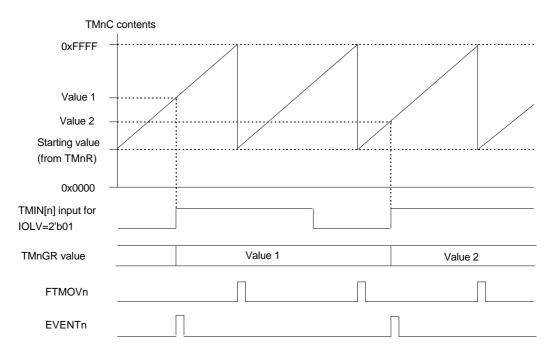

|     | 7.3.5    | Capture (CAP) Mode                                      | 7-17 |  |  |  |  |

|     | 7.3.6    | Synchronizing Starts and Stops                          | 7-18 |  |  |  |  |

| 7.4 | Signal   | Timing                                                  | 7-19 |  |  |  |  |

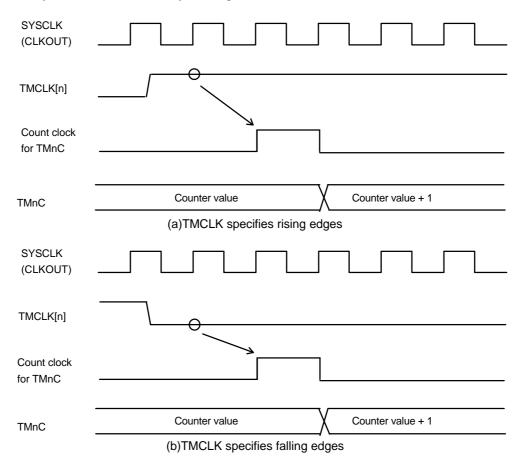

|     | 7.4.1    | Timer Clock Input Sampling                              | 7-19 |  |  |  |  |

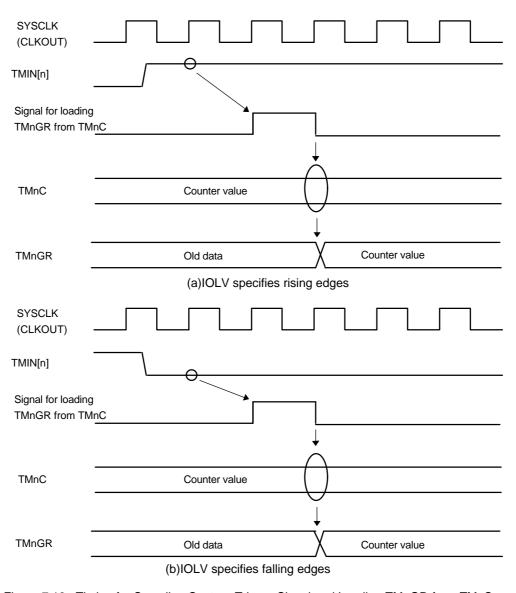

|     | 7.4.2    | Capture Trigger Input Sampling                          | 7-20 |  |  |  |  |

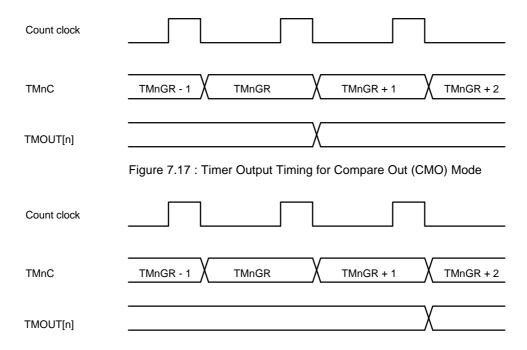

|     | 7.4.3    | Timer Output Timing                                     | 7-22 |  |  |  |  |

| 8   | Asyno    | chronous Serial Interface                               | 8-1  |  |  |  |  |

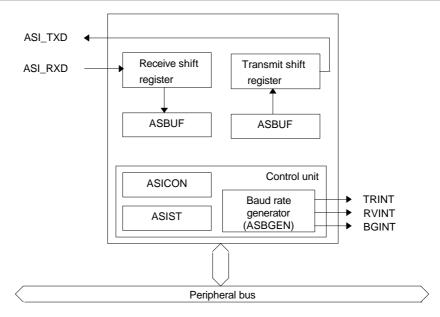

| 8.1 | Overvi   | ew                                                      | 8-2  |  |  |  |  |

|     | 8.1.1    | Block Diagram                                           | 8-2  |  |  |  |  |

|     | 8.1.2    | Pins                                                    | 8-4  |  |  |  |  |

|     | 8.1.3    | Control Registers                                       | 8-4  |  |  |  |  |

| 0.0  | Ossatusl          | Deviators                                    | 0.5  |  |

|------|-------------------|----------------------------------------------|------|--|

| 8.2  |                   | Registers ACL Control Borriston (ACLCON)     | 8-5  |  |

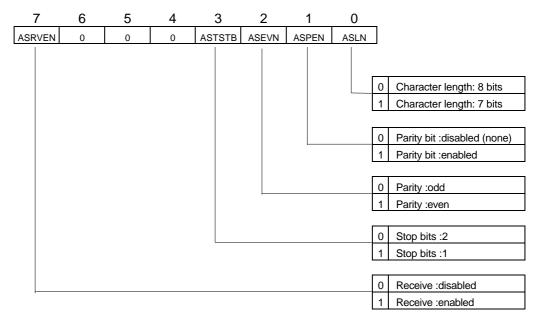

|      | 8.2.1             | ASI Control Register (ASICON)                | 8-5  |  |

|      | 8.2.2             | ASI Buffer Register (ASBUF)                  | 8-6  |  |

|      | 8.2.3             | ASI Shift Registers                          | 8-6  |  |

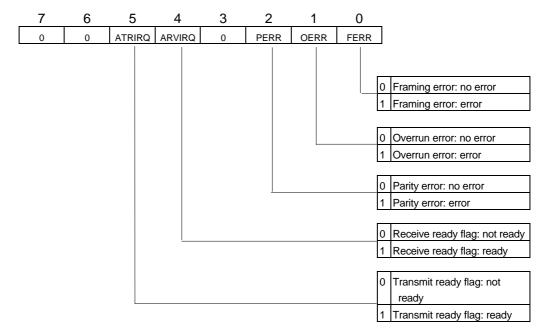

|      | 8.2.4             | ASI Status Register (ASIST)                  | 8-7  |  |

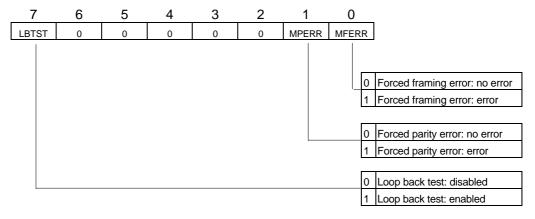

|      | 8.2.5             | ASI Test Control Register (ASTSCON)          | 8-9  |  |

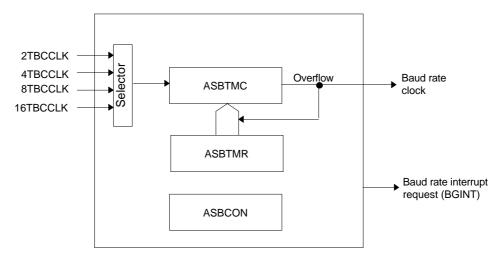

|      | 8.2.6             | Baud Rate Timer Counter (ASBTMC)             | 8-10 |  |

|      | 8.2.7             | Baud Rate Timer Register (ASBTMR)            | 8-10 |  |

|      | 8.2.8             | Baud Rate Control Register (ASBCON)          | 8-11 |  |

| 8.3  | Asynch            | ronous Serial Interface (ASI) Operation      | 8-13 |  |

|      | 8.3.1             | Baud Rate Generator (ASBGEN) Operation       | 8-13 |  |

|      | 8.3.2             | Setting Communications Parameters            | 8-16 |  |

|      | 8.3.3             | Transmitting Data                            | 8-16 |  |

|      | 8.3.4             | Receiving Data                               | 8-17 |  |

| 9    | Clock             | Synchronous Serial Interface                 | 9-1  |  |

| 9.1  | Overvie           | ew                                           | 9-2  |  |

|      | 9.1.1             | Block Diagram                                | 9-2  |  |

|      | 9.1.2             | Pins                                         | 9-3  |  |

|      | 9.1.3             | Control Registers                            | 9-3  |  |

| 9.2  | Control Registers |                                              |      |  |

|      | 9.2.1             | CSI Control Registers 0,1 (CSInCON, n=0,1)   | 9-4  |  |

|      | 9.2.2             | CSI Shift Registers 0,1 (CSInSFT, n=0,1)     | 9-5  |  |

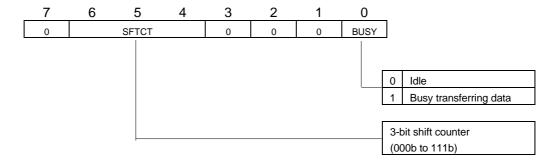

|      | 9.2.3             | CSI Status Registers 0,1 (CSInST, n=0,1)     | 9-6  |  |

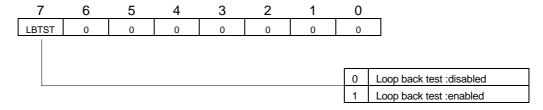

|      | 9.2.4             | CSI Test Control Register (CSTSCON)          | 9-7  |  |

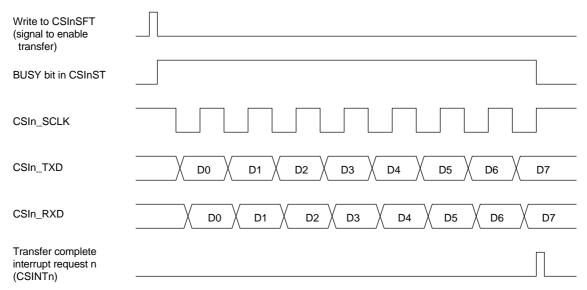

| 9.3  | Clock S           | Synchronous Serial Interface (CSI) Operation | 9-8  |  |

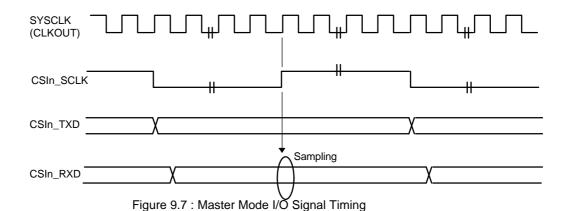

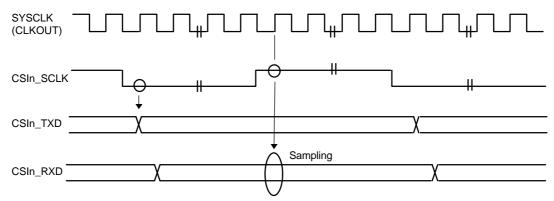

| 9.4  | I/O Sigr          | nal Timing                                   | 9-10 |  |

|      | 9.4.1             | Master Mode I/O Signal Timing                | 9-10 |  |

|      | 9.4.2             | Slave Mode I/O Signal Timing                 | 9-11 |  |

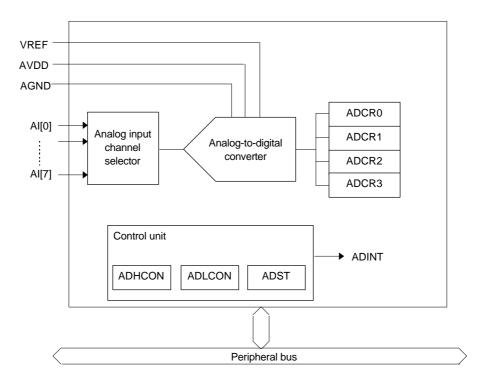

| 10   | Analog            | g-to-Digital Converter                       | 10-1 |  |

| 10.1 | Overvie           |                                              | 10-2 |  |

| 10.1 | 10.1.1            | Block Diagram                                | 10-2 |  |

|      | 10.1.1            | Pins                                         | 10-4 |  |

|      | 10.1.2            | r iiio                                       | 10-4 |  |

|       | 10.1.3   | Control Registers                                     | 10-4  |

|-------|----------|-------------------------------------------------------|-------|

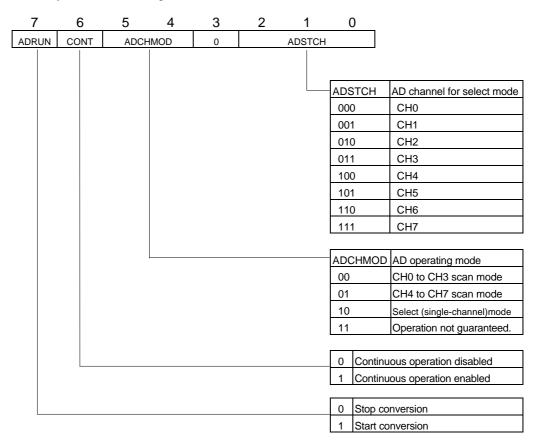

| 10.2  | Control  | Registers                                             | 10-5  |

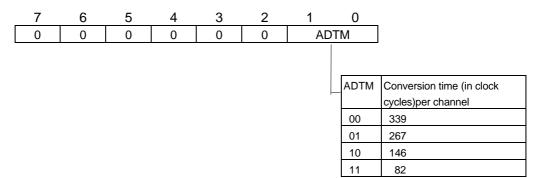

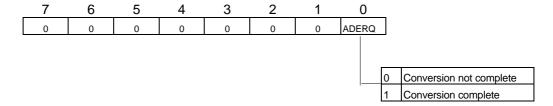

|       | 10.2.1   | AD Control Register H (ADHCON)                        | 10-5  |

|       | 10.2.2   | AD Control Register L (ADLCON)                        | 10-7  |

|       | 10.2.3   | AD Status Register (ADST)                             | 10-8  |

|       | 10.2.4   | AD Result Registers 0 to 3 (ADCRn, n=0 - 3)           | 10-9  |

| 10.3  | Analog-t | to-Digital Converter (ADC) Operation                  | 10-10 |

| 11    | Externa  | al Memory Controller                                  | 11-1  |

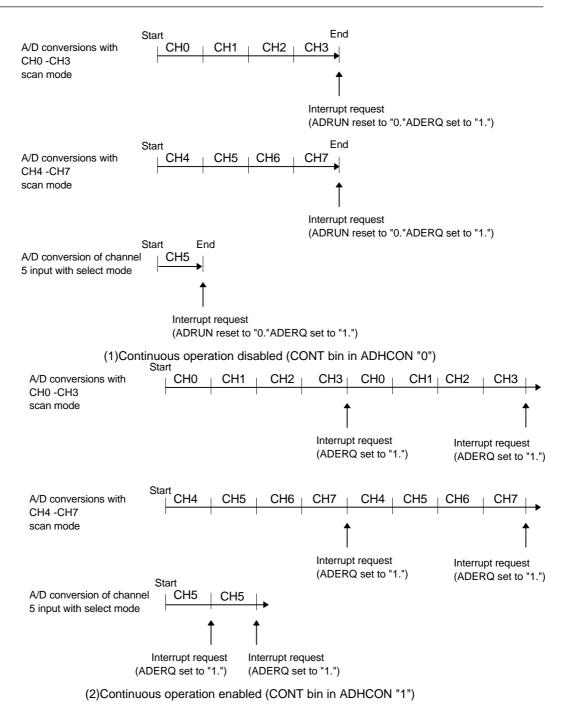

| 11. 1 | Overvie  | w                                                     | 11-2  |

|       | 11.1.1   | Block Diagram                                         | 11-3  |

|       | 11.1.2   | Pins                                                  | 11-5  |

|       | 11.1.3   | Control Registers                                     | 11-6  |

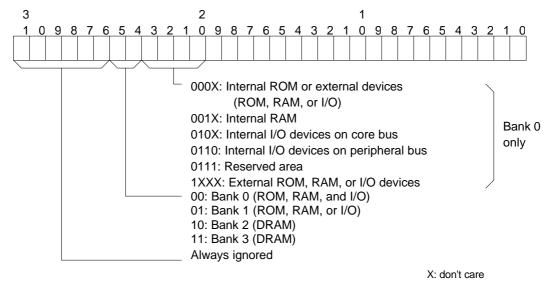

|       | 11.1.4   | Address Spaces                                        | 11-7  |

| 11.2  | Control  | Registers                                             | 11-9  |

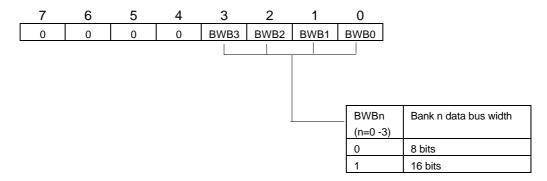

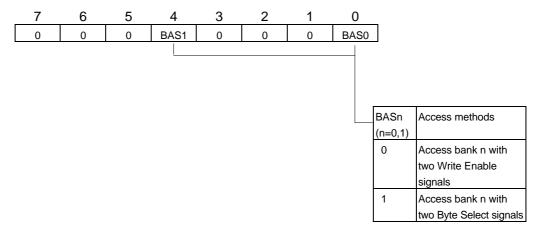

|       | 11.2.1   | Bus Width Control Register (BWCON)                    | 11-9  |

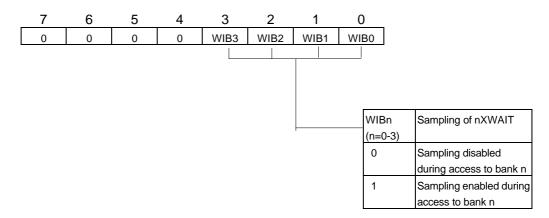

|       | 11.2.2   | Wait Input Control Register (WICON)                   | 11-10 |

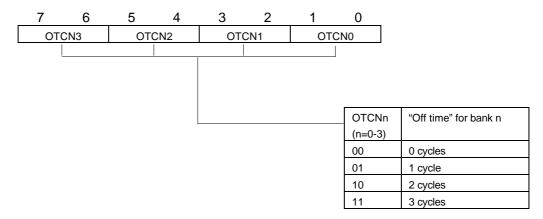

|       | 11.2.3   | Off Time Control Register (OTCON)                     | 11-11 |

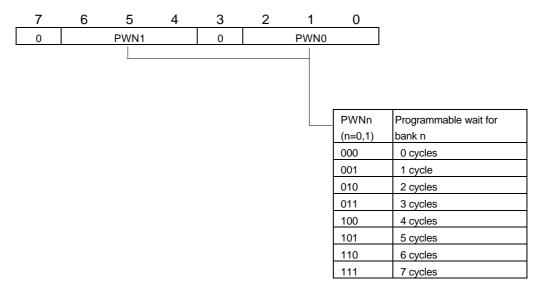

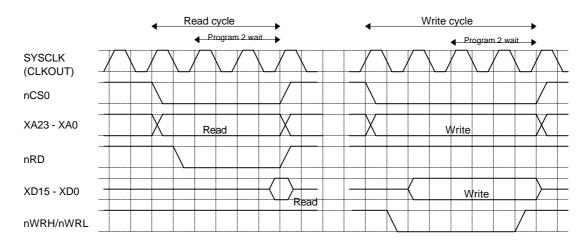

|       | 11.2.4   | Programmable Wait Control Register (PWCON)            | 11-12 |

|       | 11.2.5   | Bus Access Control Register (BACON)                   | 11-13 |

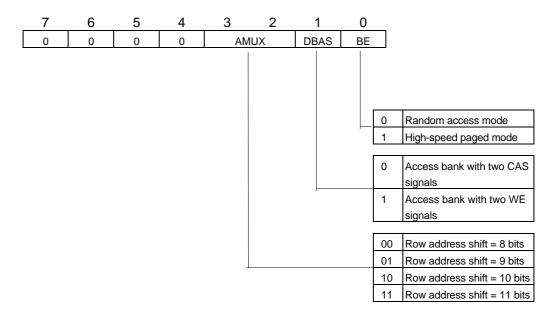

|       | 11.2.6   | DRAM Bank 2 and 3 Control Registers (DRnCON, n=2,3)   | 11-14 |

|       | 11.2.7   | DRAM Bank 2 and 3 Access Timing Control Registers     |       |

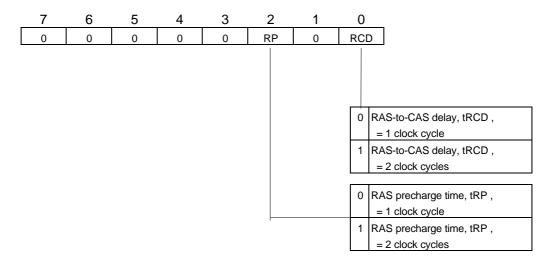

|       |          | (ATnCON, n=2,3)                                       | 11-15 |

|       | 11.2.8   | DRAM Bank 2 and 3 Programmable Wait Control Registers |       |

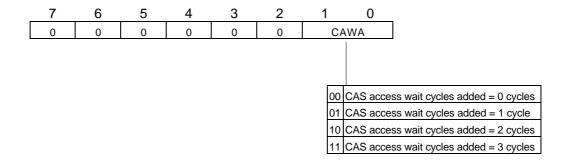

|       |          | (DWnCON, n=2,3)                                       | 11-16 |

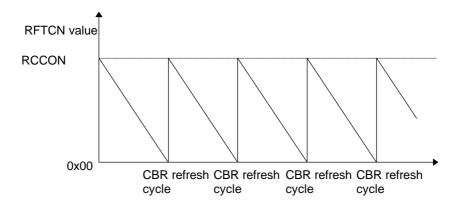

|       | 11.2.9   | Refresh Timer Counter (RFTCN)                         | 11-17 |

|       | 11.2.10  | Refresh Cycle Control Register (RCCON)                | 11-17 |

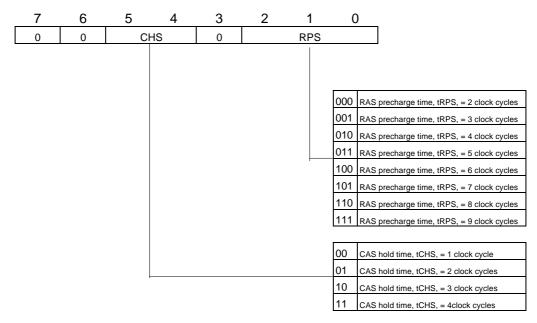

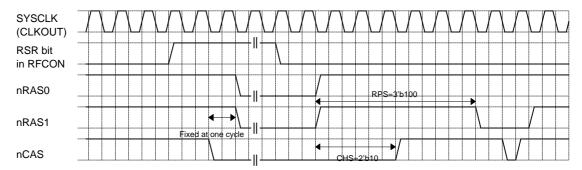

|       | 11.2.11  | Refresh Timing Control Register (RTCON)               | 11-18 |

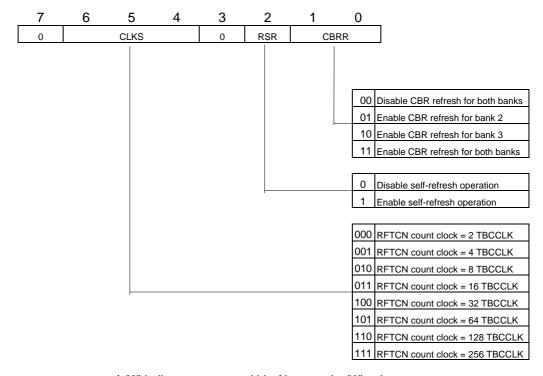

|       | 11.2.12  | Refresh Control Register (RFCON)                      | 11-19 |

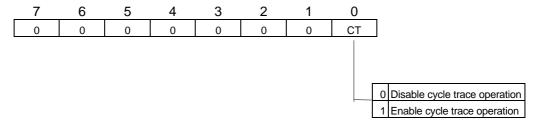

|       | 11.2.13  | Cycle Trace Control Register (CTCON)                  | 11-21 |

| 11.3  | Address  | Space Access                                          | 11-22 |

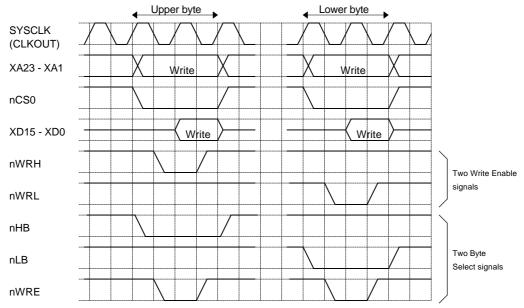

|       | 11.3.1   | Data Bus Width                                        | 11-23 |

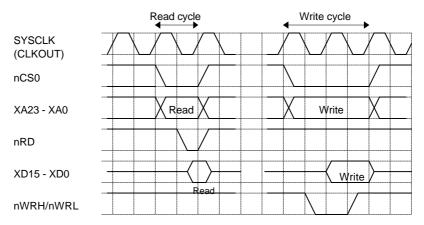

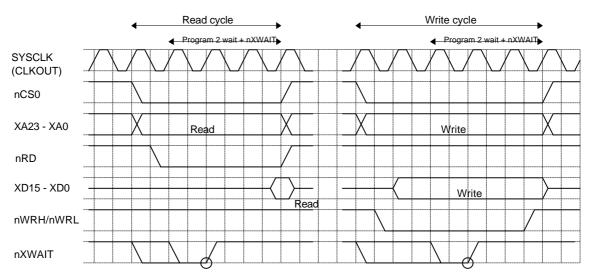

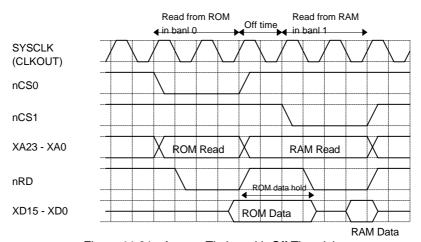

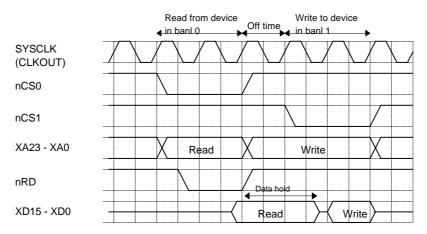

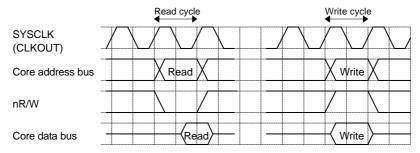

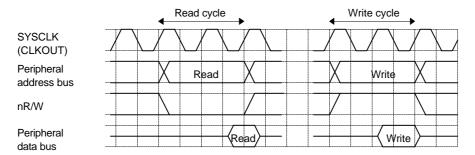

|       | 11.3.2   | Accessing External Memory in SRAM Banks (0 and 1)     | 11-24 |

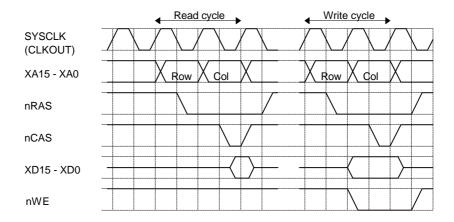

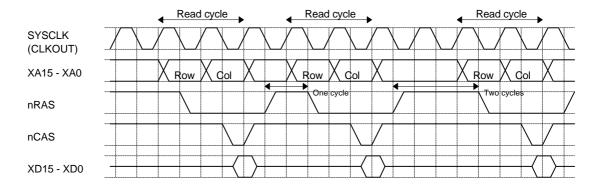

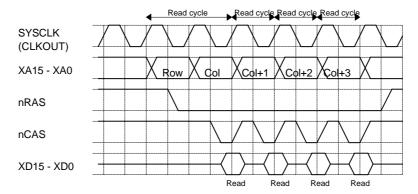

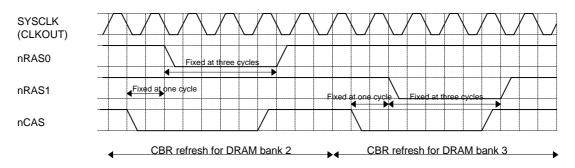

|       | 11.3.3   | Accessing External Memory in DRAM Banks (2 and 3)     | 11-27 |

|      | 11.3.4  | External Access Functions Common to All Banks | 11-36 |

|------|---------|-----------------------------------------------|-------|

|      | 11.3.5  | Accessing Bank 0 Internal Memory Areas        | 11-38 |

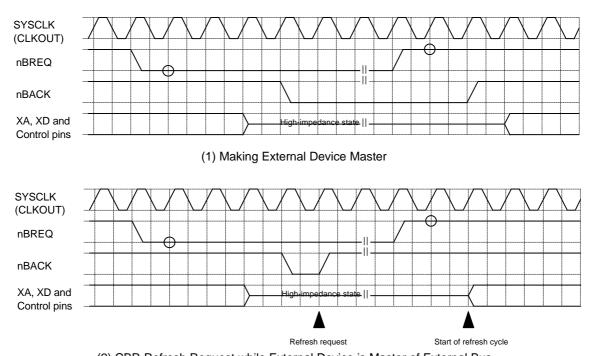

| 11.4 | Bus Ark | pitration                                     | 11-39 |

|      | 11.4.1  | Bus Access and Priority                       | 11-39 |

|      | 11.4.2  | Requesting and Obtaining Bus Access           | 11-39 |

|      | 11.4.3  | Lock Operation                                | 11-40 |

| 11.5 | Standb  | y Operation                                   | 11-41 |

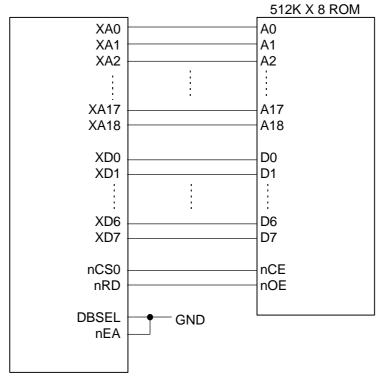

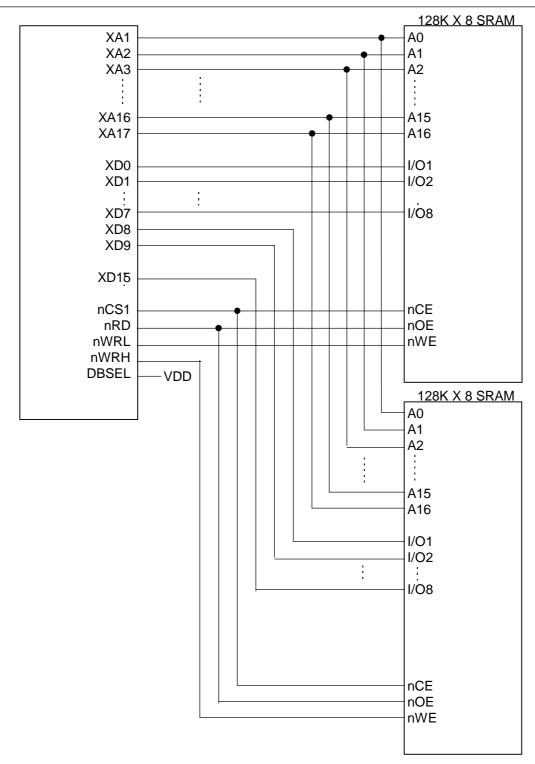

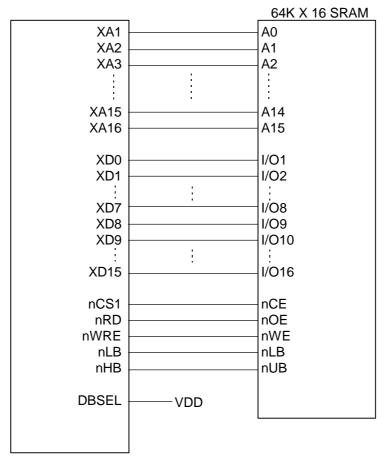

| 11.6 | Connec  | cting External Memory                         | 11-42 |

|      | 11.6.1  | Connecting ROM                                | 11-42 |

|      | 11.6.2  | Connecting SRAM                               | 11-44 |

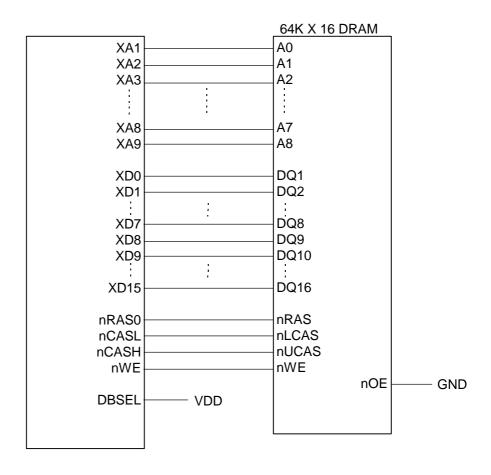

|      | 11.6.3  | Connecting DRAM                               | 11-47 |

## 1 Overview

| 1.1 | Feature | es                                   | 1-2  |

|-----|---------|--------------------------------------|------|

| 1.2 | Block [ | Diagram                              | 1-4  |

| 1.3 | Pins    |                                      | 1-5  |

|     | 1.3.1   | Pin Layout                           | 1-5  |

|     | 1.3.2   | Pin Functions                        | 1-6  |

|     | 1.3.3   | Treatment of Unused Pins             | 1-10 |

|     | 1.3.4   | Configurations of Pins and I/O ports | 1-11 |

1-1

### 1.1 Features

ML670100 is a high-performance 32-bit microcontroller combining a RISC-based, 32-bit CPU core - the ARM7TDMI developed by ARM Limited - with memory (ROM and RAM) and such peripheral circuits as timers, serial ports, and an analog-to-digital converter. This combination of 32-bit data processing, built-in memory, and on-chip peripherals make it ideal for controlling equipment requiring both high speed and high functionality. An external memory controller supports direct connection to memory (SRAM, DRAM, etc.) and peripheral devices for adding even more functionality.

The following is a list of features.

#### • CPU

- RISC-based, 32-bit CPU core (ARM7TDMI)

- Two instruction sets

The programmer can freely switch between a 32-bit instruction set deriving maximum performance and a 16-bit instruction set providing minimal code size.

- General-purpose registers: 32 bits x 29

- Built-in multiplier

#### On-chip memory

ROM: 128 kilobytesRAM: 4 kilobytes

### Standby function

- HALT mode

### • Port functions

- I/O ports: 8 bits x 9

I/O directions are specified at the bit level.

- Analog input port: 8 bits x 1

## Clock generator

- Built-in crystal oscillator circuit

- Built-in phase-locked loop for generating operating clock frequencies double or quadruple the crystal oscillator frequency

- Choice of multipliers (1/1, 1/2, and 1/4) for adjusting operating clock frequency to match load of processing

### • Time Base Generator (TBG)

- Time base clock signals for on-chip peripherals

- Built-in Watchdog Timer (WDT)

### • Flexible Timer (FTM)

- 16-bit timer with 6 channels

- Choice of operating modes: auto-reload timer (ART), compare out (CMO), pulse width modulation (PWM), and capture (CAP)

### Serial ports

- One asynchronous serial port (UART) with built-in baud rate generator

- Two clock synchronous serial ports

## Analog-to-digital converter

- 8-bit resolution

- Analog input port with eight channels

## • Interrupt controller

- Support for 28 sources: 9 external and 19 internal

- Choice of eight priority levels for each source

## • External memory controller

- Direct connection to ROM, SRAM, DRAM, and peripheral devices

- Support for four banks: two for ROM, SRAM, and I/O devices plus two for DRAM

- User-configurable wait control and other parameters for accessing memory and other external devices

## Package

- 144-pin LQFP (LQFP144-P-2020-0.50-K)

1-3

## 1.2 Block Diagram

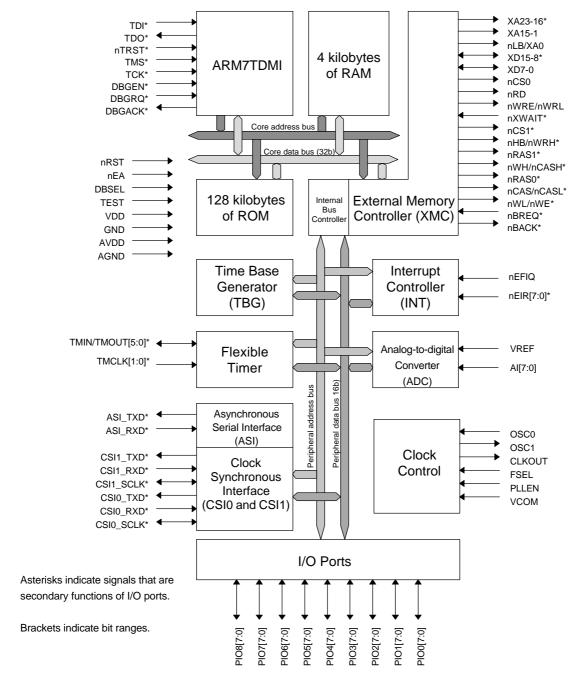

Figure 1-1 gives a block diagram for this LSI.

Figure 1-1: Block Diagram

## 1.3 Pins

## 1.3.1 Pin Layout

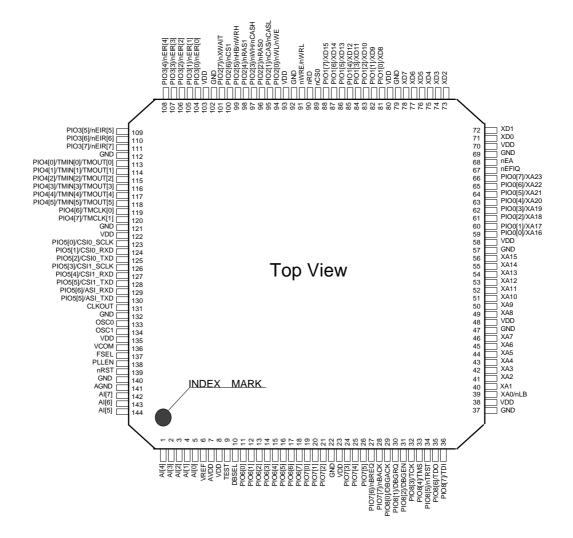

Figure 1-2 gives the pin layout for this LSI.

- Directly connect all VDD pins to external power supplies and ground all VSS pins.

- AVDD, AGND, and VREF are the power supply, ground, and reference voltage pins for the analog-to-digital converter (ADC).

Connect AVDD and VREF to VDD and AGND to VSS.

Figure 1-2: Pin Layout

1-5

## 1.3.2 Pin Functions

Table 1.1 lists the functions of each pin.

Table 1.1 : Pin Functions

| Туре               | Signal Name |                | I/O Direction  | Description                                                                                                                                 |

|--------------------|-------------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Address            | XA23-XA16   | 66-59          | Output         | These are bits 23 - 16 of the external address bus. They represent secondary functions for I/O port PIO0[7:0].                              |

|                    | XA15-XA0    | 56-49<br>46-39 | Output         | These are bits 15 - 0 of the external address bus.                                                                                          |

| Data bus           | XD15-XD8    | 88-81          | Bi-directional | These are bits 15 - 8 of the external data bus. They represent secondary functions for I/O port PIO1[7:0].                                  |

|                    | XD7-XD0     | 78-71          | Bi-directional | These are bits 7 - 0 of the external data bus.                                                                                              |

| Bus                | nCS0        | 89             | Output         | This output is the chip select signal for bank 0.                                                                                           |

| control<br>signals | nCS1        | 100            | Output         | This output is the chip select signal for bank 1. It represents a secondary function for I/O port PIO2[6].                                  |

| 8                  | nRD         | 90             | Output         | This output is the read signal for the SRAM banks (0 and 1).                                                                                |

|                    | nWRL        | 91             | Output         | This output is the Write Enable Low signal for the SRAM banks (0 and 1).                                                                    |

|                    | nWRH        | 99             | Output         | This output is the Write Enable High signal for the SRAM banks (0 and 1). It represents a secondary function for I/O port PIO2[5].          |

|                    | nWRE        | 91             | Output         | This output is the Write Enable signal for the SRAM banks (0 and 1).                                                                        |

|                    | nLB         | 39             | Output         | This output is the Low Byte Select signal for the SRAM banks (0 and 1).                                                                     |

|                    | nHB         | 99             | Output         | This output is the High Byte Select signal for the SRAM banks (0 and 1). It represents a secondary function for I/O port PIO2[5].           |

|                    | nRAS0       | 96             | Output         | This output is the Row Address Strobe signal for bank 2. It represents a secondary function for I/O port PIO2[2].                           |

|                    | nRAS1       | 98             | Output         | This output is the Row Address Strobe signal for bank 3. It represents a secondary function for I/O port PIO2[4].                           |

|                    | nCASL       | 95             | Output         | This output is the Column Address Strobe Low signal for the DRAM banks (2 and 3). It represents a secondary function for I/O port PIO2[1].  |

|                    | nCASH       | 97             | Output         | This output is the Column Address Strobe High signal for the DRAM banks (2 and 3). It represents a secondary function for I/O port PIO2[3]. |

|                    | nWE         | 94             | Output         | This output is the Write Enable signal for the DRAM banks (2 and 3). It represents a secondary function for I/O port PIO2[0].               |

Table 1.1 : Pin Functions

| Type                      | Signal Name | Pin<br>Number | I/O Direction | Description                                                                                                                                                                                     |

|---------------------------|-------------|---------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus<br>control<br>signals | nCAS        | 95            | Output        | This output is the Column Address Strobe signal for the DRAM banks (2 and 3). It represents a secondary function for I/O port PIO2[1].                                                          |

| Signais                   | nWH         | 97            | Output        | This output is the Write Enable High signal for the DRAM banks (2 and 3). It represents a secondary function for I/O port PIO2[3].                                                              |

|                           | nWL         | 94            | Output        | This output is the Write Enable Low signal for the DRAM banks (2 and 3). It represents a secondary function for I/O port PIO2[0].                                                               |

|                           | nXWAIT      | 101           | Input         | This input pin controls insertion of wait cycles. It represents a secondary function for I/O port PIO2[7].                                                                                      |

|                           | nBREQ       | 27            | Input         | This input is a bus request signal from an external device. It represents a secondary function for I/O port PIO7[6].                                                                            |

|                           | nBACK       | 28            | Output        | This output is an acknowledgment signal to a bus request signal from an external device. It represents a secondary function for I/O port PIO7[7].                                               |

| Interrupts                | nEFIQ       | 67            | Input         | This input is an external fast interrupt request (FIQ). When accepted, the request is processed as an FIQ exception.                                                                            |

|                           | nEIR[7:0]   | 111-104       | Input         | These inputs are external interrupt requests. They represent secondary functions for I/O port PIO3[7:0].                                                                                        |

| Timers                    | TMIN[5:0]   | 118-113       | Input         | These pins function as capture trigger input pins for Flexible Timer (FTM) channels 5 - 0 in capture (CAP) mode. They represent secondary functions for I/O port PIO4[5:0].                     |

|                           | TMOUT[5:0]  | 118-113       | Output        | These pins function as output pins for Flexible Timer(FTM) channels 5 - 0 in compare out (CMO) or pulse width modulation (PWM) mode. They represent secondary functions for I/O port PIO4[5:0]. |

|                           | TMCLK[1:0]  | 120,119       | Input         | These pins function as Flexible Timer (FTM) channel 1 and 0 clock input pins. They represent secondary functions for I/O port PIO4[7:6].                                                        |

| Serial<br>ports           | ASI_TXD     | 130           | Output        | This output is the transmit data for the Asynchronous Serial Interface (ASI). It represents a secondary function for I/O port PIO5[7].                                                          |

|                           | ASI_RXD     | 129           | Input         | This input is the receive data for the Asynchronous Serial Interface (ASI). It represents a secondary function for I/O port PIO5[6].                                                            |

|                           | CSI0_TXD    | 125           | Output        | This output is the transmit data for the Clock Synchronous Interface 0(CSI0). It represents a secondary function for I/O port PIO5[2].                                                          |

|                           | CSI0_RXD    | 124           | Input         | This input is the receive data for the Clock Synchronous Interface 0 (CSI0). It represents a secondary function for I/O port PIO5[1].                                                           |

Table 1.1 : Pin Functions

| Type       | : Pin Function Signal Name |         | I/O Direction  | Description                                                    |

|------------|----------------------------|---------|----------------|----------------------------------------------------------------|

| Турс       | Oignai i vaine             | Number  | I/O Bircotion  | Description                                                    |

| Serial     | CSI0_SCLK                  | 123     | Bi-directional | This pin accepts/provides the clock signal for the Clock       |

| ports      |                            |         |                | Synchronous Interface 0 (CSI0). It represents a secondary      |

|            |                            |         |                | function for I/O port PIO5[0].                                 |

|            | CSI1_TXD                   | 128     | Output         | This output is the transmit data for the Clock Synchronous     |

|            |                            |         |                | Interface 1 (CSI1). It represents a secondary function for I/O |

|            |                            |         |                | port PIO5[5].                                                  |

|            | CSI1_RXD                   | 127     | Input          | This input is the receive data for the Clock Synchronous       |

|            |                            |         |                | Interface 1 (CSI1). It represents a secondary function for I/O |

|            |                            |         |                | port PIO5[4].                                                  |

|            | CSI1_SCLK                  | 126     | Bi-directional | This pin accepts/provides the clock signal for the Clock       |

|            |                            |         |                | Synchronous Interface 1 (CSI1). It represents a secondary      |

|            |                            |         |                | function for I/O port PIO5[3].                                 |

| Analog-to- | VREF                       | 6       | Input          | This input is the reference voltage for the analog-to-digital  |

| digital    |                            |         |                | converter. Connect it to V DD.                                 |

| converter  | AI[7:0]                    | 142-144 | Input          | These are analog signal input pins for analog-to-digital       |

|            |                            | 1-5     |                | converter channels 7 - 0.                                      |

| Debugging  | TDI                        | 36      | Input          | This input is the serial data input for the debugging scan     |

| interface  |                            |         |                | circuit. It represents the secondary function for I/Oport      |

|            |                            |         |                | PIO8[7].                                                       |

|            | TDO                        | 35      | Output         | This output is the serial data output for the debugging scan   |

|            |                            |         |                | circuit. It represents the secondary function for I/O port     |

|            |                            |         |                | PIO8[6].                                                       |

|            | nTRST                      | 34      | Input          | "L" level input to this pin resets the debugging scan circuit. |

|            |                            |         |                | It represents the secondary function for I/O port PIO8[5].     |

|            | TMS                        | 33      | Input          | This input selects the mode for the debugging scan circuit. It |

|            |                            |         |                | represents the secondary function for I/O port PIO8[4].        |

|            | TCK                        | 32      | Input          | This input is the serial clock input for the debugging scan    |

|            |                            |         |                | circuit. It represents the secondary function for I/O port     |

|            |                            |         |                | PIO8[3].                                                       |

|            | DBGEN                      | 31      | Input          | "High" level input to this pin enables the CPU's debugging     |

|            |                            |         |                | function. It represents the secondary function for I/O port    |

|            |                            |         |                | PIO8[2].                                                       |

|            | DBGRQ                      | 30      | Input          | This input is a debugging request signal from an external      |

|            |                            |         |                | device. It represents the secondary function for I/O port      |

|            |                            |         |                | PIO8[1].                                                       |

|            | DBGACK                     | 29      | Output         | This output is an acknowledgment signal to a debugging         |

|            |                            |         |                | request signal from an external device. It represents the      |

|            |                            |         |                | secondary function for I/O port PIO8[0].                       |

Table 1.1 : Pin Functions

|                  | Table 1.1 : Pin Functions |                |                |                                                                                                                                                                                          |  |  |

|------------------|---------------------------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Туре             | Signal Name               | Pin<br>Number  | I/O Direction  | Description                                                                                                                                                                              |  |  |

| I/O ports        | PIO8[7:0]                 | 36-29          | Bi-directional | These form an 8-bit I/O port. I/O directions are specified at the bit level.                                                                                                             |  |  |

|                  | PIO7[7:0]                 | 28-24<br>21-19 | Bi-directional | These form an 8-bit I/O port. I/O directions are specified at the bit level.                                                                                                             |  |  |

|                  | PIO6[7:0]                 | 18-11          | Bi-directional | These form an 8-bit I/O port. I/O directions are specified at the bit level.                                                                                                             |  |  |

|                  | PIO5[7:0]                 | 130-123        | Bi-directional | These form an 8-bit I/O port. I/O directions are specified at the bit level.                                                                                                             |  |  |

|                  | PIO4[7:0]                 | 120-113        | Bi-directional | These form an 8-bit I/O port. I/O directions are specified at the bit level.                                                                                                             |  |  |

|                  | PIO3[7:0]                 | 111-104        | Bi-directional | These form an 8-bit I/O port. I/O directions are specified at the bit level.                                                                                                             |  |  |

|                  | PIO2[7:0]                 | 101-94         | Bi-directional | These form an 8-bit I/O port. I/O directions are specified at the bit level.                                                                                                             |  |  |

|                  | PIO1[7:0]                 | 88-81          | Bi-directional | These form an 8-bit I/O port. I/O directions are specified at the bit level.                                                                                                             |  |  |

|                  | PIO0[7:0]                 | 66-59          | Bi-directional | These form an 8-bit I/O port. I/O directions are specified at the bit level.                                                                                                             |  |  |

| Clock<br>control | OSC0                      | 133            | Input          | This pin is for connecting a crystal oscillator. If an external clock is used, supply it to this pin.                                                                                    |  |  |

|                  | OSC1                      | 134            | Output         | This pin is for connecting a crystal oscillator. If an external clock is used, leave this pin open.                                                                                      |  |  |

|                  | CLKOUT                    | 131            | Output         | This output is the internal system clock (SYSCLK) signal.                                                                                                                                |  |  |

|                  | FSEL                      | 137            | Input          | Connect this pin to VDD or ground to indicate the frequency range for the basic clock.                                                                                                   |  |  |

|                  | PLLEN                     | 138            | Input          | Connecting this pin to VDD enables the built-in phase-locked loop. If the PLL is not used because an external clock with a guaranteed duty is available, connect this pin to ground.     |  |  |

|                  | VCOM                      | 136            | Input          | This input controls the oscillation frequency of the PLL's voltage-controlled oscillator. Connect it to ground.                                                                          |  |  |

| System control   | nRST                      | 139            | Input          | "L" level input to this pin produces an external system reset for this LSI. "H" level input then causes execution to resume from address 0x000000.                                       |  |  |

|                  | DBSEL                     | 10             | Input          | During a system reset of this LSI, this input specifies the width of the external data bus for bank 0. Connect this pin to VDD for a data bus width of 16 bits and to ground for 8 bits. |  |  |

|                  | nEA                       | 68             | Input          | During a system reset of this LSI, this input controls the use of the internal ROM. Connect this pin to VDD to enable the ROM and to ground to disable it                                |  |  |

Table 1.1 : Pin Functions

| Type           | Signal Name | Pin<br>Number                                            | I/O Direction | Description                                                                                                                                                                                                                                      |

|----------------|-------------|----------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System control | TEST        | 9                                                        | Input         | During a system reset of this LSI, this input controls the initial pin functions for the I/O port 8 pins (PIO8[7:0]). Connect this pin to VDD to initialize the port for its secondary function, the debugging interface, and to ground for I/O. |

| Power supply   | VDD         | 8,23,38,<br>48,58,70,<br>80,93,<br>103,122,<br>135       | Input         | These pins are this LSI's power supply pins. Connect them all to $\ensuremath{VDD}$ .                                                                                                                                                            |

|                | GND         | 22,37,47,<br>57,69,79,<br>92,102,<br>112,121,<br>132,140 | Input         | These pins are this LSI's ground pins. Connect them all to ground.                                                                                                                                                                               |

|                | AVDD        | 7                                                        | Input         | This pin is the analog-to-digital converter's power supply. Connect it to VDD.                                                                                                                                                                   |

|                | AGND        | 141                                                      | Input         | This pin is the analog-to-digital converter's ground pin.  Connect it to ground.                                                                                                                                                                 |

## 1.3.3 Treatment of Unused Pins

Table 1.2 lists the connections for unused pins.

Table 1.2 : Treatment of Unused Pins

| Table 1.2. Healtheth of Officed Fills |                                                                  |  |  |  |

|---------------------------------------|------------------------------------------------------------------|--|--|--|

| Pin Name(s)                           | Treatment                                                        |  |  |  |

| PIO8-PIO0                             | Input configuration: Connect to VDD or ground through resistors. |  |  |  |

|                                       | Output configuration: Leave open.                                |  |  |  |

| nEFIQ                                 | Connect to VDD.                                                  |  |  |  |

| VREF                                  | Connect to VDD.                                                  |  |  |  |

| AI [7:0]                              | 7:0] Connect to VDD or ground.                                   |  |  |  |

| TEST                                  | Connect to VDD or ground.                                        |  |  |  |

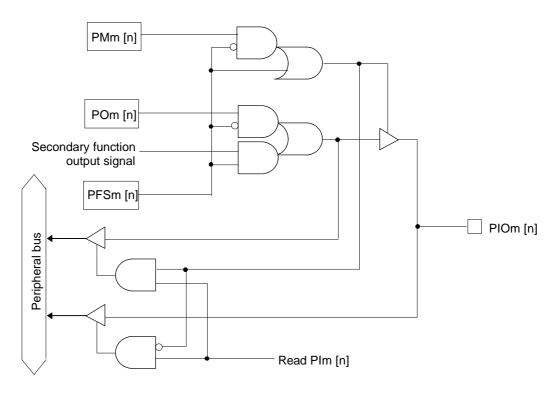

## 1.3.4 Configurations of Pins and I/O ports

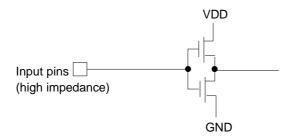

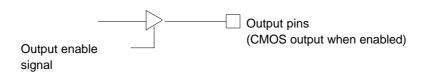

(1) Input Pins (nRST, nEA, DBSEL, TEST, nEFIQ, FSEL, PLLEN, VCOM)

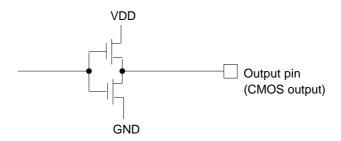

(2) Output Pin (CLKOUT)

(3) Tri-state output pins (XA23 - XA1, nLB/XA0, nCS0, nRD, nWRE/nWRL)

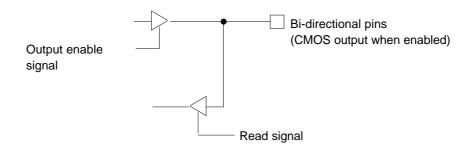

(4) Bi-directional pins (XD7 - XD0)

## (5) I/O port A (I/O ports without secondary functions) PIO6[7:0], PIO7[5:0]

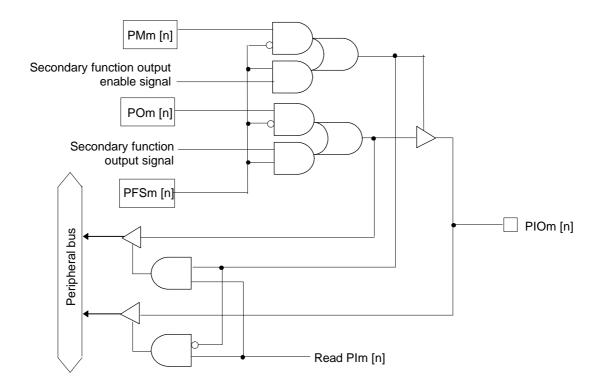

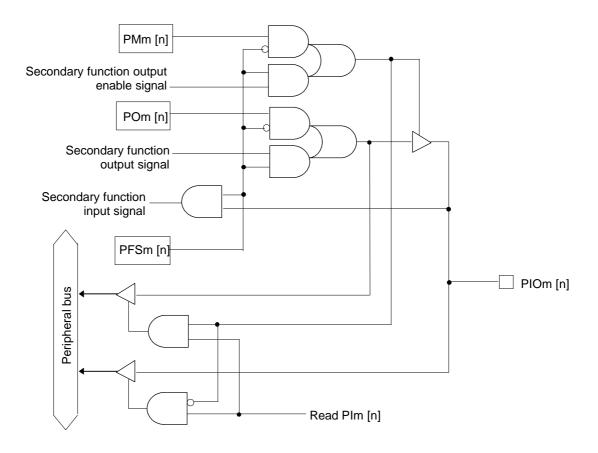

(6) I/O port B (I/O ports with secondary functions of input)

PIO2[7], PIO3[7:0], PIO4[7:6], PIO5[6], PIO5[4], PIO5[1], PIO7[6], PIO8[7], PIO8[5:1]

## (7) I/O port C (I/O ports with secondary functions of output) PIO5[7], PIO5[5], PIO5[2], PIO7[7], PIO8[6], PIO8[0]

## (8) I/O port D (I/O ports with secondary functions of tri-state output) PIO0[7:0], PIO2[6:0]

## (9) I/O port E (I/O ports with secondary functions of input and output) PIO1[7:0], PIO4[5:0], PIO5[3], PIO5[0]

## 2 CPU

This LSI uses as its CPU the ARM7TDMI core developed by ARM Limited. This CPU offers the programmer a choice of two states: ARM state, executing 32-bit ARM instructions, and THUMB state, executing 16-bit THUMB instructions, a subset of ARM instructions.

| 2.1  | CPU O           | perating States                                        | 2-2  |  |

|------|-----------------|--------------------------------------------------------|------|--|

| 2.2  | Switchi         | hing State                                             |      |  |

| 2.3  | Memor           | Memory Formats                                         |      |  |

| 2.4  | Instruct        | Instruction Length                                     |      |  |

| 2.5  | Data T          | Data Types                                             |      |  |

| 2.6  | Operating Modes |                                                        | 2-3  |  |

| 2.7  | Registe         | ers                                                    | 2-3  |  |

|      | 2.7.1           | The ARM state register set                             | 2-4  |  |

|      | 2.7.2           | The THUMB state register set                           | 2-6  |  |

|      | 2.7.3           | The relationship between ARM and THUMB state registers | 2-7  |  |

|      | 2.7.4           | Accessing Hi registers in THUMB state                  | 2-7  |  |

| 2.8  | The Pro         | ogram Status Registers                                 | 2-8  |  |

|      | 2.8.1           | The condition code flags                               | 2-8  |  |

|      | 2.8.2           | The control bits                                       | 2-8  |  |

| 2.9  | Except          | ions                                                   | 2-9  |  |

|      | 2.9.1           | Action on entering an exception                        | 2-10 |  |

|      | 2.9.2           | Action on leaving an exception                         | 2-10 |  |

|      | 2.9.3           | Exception entry/exit summary                           | 2-10 |  |

|      | 2.9.4           | FIQ                                                    | 2-11 |  |

|      | 2.9.5           | IRQ                                                    | 2-11 |  |

|      | 2.9.6           | Software interrupt                                     | 2-12 |  |

|      | 2.9.7           | Undefined instruction                                  | 2-12 |  |

|      | 2.9.8           | Exception vectors                                      | 2-12 |  |

|      | 2.9.9           | Exception priorities                                   | 2-13 |  |

| 2.10 | Reset           |                                                        | 2-13 |  |

2-1

## 2.1 CPU Operating States

From the programmer's point of view, the CPU can be in one of two states:

ARM state which executes 32-bit, word-aligned ARM instructions.

THUMB state which operates with 16-bit, halfword-aligned THUMB instructions. In this

state, the PC uses bit 1 to select between alternate halfwords.

Note: Transition between these two states does not affect the CPU mode or the contents of

the registers.

## 2.2 Switching State

### **Entering THUMB state**

Entry into THUMB state can be achieved by executing a BX instruction with the state bit (bit 0) set in the operand register.

Transition to THUMB state will also occur automatically on return from an exception(IRQ, FIQ, UNDEF, SWI etc.), if the exception was entered with the processor in THUMB state.

#### **Entering ARM state**

Entry into ARM state happens:

- 1 On execution of the BX instruction with the state bit clear in the operand register.

- 2 On the processor taking an exception (IRQ, FIQ, RESET, UNDEF, SWI etc.). In this case, the PC is placed in the exception mode's link register, and execution commences at the exception's vector address.

## 2.3 Memory Formats

The CPU views memory as a linear collection of bytes numbered upwards from zero. Bytes 0 to 3 hold the first stored word, bytes 4 to 7 the second and so on. The CPU can treat words in memory as being stored in Little Endian format.

**Note:** The core architecture supports both big- and little- endian formats, but this LSI uses only the latter.

| 31 2 | 24 23 | 16 15 | 8 7 | 0 | Word Address |

|------|-------|-------|-----|---|--------------|

| 11   | 10    | 9     | 8   |   | 8            |

| 7    | 6     | 5     | 4   |   | 4            |

| 3    | 2     | 1     | 0   |   | 0            |

- -Least significant byte is at lowest address

- -Word is addressed by byte address of least significant byte

Figure 2.1: Little endian addresses of bytes within words

## 2.4 Instruction Length

Instructions are either 32 bits long (in ARM state) or 16 bit long (in THUMB state).

## 2.5 Data Types

The CPU supports byte (8-bit), halfword (16-bit) and word (32-bit) data types. Words must be aligned to four-byte boundaries and half words to two-byte boundaries.

## 2.6 Operating Modes

The CPU supports six modes of operation:

User (usr): The normal ARM program execution state

FIQ(fiq): Designed to support a data transfer or channel process

IRQ(irq): Used for general-purpose interrupt handling Supervisor (sys): Protected mode for the operating system.

System (sys): A privileged user mode for the operating system

Undefined(und): Entered when an undefined instruction is executed

**Note :** The core architecture offers an additional mode, Abort mode, but this LSI does

not use it.

Mode changes may be made under software control, or may be brought about by interrupts or exception processing. Most application programs will execute in User mode.

The non-user modes -known as privileged modes- are entered in order to service interrupts or exceptions, or to access protected resources.

## 2.7 Registers

The CPU has a total of 34 registers -29 general-purpose 32-bit registers and five status registers- but these cannot all be seen at once. The CPU state and operating mode dictate which registers are available to the programmer.

**Note:** The core architecture offers an additional two general-purpose registers and one status register for use with the Abort mode, which this LSI does not support.

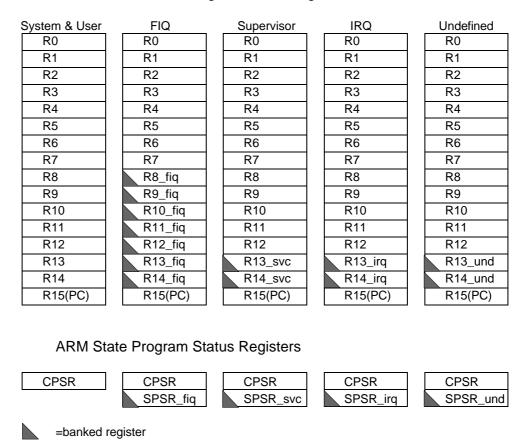

## 2.7.1 The ARM state register set

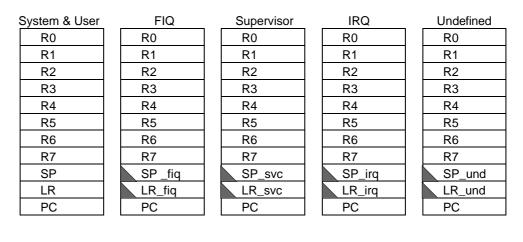

In ARM state, 16 general registers and one or two status registers are visible at any one time. In privileged (non-User) modes, mode-specific banked registers are switched in.

Figure 2.2: Register organization in ARM state shows which registers are available in each mode: the banked registers are marked with a shaded triangle.

The ARM state register set contains 16 directly accessible registers: R0 to R15. All of these except R15 are general-purpose, and may be used to hold either data or address values. In addition to these, there is a seventeenth register used to store status information.

Register 14 is used as the subroutine link register. This receives a copy of R15 when a Branch and Link (BL) instruction is executed. At all other times it may be treated as a general-purpose register. The corresponding banked registers R14\_svc, R14\_irg, R14\_fiq, and R14\_und are similarly used to hold the return values of R15 when interrupts and exceptions arise, or when Branch and Link instructions are executed within interrupt or exception routines.

Register 15 holds the Program Counter (PC). In ARM state, bits [1:0] of R15 are zero and bits [31:2] contain the PC. In THUMB state, bit [0] is zero and bits [31:1] contain the PC.

Register 16 is the CPSR (Current Program Status Register). This contains condition code flags and the current mode bits.

FIQ mode has seven banked registers mapped to R8-14 (R8\_fiq-R14\_fiq). In ARM state, many FIQ handlers do not need to save any registers. User, IRQ, Supervisor and Undefined each have two banked registers mapped to R13 and R14, allowing each of these modes to have a private stack pointer and link registers.

2-4

## ARM State General Registers and Program Counter

Figure 2.2 : Register organization in ARM state

## 2.7.2 The THUMB state register set

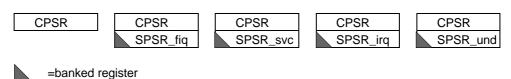

The THUMB state register set is a subset of the ARM state set. The programmer has direct access to eight general registers, R0-R7, as well as the Program Counter (PC), a stack pointer register (SP), a link register (LR), and the CPSR. There are banked Stack Pointers, Link Registers and Saved Program Status Registers (SPSRs) for each privileged mode. This is shown in Figure 2.3: Register organization in THUMB state.

## THUMB State General Registers and Program Counter

## **THUMB State Program Status Registers**

Figure 2.3: Register organization in THUMB state

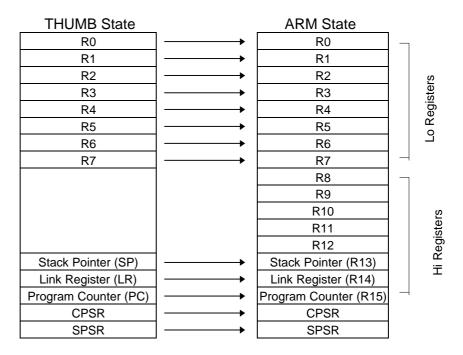

## 2.7.3 The relationship between ARM and THUMB state registers

The THUMB state registers relate to the ARM state registers in the following way:

- THUMB state R0-R7 and ARM state R0-R7 are identical

- THUMB state CPSR and SPSRs and ARM state CPSR and SPSRs are identical

- THUMB state SP maps onto ARM state R13

- THUMB state LR maps onto ARM state R14

- The THUMB state Program Counter maps onto the ARM state Program Counter (R15)

This relationship is shown in Figure 2.4: Mapping of THUMB state registers onto ARM state registers.

Figure 2.4: Mapping of THUMB state registers onto ARM state registers

## 2.7.4 Accessing Hi registers in THUMB state

In THUMB state, registers R8-R15 (the Hi registers) are not part of the standard register set. However, the assembly language programmer has limited access to them, and can use them for fast temporary storage.

A value may be transferred from a register in the range R0-R7 (a Lo register) to a Hi register, and from a Hi register to a Lo register, using special variants of the MOV instruction. Hi register values can also be compared against or added to Lo register values with the CMP and ADD instructions.

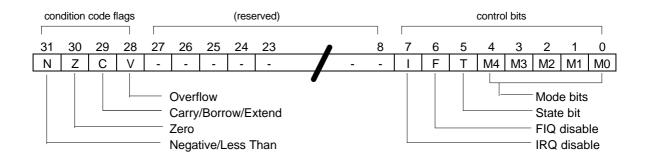

## 2.8 The Program Status Registers

The CPU contains a Current Program Status Register (CPSR), plus four Saved Program Status Registers (SPSRs) for use by exception handlers. These registers

- hold information about the most recently performed ALU operation

- control the enabling and disabling of interrupts

- set the processor operating mode

The arrangement of bits is shown in Figure 2.5: Program status register format.

Figure 2.5: Program status register format

## 2.8.1 The condition code flags

The N, Z, C and V bits are the condition code flags. These may be changed as a result of arithmetic and logical operations, and may be tested to determine whether an instruction should be executed.

In ARM state, all instructions may be executed conditionally. In THUMB state, only the Branch instruction is capable of conditional execution.

### 2.8.2 The control bits

The bottom 8 bits of a PSR (incorporating I, F, T and M [4:0]) are known collectively as the control bits. These will change when an exception arises. If the CPU is executing in a privileged mode, they can also be manipulated by software.

The T bit This reflects the operating state. When this bit is set, the CPU is

executing in THUMB state, otherwise it is executing in ARM state.

Note that the software must never change the state of the TBIT in the CPSR. If this happens, the CPU will enter an unpredictable state.

Interrupt disable bits The I and F bits are interrupt disable bits. When set, these disable

the IRQ and FIQ interrupts respectively.

The mode bits The M4, M3, M2, M1 and M0 bits (M[4:0]) are the mode bits.

These determine the CPU's operating mode, as shown in Table 2.1 PSR mode bit values. Not all combinations of the mode bits define a valid CPU mode. Only those explicitly described shall be used. The user should be aware that if any illegal value is programmed into the mode bits, M [4:0], then the CPU will enter an unrecoverable state.

If this occurs, reset should be applied.

Reserved bits The remaining bits in the PSRs are reserved. When changing a

PSR's flag or control bits, you must ensure that these unused bits are not altered. Also, your program should not rely on them containing specific values, since in future CPUs they may read as one or zero.

Table 2.1: PSR mode bit values

| M[4:0] | Mode       | Visible THUMB state registers                  | Visible ARM state registers                     |  |

|--------|------------|------------------------------------------------|-------------------------------------------------|--|

| 10000  | User       | R7R0,<br>LR, SP<br>PC, CPSR                    | R14R0,<br>PC, CPSR                              |  |

| 10001  | FIQ        | R7R0,<br>LR_fiq, SP_fiq<br>PC, CPSR, SPSR_fiq  | R7R0,<br>R14_fiqR8_fiq,<br>PC, CPSR, SPSR_fiq   |  |

| 10010  | IRQ        | R7R0,<br>LR_irq, SP_irq<br>PC, CPSR, SPSR_irq  | R12R0,<br>R14_irqR13_irq,<br>PC, CPSR, SPSR_irq |  |

| 10011  | Supervisor | R7R0,<br>LR_svc, SP_svc,<br>PC, CPSR, SPSR_svc | R12R0,<br>R14_svcR13_svc,<br>PC, CPSR, SPSR_svc |  |

| 11011  | Undefined  | R7R0<br>LR_und, SP_und,<br>PC, CPSR, SPSR_und  | R12R0,<br>R14_undR13_und,<br>PC, CPSR           |  |

| 11111  | System     | R7R0,<br>LR, SP<br>PC, CPSR                    | R14R0,<br>PC, CPSR                              |  |

## 2.9 Exceptions

Exceptions arise whenever the normal flow of a program has to be halted temporarily, for example to service an interrupt from a peripheral. Before an exception can be handled, the current CPU state must be preserved so that the original program can resume when the handler routine has finished.

It is possible for several exceptions to arise at the same time. If this happens, they are dealt with in a fixed order -see 2.9.9 Exception priorities.

## 2.9.1 Action on entering an exception

When handling an exception, the CPU:

- Preserves the address of the next instruction in the appropriate Link Register. If the exception has been entered from ARM state, then the address of the next instruction is copied into the Link Register (that is, current PC + 4 or PC + 8 depending on the exception. See Table 2.2 Exception entry/exit for details). If the exception has been entered from THUMB state, then the value written into the exception has been entered from THUMB state, then the value written into the Link Register is the current PC offset by a value such that the program resumes from the correct place on return from the exception. This means that the exception handler need not determine which state the exception was entered from. For example, in the case of SWI, MOVS PC, R14\_svc will always return to the next instruction regardless of whether the SWI was executed in ARM or THUMB state.

- 2 Copies the CPSR into the appropriate SPSR

- 3 Forces the CPSR mode bits to a value which depends on the exception

- 4 Forces the PC to fetch the next instruction from the relevant exception vector

It may also set the interrupt disable flags to prevent otherwise unmanageable nestings of exceptions.

If the CPU is in THUMB state when an exception occurs, it will automatically switch into ARM state when the PC is loaded with the exception vector address.

## 2.9.2 Action on leaving an exception

On completion, the exception handler:

- 1 Moves the Link Resister, minus an offset where appropriate, to the PC.(The offset will vary depending on the type of exception.)

- 2 Copies the SPSR back to the CPSR

- 3 Clears the interrupt disable flags, if they were set on entry

**Note:** An explicit switch back to THUMB state is never needed, since restoring the CPSR from the SPSR automatically sets the T bit to the value it held immediately prior to the exception.

## 2.9.3 Exception entry/exit summary

Table 2.2: Exception entry/exit summarizes the PC value preserved in the relevant R14 on exception entry, and the recommended instruction for exiting the exception handler.

| Table 2.2 : Exception entry/exit |                      |                          |                         |       |  |  |

|----------------------------------|----------------------|--------------------------|-------------------------|-------|--|--|

|                                  | Return Instruction   | Previous<br>ARM<br>R14_x | State<br>THUMB<br>R14_x | Notes |  |  |

| BL                               | MOV PC, R14          | PC + 4                   | PC + 2                  | 1     |  |  |

| SWI                              | MOVS PC, R14_svc     | PC + 4                   | PC + 2                  | 1     |  |  |

| UDEF                             | MOVS PC, R14_und     | PC + 4                   | PC + 2                  | 1     |  |  |

| FIQ                              | SUBS PC, R14_fiq, #4 | PC + 4                   | PC + 4                  | 2     |  |  |

| IRQ                              | SUBS PC, R14_irq, #4 | PC + 4                   | PC + 4                  | 2     |  |  |

| RESET                            | NA                   | -                        | -                       | 3     |  |  |

#### Note:

- 1 Where PC is the address of the BL/SWI/Undefined Instruction.

- Where PC is the address of the instruction which did not get executed since the FIQ or IRQ took priority.

- 3 The value saved in R14\_svc upon reset is unpredictable.

#### 2.9.4 FIQ

The FIQ (Fast Interrupt Request) exception is designed to support a data transfer or channel process, and in ARM state has sufficient private registers to remove the need for register saving (thus minimizing the overhead of context switching).

Irrespective of whether the exception was entered from ARM or Thumb state, a FIQ handler should leave the interrupt by executing

FIQ may be disabled by setting the CPSR's F flag (but note that this is not possible from User mode).

#### 2.9.5 IRQ

The IRQ (Interrupt Request) exception is a normal interrupt. IRQ has a lower priority than FIQ and is masked out when a FIQ sequence is entered. It may be disabled at any time by setting the I bit in the CPSR, though this can only be done from a privileged (non-User) mode.

Irrespective of whether the exception was entered from ARM or Thumb state, an IRQ handler should return from the interrupt by executing.

#### 2.9.6 Software interrupt

The software interrupt instruction (SWI) is used for entering Supervisor mode, usually to request a particular supervisor function. A SWI handler should return by executing the following irrespective of the state (ARM or Thumb):

This restores the PC and CPSR, and returns to the instruction following the SWI.

#### 2.9.7 Undefined instruction

When the CPU comes across an instruction which it cannot handle, it takes the undefined instruction trap. This mechanism may be used to extend either the THUMB or ARM instruction set by software emulation.

After emulating the failed instruction, the trap handler should execute the following irrespective of the state (ARM or Thumb):

This restores the CPSR and returns to the instruction following the undefined instruction.

## 2.9.8 Exception vectors

The following table shows the exception vector addresses.

Table 2.3: Exception vectors

| Address    | Exception             | Mode on entry |

|------------|-----------------------|---------------|

| 0x00000000 | Reset                 | Supervisor    |

| 0x00000004 | Undefined instruction | Undefined     |

| 0x00000008 | Software interrupt    | Supervisor    |

| 0x000000C  | Reserved              | Reserved      |

| 0x00000010 | Reserved              | Reserved      |

| 0x00000014 | Reserved              | Reserved      |

| 0x00000018 | IRQ                   | IRQ           |

| 0x0000001C | FIQ                   | FIQ           |

## 2.9.9 Exception priorities

When multiple exceptions arise at the same time, a fixed priority system determines the order in which they are handled:

Highest priority:

1 Reset 2 FIQ 3 IRQ

Lowest priority:

4 Undefined Instruction, software interrupt.

Not all exceptions can occur at once:

Undefined Instruction and Software Interrupt are mutually exclusive, since they each correspond to particular (non-overlapping) decodings of the current instruction.

#### 2.10 Reset

After a system reset, the CPU:

- Overwrites R14\_svc and SPSR\_svc by copying the current values of the PC and CPSR into them. The value of the saved PC and SPSR is not defined.

- Forces M [4:0] to 10011(Supervisor mode), sets the I and F bits in the CPSR.

- Forces the PC to fetch the next instruction from address 0x00.

- 4 Execution resumes in ARM state.

## 3 CPU Control Functions

| 3.1 | Overvi  | ew                                    | 3-2 |

|-----|---------|---------------------------------------|-----|

|     | 3.1.1   | Pins                                  | 3-2 |

|     | 3.1.2   | Control Registers                     | 3-3 |

| 3.2 | Contro  | l Registers                           | 3-3 |

|     | 3.2.1   | Standby Control Register (SBYCON)     | 3-3 |

|     | 3.2.2   | Clock Control Register (CKCON)        | 3-4 |

|     | 3.2.3   | Reset Status Register (RSTST)         | 3-5 |

| 3.3 | System  | n Resets                              | 3-6 |

|     | 3.3.1   | External Reset Signal (nRST)          | 3-6 |

|     | 3.3.2   | Watchdog Timer (WDT) Counter Overflow | 3-6 |

| 3.4 | Clock S | Signals                               | 3-7 |

| 3.5 | Standb  | y Mode                                | 3-8 |

#### 3.1 Overview

CPU control functions for this LSI include the following.

#### Reset control

This function controls the system reset function for initializing the CPU and on-chip peripherals.

#### Clock control

This function controls the oscillator circuit based on a crystal oscillator and a built-in phase-locked loop which together generate and control the system clock (SYSCLK) signal. It offers a choice of divider ratio (1/1, 1/2, and 1/4) for adjusting operating clock frequency to match the load of processing.

#### Standby mode control

This function controls the transitions to and from HALT mode.

#### 3.1.1 Pins

Table 3.1 lists the pins connected to the CPU control unit.

Table 3.1: CPU Control Unit Pins

| Pin Name                              | Symbol | Direction | Description                                                                                                                                                                           |

|---------------------------------------|--------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset input                           | nRST   | input     | "L" level input to this pin produces an external system reset for this LSI. "H" level input then causes execution to resume from address 0x000000.                                    |

| Crystal oscillator input pin          | OSC0   | input     | This pin is for connecting a crystal oscillator. If an external clock is used, supply it to this pin.                                                                                 |

| Crystal oscillator output pin         | OSC1   | output    | This pin is for connecting a crystal oscillator. If an external clock is used, leave this pin open                                                                                    |

| System clock (SYSCLK) output          | CLKOUT | output    | This output is the internal system clock (SYSCLK) signal.                                                                                                                             |

| PLL enable input                      | PLLEN  | input     | Connecting this pin to V DD enables the built-in phase-locked loop. If the PLL is not used because an external clock with a guaranteed duty is available, connect this pin to ground. |

| PLL frequency divider selection input | FSEL   | input     | Connect this pin to V DD or ground to indicate the frequency range for the basic clock.                                                                                               |

| VCO frequency selection input         | VCOM   | input     | This input controls the oscillation frequency of the PLL's voltage-controlled oscillator.  Connect it to ground.                                                                      |

#### 3.1.2 Control Registers

Table 3.2 lists the control registers for the CPU control unit.

Reads from these control registers takes exactly one clock cycle; writes, at least two. Modifying the standby control (SBYCON) or clock control (CKCON) register requires two operations: writing 0x0000003C and then writing the new value. Without the first, the second is ignored.

Table 3.2: CPU Control Unit Control Registers

| Table 6:2: 61 6 Gentrer Gill Gentrer Registers |                          |        |     |        |               |  |

|------------------------------------------------|--------------------------|--------|-----|--------|---------------|--|

| Address                                        | Name                     | Symbol | R/W | Size   | Initial value |  |

|                                                |                          |        |     | (bits) |               |  |

| 0x040_0000                                     | Standby Control Register | SBYCON | W   | 32     | 0x00000000    |  |

| 0x040_0004                                     | Clock Control Register   | CKCON  | R/W | 32     | 0x00000000    |  |

| 0x040_000C                                     | Reset Status Register    | RSTST  | R   | 32     | 0x00000000    |  |

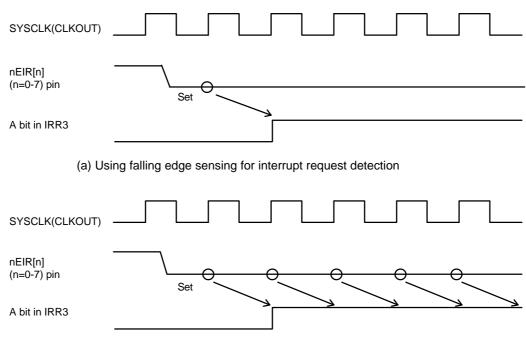

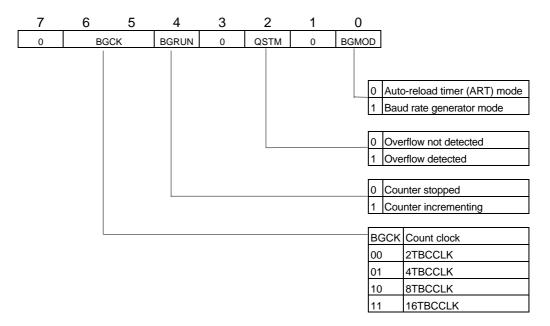

## 3.2 Control Registers