# 34 H25 Absolute Optical Encoder

#### **Electrical Specifications**

Code: 12 or 13 bits NB or GC; excess gray and BCD available Counts Per Shaft Turn: 4096 or 8192

Count Transition Accuracy: ± 1/2 bit maximum Supply Voltage: 5 - 28 VDC

Current Requirements: 120 mA typical

Output Formats: Parallel: Gray Code, Natural Binary and Binary Coded Decimal; Serial: Serial Synchronous Interface (SSI) compatible; Analog: 4-20 mA, 0-10V

Output Device: (see note 5) 7272: Line Driver, 5 – 28 VDC,  $V_{out} = V_{in}$ 7272: Line Driver, 5 – 28 VDC, Vout = 5 volts (special feature) 7273: Open Collector, accepts 5 - 28 VDC SSI: See page 40

Protection Level: Reverse, overvoltage and output short circuit protection (7272 only)

Frequency Response: 100kHz (1200 RPM for 12-bits, 600 RPM for 13-bits)

Output Termination Pinouts: See table page 41

Mechanical & Environmental Specs

Reference the H25 Incremental Encoder, pages 16-17

Connector

MS3112E14-19P, 19-pin connector on encoder body, mates to MS3116F14-19S (or equivalent)

NOTES & TABLES: All notes and tables referred to in the text can be found on pages 50 and 51.

|                         | ONE REVOLUTION                                                                                                 |   |

|-------------------------|----------------------------------------------------------------------------------------------------------------|---|

| 26 _                    | www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.ww | _ |

| 27 -                    |                                                                                                                | _ |

| 28 _                    |                                                                                                                | _ |

| 2 <sup>9</sup> -        |                                                                                                                | _ |

| 210 -                   |                                                                                                                | _ |

| iB (2 <sup>11</sup> ) = |                                                                                                                | - |

Long considered the industry standard for shafted incremental encoders, the Model H25 is now available in an absolute version up to 13 Bits of resolution. It incorporates many of the great standard features of the incremental version, including: EMI shielding, 40-Ib ABEC 7 bearings, matched thermal coefficients on critical components, and custom optics. This encoder features a 12 or 13 Bit absolute parallel gray code output, a selection line for count direction, and an output latch as standard. Output is standard gray code with options for natural binary or SSI compatible signals. Signals can be provided in either a single-ended multi-voltage line driver (TTL compatible when provided with 5 volts) or as an opencollector style of output. Typical applications include dam gate control, cranes, telescopes, tool changers, and robotics.

Certifications CE EN 55011 and EN 61000-6-2 See Regulatory Information on pages 47-49 for further certification details.

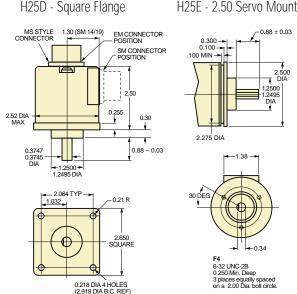

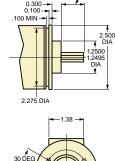

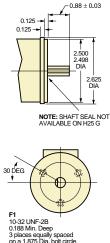

0.34

6-32 UNC-2B 0.250 Min. Deep 3 places equally spaced on a 2.00 Dia, bolt circle

$0.88 \pm 0.03$

H25G - 2.62 Dia Servo Mount

TOLERANCES:  $XX = \pm 0.01$ ,  $XXX = \pm 0.005$

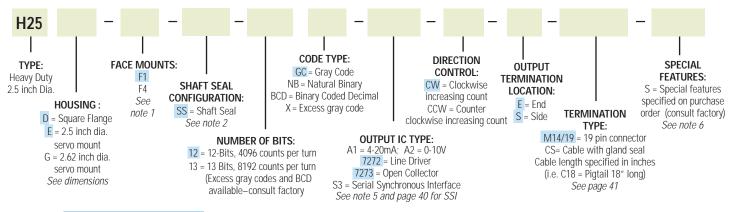

### H25 Absolute Encoder Ordering Options FOR ASSISTANCE CALL 800-350-2727

Use this diagram, working from left to right to construct your model number (example: H25E-F4-SS-12GC-7272-CW-SM14/19). All notes and tables referred to can be found on pages 50-51.

EXARELARSE ENCODERS? where highlighted multrel: 0765 standards aparso 7550 adore and Enimain on Standards and

# Parallel Absolute Output

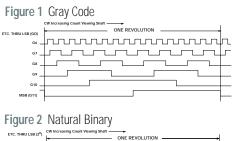

The two most common types of absolute outputs are the Gray Code and the Natural Binary. Resolution for absolute encoders is expressed in "bits" where each successive bit increases the resolution by a factor of two. For example, 10 bits =  $2^{10}$  = 1024 counts per revolution.

Natural binary code (Figure 1) is constructed so that the code counts up using the natural sequence of binary counting, i.e. 000, 001, 010, 011, 100 . . etc. The drawback to using this code sequence is that at several count positions the code will have transitions on multiple bits simultaneously. Due to the normal variations caused by gate delays, line impedances, etc. the actual transitions will not occur simultaneously. Reading data during one of these times could result in an erroneous reading. This can be overcome by taking multiple readings.

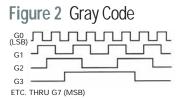

Gray code (Figure 2), by contrast, is designed to avoid the multiple transition problem entirely. It is specifically constructed so that only one bit will transition at a time. This ensures that state changes are much less ambiguous to the controller and is generally considered to be a more robust type of absolute code.

Regardless of the code type, one of the characteristics of absolute encoders is that they can readily be used for any resolution up to and including their maximum resolution. For example, a 12 bit encoder can be used at only 8 bits by ignoring (or disconnecting) the four lowest significant bits (LSB). This enables an installation that uses multiple absolute encoders to use the same encoder throughout with each controller using only the bits that it needs.

#### Figure 1 Natural Binary 2<sup>2</sup> 2<sup>3</sup> ETC. THRU 27 (MSB)

### Ordering 8-Bit Absolutes

For years, we produced encoders with a maximum resolution of 8 bits. Lots of those old 8 bit encoders are still around. We update them to newer 12 bit designs on a case-by-case basis. If you have an 8 bit encoder, here is how that model number was constructed: Direction of Rotation, Count, Code and Latch designators were inserted between Shaft Seal Configuration and Output IC as shown below. To specify an equivalent encoder based on the 12 bit design, please call our Applications Specialists at 800-ENCODER (800-362-6337) or check our web site at www.beiied.com.

Direction of Rotation: CCW or CW Count: 8

Code: GC = Gray Code or NB = Natural Binary Latch: L= Latch or Blank=None Output Terminations: EM20=MS3102R20-29P or ED25=DB25P; SM18 = MS3102R18-1P; C18 = Cable, with length specified in inches. Specify ED25 for Line Driver Outputs.

Example: H25E-F1-SS-CCW-8GC-7406R-EM20 (one possible encoder configuration with the 8-Bit Absolute Option.)

# Serial Synchronous Interface (SSI)

SSI output provides effective synchronization in a closed-loop control system. A clock pulse train from a controller is used to clock out sensor data: one bit of position data is transmitted to the controller per one clock pulse received by the sensor. The use of a differential driver permits reliable transmission of data over long distances in environments that may be electrically noisy. The encoder utilizes a clock signal, provided by the user interface, to time the data transmission. Receiving electronics must include an appropriate receiver as well as line terminating resistors.

#### Features

- · Synchronous transmission

- Transmission lengths to 1000 feet

- Accepts clock rates from 100 KHz to 1.8 MHz

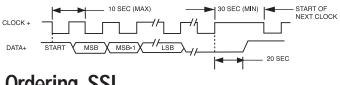

#### Data Transmission Sequence

- 1. Output driver of the encoder is a MAX 491 transceiver in transmit mode. The recommended receiver is a MAX 491 transceiver in receive mode.

- 2. Controller provides a series of pulses (or differential pulse pairs) on the CLOCK input lines.

- 3. On the first HIGH-to-LOW CLOCK transition, the encoder latches its data at the current position and prepares to transmit.

- 4. Controller reads data on the falling edge of the next 16 clock cycles.

- 5. The first bit is a START bit and is always HIGH.

- 6. Next come 12 data bits beginning with the most significant bit (MSB) and ending with the least significant bit (LSB). This is followed by three LOW pulses.

- 7. After the DATA bits, the DATA line goes LOW and remains LOW for a minimum of 30 microseconds between the end of the DATA bits and the beginning of the next CLOCK series.

#### Interfacing Long Data Lines

Cable impedance can create a transmission delay, in effect, shifting the phase relationship between the clock pulse and the data. If this phase shift exceeds 180°, then the wrong bit position will be sampled by the receiver. As a result, the maximum allowable clock frequency is a function of the cable length. For 24 AWG, stranded, 3 pair cable (BEI part number 37048-003 or equivalent) the group delay is 1.36ns/ft. The table below shows the maximum transmission rate allowable as a function of cable length to ensure a phase shift of less than 90°.

CLOCK, Maximum (kHz) = 92,000 / Cable Length (ft)CW

| Cable Length (ft) | 50   | 100 | 200 | 300 | 500 | 1000 |

|-------------------|------|-----|-----|-----|-----|------|

| Max Freq (kHz)    | 1800 | 900 | 500 | 300 | 200 | 100  |

#### SSI Timing

### Ordering SSI

HOW TO SPECIFY SSI OUTPUT IN THE ENCODER MODEL NUMBER:

Use the designation, S3 between the Code Format designation and the Connector designation.

#### Example: H25D-SS-12GC-S3-CW-SM18

SUNSTAR自动化 http://www.sensor-ic.com/ TEL: 0755-83376489 FAX:0755-83376182 E-MAIL: szss20@163.com

# **Single Turn Absolute Encoder Options**

The tables below are reference for pinouts, connections and operation of BEI's single turn absolute encoders. These absolute options are available in a wide range of package styles with a variety of outputs. The applicability table below shows which combinations are currently available. As always, you can call us at **800-360-ASAP** (2727) for immediate applications assistance should you have any questions.

| Output Code and Terminations (12 & 13 Bit) |                               |                                              |                   |                 |                            |                  |      |                            |  |

|--------------------------------------------|-------------------------------|----------------------------------------------|-------------------|-----------------|----------------------------|------------------|------|----------------------------|--|

| PARALLEL CODE                              |                               |                                              |                   |                 |                            | TERMINATION TYPE |      |                            |  |

|                                            | Gray Code                     |                                              | Natural<br>Binary |                 | Binary<br>Coded<br>Decimal | Cable            | Conn | Term<br>Board<br>H38 & H40 |  |

|                                            | 12 Bit                        |                                              | 12 Bit            | 13 Bit          |                            |                  |      |                            |  |

| MSB                                        | G <sub>11</sub>               | G <sub>12</sub>                              | 211               | 2 <sup>12</sup> | A <sub>0</sub>             | WHT/BLK          | Α    | 1                          |  |

|                                            | G <sub>10</sub>               | G <sub>11</sub>                              | 2 <sup>10</sup>   | 2 <sup>11</sup> | B <sub>0</sub>             | WHT/BRN          | В    | 2                          |  |

|                                            | G <sub>9</sub>                | G <sub>10</sub>                              | 2 <sup>9</sup>    | 2 <sup>10</sup> | Co                         | WHT/RED          | С    | 3                          |  |

|                                            | G <sub>8</sub>                | G9                                           | 2 <sup>8</sup>    | 2 <sup>9</sup>  | D <sub>0</sub>             | WHT/ORN          | D    | 4                          |  |

|                                            | G <sub>7</sub>                | G <sub>8</sub>                               | 27                | 28              | A <sub>1</sub>             | WHT/YEL          | E    | 5                          |  |

|                                            | G <sub>6</sub> G <sup>7</sup> |                                              | 26                | 27              | B <sub>1</sub>             | WHT/GRN          | F    | 6                          |  |

|                                            | G <sub>5</sub>                | G <sub>6</sub>                               | 2 <sup>5</sup>    | 26              | C <sub>1</sub>             | WHT/BLU          | G    | 7                          |  |

|                                            | G <sub>4</sub>                | $G_5$                                        | 24                | 2 <sup>5</sup>  | D <sub>1</sub>             | WHT/VIO          | Н    | 8                          |  |

|                                            | G <sub>3</sub>                | G <sub>3</sub> G <sub>4</sub>                |                   | 24              | A <sub>2</sub>             | WHT/GRY          | J    | 9                          |  |

|                                            | G <sub>2</sub>                | G <sub>3</sub>                               | ·                 |                 | B <sub>2</sub>             | WHT              | K    | 10                         |  |

|                                            | G <sub>1</sub>                | G <sub>2</sub>                               |                   |                 | C <sub>2</sub>             | GRY/BLK          | L    | 11                         |  |

| LSB <sub>12</sub>                          | G <sub>0</sub>                | G <sub>1</sub> 2 <sup>0</sup> 2 <sup>1</sup> |                   | 2 <sup>1</sup>  | D <sub>2</sub>             | GRY/BRN          | М    | 12                         |  |

| LSB <sub>13</sub>                          | G <sub>0</sub>                |                                              | 20                | A <sub>3</sub>  | GRY/RED                    | N                | 13   |                            |  |

|                                            | *0V (                         | CIRCUI                                       | т сом             | MON)            | GRY/RED                    | Р                |      |                            |  |

|                                            |                               | DIRECT                                       | FION C            | ONTRO           | ORN                        | R                | 18   |                            |  |

|                                            |                               | CAS                                          | e groi            | JND             | GRN                        | S                | 16   |                            |  |

|                                            | 0                             | V (CIR                                       | CUIT C            | OMMO            | BLK                        | Т                | 15   |                            |  |

|                                            |                               | LATCH                                        | I CONT            | ROL             | YEL                        | U                | 17   |                            |  |

|                                            | +                             | V (SUP                                       | PLY VO            | LTAGE)          | RED                        | V                | 14   |                            |  |

|                                            |                               | SHI                                          | eld di            | RAIN            | BARE                       |                  |      |                            |  |

\*Pin P is available for a tri-state option

|       | Output Applicability Table |         |               |               |     |            |        |  |  |  |

|-------|----------------------------|---------|---------------|---------------|-----|------------|--------|--|--|--|

|       | 12 BITS                    | 13 BITS | 14/15<br>BITS | 12x12<br>BITS | SSI | 4–20<br>mA | 0–10 V |  |  |  |

| H25   | •                          | •       |               |               | •   | •          | •      |  |  |  |

| H25X  |                            |         | •             |               |     |            |        |  |  |  |

| HS35  | •                          |         |               |               | •   |            |        |  |  |  |

| H38   | •                          | •       |               | •             | •   | •          | •      |  |  |  |

| H40   | •                          | •       |               | •             | •   | •          | •      |  |  |  |

| HMT25 |                            |         |               | •             | •   |            |        |  |  |  |

**Direction Control:** Standard is CW increasing when viewed from the shaft end. Pin R is normally HI (or N/C) and is pulled up internally to +V. To reverse the count direction, Pin R must be pulled LO (COMMON).

**Latch control:** Encoder outputs are active and provide continuous parallel position information when Pin U is HI (or N/C). Pin U is pulled up internally to +V. When Pin U is LO (COMMON) the encoder outputs are latched at the logic state that is present when the latch is applied and will stay latched until Pin U is no longer grounded.

|       |                      | טוע                  |                      |                      |   |

|-------|----------------------|----------------------|----------------------|----------------------|---|

|       | Gray Code            |                      | Natural              | M14/19<br>Connector  |   |

|       | 14 BIT               | 15 Bit               | 14 BIT               | 15 Bit               |   |

| LSB   | GO                   | GO                   | 20                   | 20                   | А |

|       | G <sub>1</sub>       | G <sub>1</sub>       | 2 <sup>1</sup>       | 2 <sup>1</sup>       | В |

|       | G <sub>2</sub>       | G <sub>2</sub>       | 2 <sup>2</sup>       | 2 <sup>2</sup>       | С |

|       | G3                   | G3                   | 2 <sup>3</sup>       | 2 <sup>3</sup>       | D |

|       | G <sub>4</sub>       | G <sub>4</sub>       | 24                   | 24                   | E |

|       | G5                   | G5                   | 2 <sup>5</sup>       | 2 <sup>5</sup>       | F |

|       | G <sub>6</sub>       | G <sub>6</sub>       | 26                   | 26                   | G |

|       | G7                   | G7                   | 27                   | 27                   | Н |

|       | G8                   | G <sub>8</sub>       | 2 <sup>8</sup>       | 2 <sup>8</sup>       | J |

|       | G9                   | G9                   | 2 <sup>9</sup>       | 2 <sup>9</sup>       | К |

|       | G <sub>10</sub>      | G <sub>10</sub>      | 2 <sup>10</sup>      | 2 <sup>10</sup>      | L |

|       | G <sub>11</sub>      | G <sub>11</sub>      | 2 <sup>11</sup>      | 2 <sup>11</sup>      | М |

|       | G <sub>12</sub>      | G <sub>12</sub>      | 2 <sup>12</sup>      | 2 <sup>12</sup>      | Ν |

| MSB14 | G <sub>13</sub>      | G <sub>13</sub>      | 2 <sup>13</sup>      | 2 <sup>13</sup>      | Р |

| MSB15 | DIR<br>CONTROL       | G <sub>14</sub>      | DIR<br>CONTROL       | 2 <sup>14</sup>      | R |

|       | CASE<br>GROUND       | CASE<br>GROUND       | CASE<br>GROUND       | CASE<br>GROUND       | S |

|       | CIRCUIT<br>COMMON    | CIRCUIT<br>COMMON    | CIRCUIT<br>COMMON    | CIRCUIT<br>COMMON    | Т |

|       | LATCH                | DIR/LATCH            | LATCH                | DIR/LATCH            | U |

|       | +V SUPPLY<br>VOLTAGE | +V SUPPLY<br>Voltage | +V SUPPLY<br>VOLTAGE | +V SUPPLY<br>VOLTAGE | V |

Parallel Code (14

15 Rit

| SSI Output Termination Table |             |                |               |                |              |  |  |  |  |

|------------------------------|-------------|----------------|---------------|----------------|--------------|--|--|--|--|

|                              | M18<br>CONN | M14/19<br>CONN | CABLE<br>CONN | TERM. E<br>H38 | BOARD<br>H48 |  |  |  |  |

| DATA +                       | А           | A              | YEL           | 4              | 1            |  |  |  |  |

| DATA-                        | Н           | В              | WHT/YEL       | 7              | 7            |  |  |  |  |

| CLOCK+                       | В           | С              | BLU           | 5              | 2            |  |  |  |  |

| CLOCK-                       | I           | D              | WHT/BLU       | 8              | 8            |  |  |  |  |

| DIR CONTROL                  | С           | R              | ORN           | 6              | 3            |  |  |  |  |

| CASE GROUND                  | G           | S              | BARE/SHIELD   | 1              | 6            |  |  |  |  |

| CIRCUIT COMMON               | F           | Т              | BLK           | 2              | 5            |  |  |  |  |

| +V SUPPLY VOLTAGE            | D           | V              | RED           | 3              | 4            |  |  |  |  |

| SHIELD DRAIN                 | _           | —              | BARE          |                | _            |  |  |  |  |

**M18 Connector** is a MS3102E18-1P, 10-pin connector on the encoder body and mates to an MS3106F18-1S connector or can be used with a standard cable/connector assembly, BEI P/N 924-31186-18XX (Where X = 10, 20 or 30 for a 10, 20, or 30 foot length). This is the preferred connector for SSI output.

Dir/Latch on 15-Bit Encoders: Due to a limited number of connector pins, either direction controsいの状態であります。 2015年14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-199、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and mater to ap MS3112E14-198、19-Pin connector on the encoder body and the en