# INERTIAL SENSOR: 3Axis - 2g/6g DIGITAL OUTPUT LINEAR ACCELEROMETER

PRODUCT PREVIEW

- 2.7V TO 3.6V SINGLE SUPPLY OPERATION

- I2C/SPI DIGITAL OUTPUT INTERFACES

- MOTION ACTIVATED INTERRUPT SOURCE

- FACTORY TRIMMED DEVICE SENSITIVITY AND OFFSET

- EMBEDDED SELF TEST

- HIGH SHOCK SURVIVABILITY

#### **DESCRIPTION**

The LIS3L02DS is a tri-axis digital output linear accelerometer that includes a sensing element and an IC interface able to take the information from the sensing element and to provide the measured acceleration signals to the external world through an I2C/SPI serial interface.

The sensing element, capable to detect the acceleration, is manufactured using a dedicated process called THELMA (Thick Epi-Poly Layer for Microactuators and Accelerometers) developed by ST to produce inertial sensors and actuators in silicon.

The IC interface instead is manufactured using a CMOS process that allows high level of integration to design a dedicated circuit which is factory trimmed to better match the sensing element characteristics

The LIS3L02DS has a user selectable full scale of 2g, 6g and it is capable of measuring accelerations

over a maximum bandwidth of 2.0 KHz for the X, Y axis and Z axis. The device bandwidth may be programmed accordingly to the application requirements. A self-test capability allows the user to check the functioning of the system.

The device may be configured to generate an inertial wake-up/interrupt signal when a programmable acceleration threshold is exceeded along one of the three axis.

The LIS3L02DS is available in plastic SMD package and it is specified over a temperature range extending from -40°C to +85°C.

The LIS3L02DS belongs to a family of products suitable for a variety of applications:

- Antitheft systems and Inertial navigation

- Virtual reality input devices

- Vibration Monitoring, recording and compensation

- Robotics and Appliance control

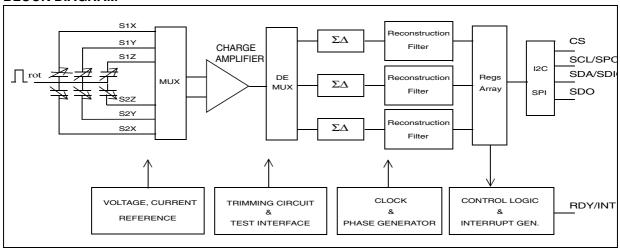

#### **BLOCK DIAGRAM**

February 2004 1/18

This is preliminary information on a new product now in development. Details are subject to change without notice.

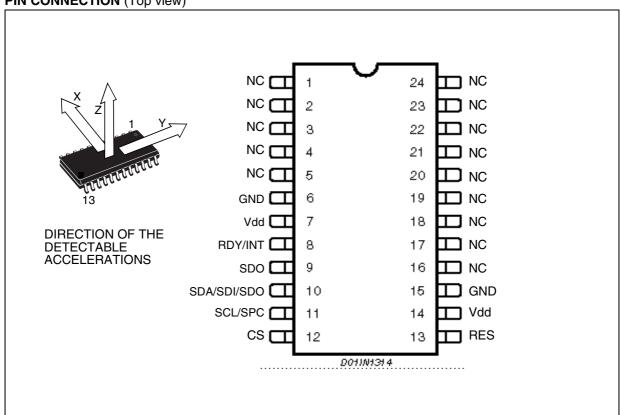

## **PIN DESCRIPTION**

| N°       | Pin                 | Function                                                                                    |

|----------|---------------------|---------------------------------------------------------------------------------------------|

| 1 to 5   | NC                  | Internally not connected                                                                    |

| 6        | GND                 | 0V supply                                                                                   |

| 7        | Vdd                 | Power supply                                                                                |

| 8        | RDY/INT             | Data ready/inertial wake-up interrupt                                                       |

| 9        | SDO                 | SPI Serial Data Output                                                                      |

| 10       | SDA/<br>SDI/<br>SDO | I2C Serial Data (SDA) SPI Serial Data Input (SDI) 3-wire Interface Serial Data Output (SDO) |

| 11       | SCL/SPC             | I2C Serial Clock (SCL)<br>SPI Serial Port Slock (SPC)                                       |

| 12       | CS                  | SPI enable I2C/SPI mode selection (1: I2C mode; 0: SPI enabled)                             |

| 13       | RES                 | Reserved. Either leave unconnected or connect to Vdd                                        |

| 14       | Vdd                 | Power supply                                                                                |

| 15       | GND                 | 0V supply                                                                                   |

| 16 to 24 | NC                  | Internally not connected                                                                    |

## PIN CONNECTION (Top view)

## **ELECTRICAL CHARACTERISTCS** (Temperature range -40°C to +85°C)

All the parameters are specified @ Vdd=3.3V and T=25°C unless otherwise noted

| Symbol    | Parameter                               | Test Condition                                                    | Min.   | Typ. <sup>1</sup> | Max.   | Unit |

|-----------|-----------------------------------------|-------------------------------------------------------------------|--------|-------------------|--------|------|

| Vdd       | Supply voltage                          |                                                                   | 2.7    |                   | 3.6    | V    |

| Idd       | Supply current                          | T = 25°C                                                          |        | 1                 | 1.5    | mA   |

| IddPdn    | Current consumption in power-down mode  | T = 25°C                                                          |        |                   | 10     | μА   |

| BW        | Digital Filter Cut-Off frequency (-3dB) |                                                                   |        | 70                | 1150   | Hz   |

| FS        | Measurement range <sup>2</sup>          | FS bit set to 0                                                   |        | ±2.0              |        | g    |

|           |                                         | FS bit set to 1                                                   |        | ±6.0              |        | g    |

| FSAcc     | Full-scale accuracy                     | T = 25°C<br>Full-scale = 2g                                       | FS-10% | FS                | FS+10% | g    |

|           |                                         | T = 25°C<br>Full-scale = 6g                                       | FS-15% | FS                | FS+15% | g    |

| So        | Device Resolution                       | T = 25°C<br>Full-scale = 2g<br>BW=56Hz                            |        | 1                 |        | mg   |

| 0g-Offset | Zero g level                            | T = 25°C<br>Full-scale = 2g                                       | -50    |                   | 50     | mg   |

| NL        | Non Linearity                           | Best fit straight line<br>X, Y axis<br>Full-scale = 2g<br>BW=56Hz |        | ±1                |        | % FS |

|           |                                         | Best fit straight line<br>Z axis<br>Full-scale = 2g<br>BW=56Hz    |        | ±3                |        | % FS |

| DR1       | Output data rate                        | Dec factor = 128                                                  |        | 280               |        | Hz   |

| DR2       | Output data rate                        | Dec factor = 64                                                   |        | 560               |        | Hz   |

| DR3       | Output data rate                        | Dec factor = 32                                                   |        | 1120              |        | Hz   |

| DR4       | Output data rate                        | Dec factor = 8                                                    |        | 4480              |        | Hz   |

| Ton       | Turn-on time                            |                                                                   |        | 50                |        | ms   |

#### Notes

<sup>&</sup>lt;sup>1</sup> Typical specifications are not guaranteed

<sup>&</sup>lt;sup>2</sup> Guaranteed by wafer level test and measurement of initial offset and sensitivity

## **ABSOLUTE MAXIMUM RATING**

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol           | Ratings                                                                   | Maximum Value        | Unit |

|------------------|---------------------------------------------------------------------------|----------------------|------|

| Vdd              | Supply voltage                                                            | -0.3 to 6            | V    |

| Vin              | Input voltage on any control pin (CS, SCL/SPC, SDA/SDI/SDO, SDO, RDY/INT) | Vss -0.3 to Vdd +0.3 | V    |

| A <sub>POW</sub> | Acceleration (Any axis, Powered, Vdd=3.3V)                                | 3000g for 0.5 ms     |      |

| A <sub>UNP</sub> | Acceleration (Any axis, Unpowered)                                        | 3000g for 0.5 ms     |      |

| T <sub>OP</sub>  | Operating Temperature Range                                               | -40 to +85           | °C   |

| T <sub>STG</sub> | Storage Temperature Range                                                 | -40 to +105          | °C   |

#### 1 FUNCTIONALITY

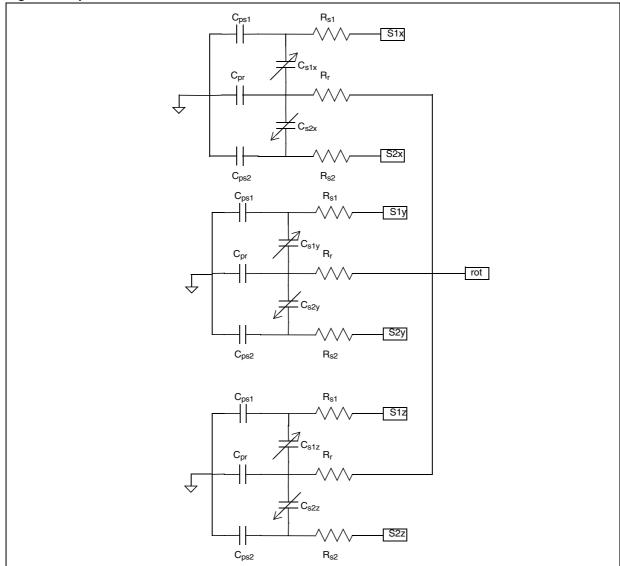

#### 1.1 Sensing element

The THELMA process is utilized to create a surface micro-machined accelerometer. The technology allows to carry out suspended silicon structures which are attached to the substrate in a few points called anchors and free to move on a plane parallel to the substrate itself. To be compatible with the traditional packaging techniques a cap is placed on top of the sensing element to avoid blocking the moving parts during the molding phase.

The equivalent circuit for the sensing element is shown in the below figure; when a linear acceleration is applied, the proof mass displaces from its nominal position, causing an imbalance in the capacitive half-bridge. This imbalance is measured using charge integration in response to a voltage pulse applied to the sense capacitor.

The nominal value of the capacitors, at steady state, is few pF and when an acceleration is applied the maximum variation of the capacitive load is few tenth of pF.

Figure 1. Equivalent electrical circuit

#### 1.2 IC Interface

The complete measurement chain is composed by a low-noise capacitive amplifier which converts into an analog voltage the capacitive unbalancing of the MEMS sensor and by three  $\Sigma\Delta$  analog-to-digital converters, one for each axis, that translates the produced signal into a digital bitstream.

The  $\Sigma\Delta$  converters are tigthly coupled with dedicated reconstruction filters which removes the high frequency components of the quantization noise and provides low rate and high resolution digital words.

The charge amplifier and the  $\Sigma\Delta$  converters are operated respectively at 107.5 KHz and 35.8 KHz.

The data rate at the output of the reconstruction depends on the user selected Decimation Factor (DF) and span from 280 Hz to 4.48 KHz.

The acceleration data may be accessed through an I2C/SPI interface thus making the device particularly suitable for direct interfacing with a microcontroller.

The LIS3L02DS features a Data-Ready signal (DRY) which indicated when a new set of measured acceleration data is available thus simplifying data synchronization in digital system employing the device itself. The LIS3L02DS may also be configured to generate an inertial wake-up/interrupt signal when a programmable acceleration threshold is exceeded along one of the three axis.

#### 1.3 Factory calibration

The IC interface is factory calibrated to provide to the final user a device ready to operate. The parameters which are trimmed are: gain, offset, common mode and internal clock frequency.

The trimming values are stored inside the device by a non volatile structure. Any time the device is turned on, the trimming parameters are downloaded into the registers to be employed during the normal operation thus allowing the final user to employ the device without any need for further calibration

#### 2 DIGITAL INTERFACES

The registes embedded inside the LIS3L02DS may be accessed through both the 2C and SPI serial interfaces. The latter may be SW configured to operate either in SPI mode or in 3-wire interface mode.

The serial interfaces are mapped onto the same pads. To select/exploit the I2C interface, CS line must be tied high (i.e connected to Vdd).

**Table 1. Serial Interface Pin Description**

| PIN Name    | PIN Description                                                                             |

|-------------|---------------------------------------------------------------------------------------------|

| CS          | SPI enable I2C/SPI mode selection (1: I2C mode; 0: SPI enabled)                             |

| SCL/SPC     | I2C Serial Clock (SCL)<br>SPI Serial Port Slock (SPC)                                       |

| SDA/SDI/SDO | I2C Serial Data (SDA) SPI Serial Data Input (SDI) 3-wire Interface Serial Data Output (SDO) |

| SDO         | SPI Serial Data Output (SDO)                                                                |

#### 2.1 I2C Serial Interface

The LIS3L02DS I2C is a bus slave. The I2C is employed to write the data into the registers whose content can also be read back.

The relevant I<sup>2</sup>C terminology is given in the table below

**Table 2. Serial Interface Pin Description**

| Term        | Description                                                                              |

|-------------|------------------------------------------------------------------------------------------|

| Transmitter | The device which sends data to the bus                                                   |

| Receiver    | The device which receives data from the bus                                              |

| Master      | The device which initiates a transfer, generates clock signals and terminates a transfer |

| Slave       | The device addressed by the master                                                       |

There are two signals associated with the I<sup>2</sup>C bus: the Serial Clock Line (SCL) and the Serial DAta liine (SDA). The latter is a bidirectional line used for sending and receiving the data to/form the interface. Both the lines are connected to Vdd through a pull-up resistor embedded inside the LIS3L02DS. When the bus is free both the lines are high.

## 2.1.1 I<sup>2</sup>C Operation

The transaction on the bus is started through a START signal. A START condition is defined as a HIGH to LOW transition on the data line while the SCL line is held HIGH. After this has been transmitted by the Master, the bus is considered busy. The next byte of data transmitted after the start condition contains the address of the slave in the first 7 bits and the eighth bit tells whether the Master is receiving data from the slave or transmitting data to the slave. When an address is sent, each device in the system compares the first seven bits after a start condition with it's address. If they match, the device considers itself addressed by the Master. The address can be made up of a programmable part and a fixed part, thus allowing more than one device of the same type to be connected to the I<sup>2</sup>C bus.

The Slave ADdress (SAD) associated to the LIS3L02DS is 0011101.

Data transfer with acknowledge is mandatory. The transmitter must release the SDA line during the ac-

47/

knowledge pulse. The receiver must then pull the data line LOW so that it remains stable low during the HIGH period of the acknowledge clock pulse. A receiver which has been addressed is obliged to generate an acknowledge after each byte of data has been received.

The I<sup>2</sup>C embedded inside the Gengine ASIC behaves like a slave device and the following protocol must be adhered to. After the start condition (ST) a salve address is sent, once a slave acknowledge has been returned, a 8-bit sub-address will be transmitted: the 7 LSB represent the actual register address while the MSB enables address autoincrement. If the MSB of the SUB field is 1, the SUB (register address) will be automatically incremented to allow multiple data read/write.

If the LSB of the slave address was '1' (read), a repeated START condition will have to be issued after the two sub-address bytes; if the LSB is '0' (write) the Master will transmit to the slave with direction unchanged.

Transfer when Master is writing one byte to slave

| Ma  | aster | ST | SAD + W |     | SUB |     | DATA |     | SP |

|-----|-------|----|---------|-----|-----|-----|------|-----|----|

| Sla | ave   |    |         | SAK |     | SAK |      | SAK |    |

Transfer when Master is writing multiple bytes to slave:

| Master | ST | SAD + W |     | SUB |     | DATA |     | DATA |     | SP |

|--------|----|---------|-----|-----|-----|------|-----|------|-----|----|

| Slave  |    |         | SAK |     | SAK |      | SAK |      | SAK |    |

Transfer when Master is receiving (reading) one byte of data from slave:

| Master | ST | SAD + W |     | SUB |     | SR | SAD + R |     |      | NMAK | SP |

|--------|----|---------|-----|-----|-----|----|---------|-----|------|------|----|

| Slave  |    |         | SAK |     | SAK |    |         | SAK | DATA |      |    |

Transfer when Master is receiving (reading) multiple bytes of data from slave

| Master | ST | SAD + W |     | SUB |     | SR | SAD + R |     |      | MAK |

|--------|----|---------|-----|-----|-----|----|---------|-----|------|-----|

| Slave  |    |         | SAK |     | SAK |    |         | SAK | DATA |     |

| Master | SR |      | MAK |      | NMAK | SP |

|--------|----|------|-----|------|------|----|

| Slave  |    | DATA |     | DATA |      |    |

Data are transmitted in byte format. Each data transfer contains 8 bits. The number of bytes transferred per transfer is unlimited. Data is transferred with the Most Significant Bit (MSB) first. If a receiver can't receive another complete byte of data until it has performed some other function, it can hold the clock line, SCL LOW to force the transmitter into a wait state. Data transfer only continues when the receiver is ready for another byte and releases the data line. If a slave receiver doesn't acknowledge the slave address (i.e. it is not able to receive because it is performing some real time function) the data line must be left HIGH by the slave. The Master can then abort the transfer. A LOW to HIGH transition on the SDA line while the SCL line is HIGH is defined as a STOP condition. Each data transfer must be terminated by the generation of a STOP condition.

In order to read multiple bytes, it is necessary to assert the most significant bit of the sub-address field. In other words, SUB(7) must be equal to 1 while SUB(6-0) represents the address of first register to read.

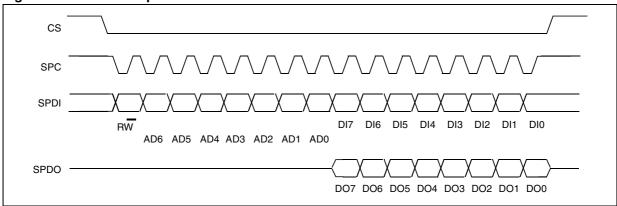

#### 2.2 SPI Bus Interface

The Gengine SPI is a bus slave. The SPI allows to write and read the registers of the device. The Serial Interface interacts with the outside world with 4 wires: CS, SPC, SPDI and SPDO.

## 2.2.1 Read & Write registers

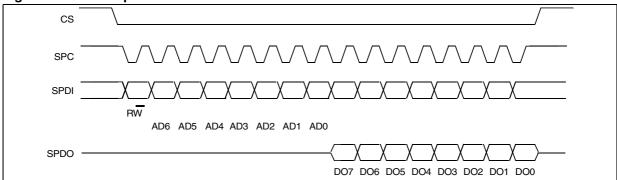

Figure 2. Read & write protocol

CS is the Serial Port Enable and it is controlled by the SPI master. It goes low at the start of the transmission and goes back high at the end. SPC is the Serial Port Clock and it is controlled by the SPI master. It is stopped high when CS is high (no transmission). SPDI and SPDO are respectively the Serial Port Data Input and Output. Those lines are driven at the falling edge of SPC and should be captured at the rising edge of SPC.

Both the Read Register and Write Register commands are completed in 16 clocks pulses. Bit duration is the time between two falling edges of SPC. The first bit (bit 0) starts at the first falling edge of SPC after the falling edge of CS while the last bit (bit 15) starts at the last falling edge of SPC just before the rising edge of CS.

- bit 0: RW bit. When 0, the data DI(7:0) is written into the device. When 1, the data DO(7:0) from the device is read. In latter case, the chip will drive SPDO at the start of bit 8.

- bit 1-7: address AD(6:0). This is the address field of the indexed register.

- bit 8-15: data DI(7:0) (write mode). This is the data that will be written into the device (MSb first).

- bit 8-15: data DO(7:0) (read mode). This is the data that will be read from the device (MSb first).

#### 2.2.2 SPI Read

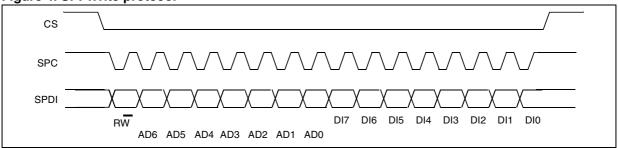

Figure 3. SPI Read protocol

The SPI Read command consists is performed with 16 clocks pulses:

- bit 0: READ bit. The value is 1.

- bit 1-7: address AD(6:0). This is the address field of the indexed register.

- bit 8-15: data DO(7:0) (read mode). This is the data that will be read from the device (MSb first).

## 2.2.3 SPI Write

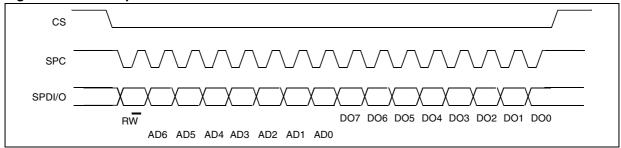

Figure 4. SPI Write protocol

The SPI Write command consists is performed with 16 clocks pulses.

- bit 0: WRITE bit. The value is 0.

- bit 1-7: address AD(3:0). This is the address field of the indexed register.

- bit 8-15: data DI(7:0) (write mode). This is the data that will be written inside the device (MSb first).

## 2.2.4 SPI Read in 3-wires mode

3-wires mode is entered by setting to 1 bit SIM (SPI Serial Interface Mode selection) in A\_IF\_CTRL2.

Figure 5. SPI Read protocol in 3-wires model

The SPI Read command consists is performed with 16 clocks pulses:

- bit 0: READ bit. The value is 1.

- bit 1-7: address AD(6:0). This is the address field of the indexed register.

- bit 8-15: data DO(7:0) (read mode). This is the data that will be read from the device (MSb first).

## 3 REGISTERS MAPPING

The table given below provides a listing of the registers embedded in the device and the related address. All the "application related" registers (i.e. control, status, data) are mapped into Bank2 so to simplify their access when running through the SPI interface.

Table 3. Registers address map

| Don Nome    | T    | Register A        | ddress  | Size  | 0              |

|-------------|------|-------------------|---------|-------|----------------|

| Reg. Name   | Туре | Binary            | Hex     | (Bit) | Comment        |

|             |      | 0000000 - 0010101 | 00 - 15 |       | Reserved       |

| OFFSET_X    | rw   | 0010110           | 16      | 8     | Loaded at boot |

| OFFSET_Y    | rw   | 0010111           | 17      | 8     | Loaded at boot |

| OFFSET_Z    | rw   | 0011000           | 18      | 8     | Loaded at boot |

| GAIN_X      | rw   | 0011001           | 19      | 8     | Loaded at boot |

| GAIN_Y      | rw   | 0011010           | 1A      | 8     | Loaded at boot |

| GAIN_Z      | rw   | 0011011           | 1B      | 8     | Loaded at boot |

|             |      | 0011100 - 0011111 | 1C - 1F |       | Reserved       |

| CTRL_REG1   | rw   | 0100000           | 20      | 8     |                |

| CTRL_REG2   | rw   | 0100001           | 21      | 8     |                |

|             |      | 0100010           | 22      |       | Reserved       |

| WAKE_UP_CFG | rw   | 0100011           | 23      | 8     |                |

| WAKE_UP_SRC | r    | 0100100           | 24      | 8     |                |

| WAKE_UP_ACK | r    | 0100101           | 25      | 8     |                |

|             |      | 0100110           | 26      |       | Reserved       |

| STATUS_REG  | rw   | 0100111           | 27      | 8     |                |

| OUTX_L      | r    | 0101000           | 28      | 8     |                |

| OUTX_H      | r    | 0101001           | 29      | 8     |                |

| OUTY_L      | r    | 0101010           | 2A      | 8     |                |

| OUTY_H      | r    | 0101011           | 2B      | 8     |                |

| OUTZ_L      | r    | 0101100           | 2C      | 8     |                |

| OUTZ_H      | r    | 0101101           | 2D      | 8     |                |

| THS_L       | rw   | 0101110           | 2E      | 8     |                |

| THS_H       | rw   | 0101111           | 2F      | 8     |                |

|             |      | 0110000 - 1111111 | 30 - 3F |       | Reserved       |

## 4 REGISTERS DESCRIPTION

The device contains a set of registers which are used to control its behavior and to retrieve acceleration data.

## 4.1 OFFSET\_X (16h)

| OX7 | OX6 | OX5 | OX4 | ОХЗ | OX2 | OX1 | OX0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

|--|

## 4.2 OFFSET\_Y (17h)

| OY7 OY6 OY | 5 OY4 | OY3 | OY2 | OY1 | OY0 |

|------------|-------|-----|-----|-----|-----|

|------------|-------|-----|-----|-----|-----|

| DOY7, DOY0 | Digital Offset Trimming for Y-Axis |

|------------|------------------------------------|

|------------|------------------------------------|

## 4.3 OFFSET\_Z (18h)

| OZ7 | OZ6 | OZ5 | OZ4 | OZ3 | OZ2 | OZ1 | OZ0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

|--|

## 4.4 GAIN\_X (19h)

| GX7 | GX6 | GX5 | GX4 | GX3 | GX2 | GX1 | GX0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| GX7, GX0 | Digital Gain Trimming for X-Axis |  |

|----------|----------------------------------|--|

|----------|----------------------------------|--|

## 4.5 GAIN\_Y (1Ah)

| GY7 | GY6 | GY5 | GY4 | GY3 | GY2 | GY1 | GY0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| GY7, GY0 | Digital Gain Trimming for Y-Axis |

|----------|----------------------------------|

|----------|----------------------------------|

## 4.6 GAIN\_Z (1Bh)

## 4.7 A\_IF\_CTRL1 (20h)

| PD1 | PD0 | DF1 | DF0 | ST | Zen | Yen | Xen |

|-----|-----|-----|-----|----|-----|-----|-----|

|-----|-----|-----|-----|----|-----|-----|-----|

| PD1, PD0 | Power Down Control (00: power-down mode; 01: device on)                                                    |

|----------|------------------------------------------------------------------------------------------------------------|

| DF1, DF0 | Decimation Factor Control (00: decimate by 128; 01: decimate by 64; 10: decimate by 32; 11: decimate by 8) |

| ST       | Self Test Enable (0: normal mode; 1: self-test active)                                                     |

| Zen      | Z-axis enable (0: axis off; 1: axis on)                                                                    |

| Yen      | Y-axis enable (0: axis off; 1: axis on)                                                                    |

| Xen      | X-axis enable (0: axis off; 1: axis on)                                                                    |

## 4.8 A\_IF\_CTRL2 (21h)

| FS | х | х | воот | IEN | DRDY | SIM | DAS |

|----|---|---|------|-----|------|-----|-----|

| FS   | Full Scale selection (0: +/- 2g; 1: +/- 6g)                                     |

|------|---------------------------------------------------------------------------------|

| воот | Reboot memory content                                                           |

| IEN  | Interrupt ENable<br>(0: data ready on RDY pad; 1: int req on RDY pad)           |

| DRDY | Enable Data-Ready generation                                                    |

| SIM  | SPI Serial Interface Mode selection (0: 4-wire interface; 1: 3-wire interface)  |

| DAS  | Data Alignement Selection (0: 12 bit right justified; 1: 16 bit left justified) |

## 4.9 WAKE\_UP\_CFG (23h)

| _ |     |     |     |     |     |     |     |

|---|-----|-----|-----|-----|-----|-----|-----|

| х | LIR | MZH | MZL | MYH | MYL | MXH | MXL |

| LIR | Latch interrupt request (1: interrupt request latched)                                          |

|-----|-------------------------------------------------------------------------------------------------|

| MZH | Mask Z High Interrupt (1: enable int req on measured accel. value higher than preset threshold) |

| MZL | Mask Z Low Interrupt (1: enable int req on measured accel. value lower than preset threshold)   |

| MYH | Mask Y High Interrupt (1: enable int req on measured accel. value higher than preset threshold) |

| MYL | Mask Y Low Interrupt (1: enable int req on measured accel. value lower than preset threshold)   |

| МХН | Mask X High Interrupt (1: enable int req on measured accel. value higher than preset threshold) |

| MXL | Mask X Low Interrupt (1: enable int req on measured accel. value lower than preset threshold)   |

## 4.10 WAKE\_UP\_SOURCE (24h)

|   | 1.4 | 711 | 71 | VIII | M  | VII | VI |

|---|-----|-----|----|------|----|-----|----|

| Х | IA  | ZH  | ZL | ΥĦ   | ΥL | XH  | XL |

|   |     |     |    |      |    |     |    |

| IA  | Interrupt Active |

|-----|------------------|

| MZH | Z High           |

| MZL | Z Low            |

| MYH | Y High           |

| MYL | Y Low            |

| MXH | X High           |

| MXL | X Low            |

## 4.11 WAKE\_UP\_ACK (25h)

Reading at this address resets the  $\ensuremath{\mathbf{WAKE\_UP\_SOURCE}}$  register.

## 4.12 A\_IF\_STATUS (27h)

| ZYXOR ZOR YOR XOR | ZYXDA ZDA | A YDA XDA |

|-------------------|-----------|-----------|

|-------------------|-----------|-----------|

| ZYXOR | X, Y and Z axis Data Overrun       |  |

|-------|------------------------------------|--|

| ZOR   | Z axis Data Overrun                |  |

| YOR   | Y axis Data Overrun                |  |

| XOR   | Y axis Data Overrun                |  |

| ZYXDA | X, Y and Z axis new Data Available |  |

| ZDA   | Z axis new Data Available          |  |

| YDA   | Y axis new Data Available          |  |

| XDA   | X axis new Data Available          |  |

## 4.13 OUTX\_L (28h)

| XD7 XD6 XD5 | XD4 | XD3 | XD2 | XD1 | XD0 |  |

|-------------|-----|-----|-----|-----|-----|--|

|-------------|-----|-----|-----|-----|-----|--|

| XD7, XD0 |

|----------|

|----------|

## 4.14 OUTX\_H (29h)

When reading the register in "12 bit right justified" mode the most significant bits (7:4) are replaced with bit 3 (i.e. XD15-XD12=XD11, XD11, XD11, XD11).

| XD15 | XD14  | XD13 | XD12  | XD11  | XD10 | ΧDa | XD8 |

|------|-------|------|-------|-------|------|-----|-----|

| ADIO | AD IT | ADIO | ND 12 | AD II | ADIO | AD3 | AD0 |

| XD15, XD8 | X axis acceleration data MSb |

|-----------|------------------------------|

|-----------|------------------------------|

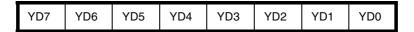

## 4.15 OUTY\_L (2Ah)

| Y axis acceleration data LSb | YD0 |

|------------------------------|-----|

|------------------------------|-----|

## 4.16 OUTY\_H (2Bh)

When reading the register in "12 bit right justified" mode the most significant bits (7:4) are replaced with bit 3 (i.e. YD15-YD12=YD11, YD11, YD11, YD11).

| YD15 | YD14 | YD13 | YD12 | YD11 | YD10 | YD9 | YD8 |

|------|------|------|------|------|------|-----|-----|

| YD15, YD8 | Y axis acceleration data MSb |

|-----------|------------------------------|

|-----------|------------------------------|

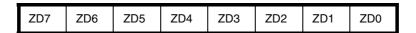

## 4.17 OUTZ\_L (2Ch)

| ZD7, ZD0 |

|----------|

|----------|

## 4.18 OUTZ\_H (2Dh)

When reading the register in "12 bit right justified" mode the most significant bits (7:4) are replaced with bit 3 (i.e. ZD15-ZD12=ZD11, ZD11, ZD11, ZD11).

|      | •    |      |      |      |      |     |     |

|------|------|------|------|------|------|-----|-----|

| ZD15 | ZD14 | ZD13 | ZD12 | ZD11 | ZD10 | ZD9 | ZD8 |

| ZD15, ZD8 | Z axis acceleration data MSb |

|-----------|------------------------------|

|-----------|------------------------------|

## 4.19 THS\_L (2Eh)

| THS15 | THS14 | THS13 | THS12 | THS11 | THS10 | THS9 | THS8 |

|-------|-------|-------|-------|-------|-------|------|------|

| THS15, THS8 | Inertial Wake Up Acceleration Threshold Lsb |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

## 4.20 THS\_H (2Fh)

| THS15 TH | HS14 THS13 | THS12 | THS11 | THS10 | THS9 | THS8 |

|----------|------------|-------|-------|-------|------|------|

|----------|------------|-------|-------|-------|------|------|

|--|

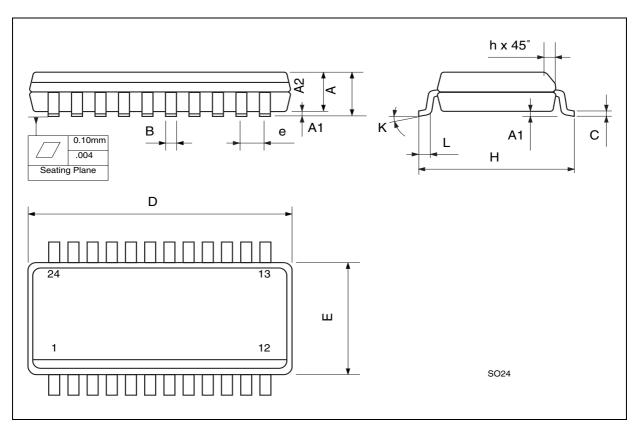

| DIM. |       | mm   |           | inch    |       |        |  |

|------|-------|------|-----------|---------|-------|--------|--|

|      | MIN.  | TYP. | MAX.      | MIN.    | TYP.  | MAX.   |  |

| Α    | 2.35  |      | 2.65      | 0.093   |       | 0.104  |  |

| A1   | 0.10  |      | 0.30      | 0.004   |       | 0.012  |  |

| A2   |       |      | 2.55      |         |       | 0.100  |  |

| В    | 0.33  |      | 0.51      | 0.013   |       | 0.0200 |  |

| С    | 0.23  |      | 0.32      | 0.009   |       | 0.013  |  |

| D    | 15.20 |      | 15.60     | 0.598   |       | 0.614  |  |

| Е    | 7.40  |      | 7.60      | 0.291   |       | 0.299  |  |

| е    |       | 1.27 |           |         | 0,050 |        |  |

| Н    | 10.0  |      | 10.65     | 0.394   |       | 0.419  |  |

| h    | 0.25  |      | 0.75      | 0.010   |       | 0.030  |  |

| k    |       | 0    | ° (min.), | 8° (max | .)    |        |  |

| L    | 0.40  |      | 1.27      | 0.016   |       | 0.050  |  |

## OUTLINE AND MECHANICAL DATA

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics.

All other names are the property of their respective owners

© 2004 STMicroelectronics - All rights reserved

#### STMicroelectronics GROUP OF COMPANIES

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States www.st.com

SUNSTAR商斯达实业集团是集研发、生产、工程、销售、代理经销 、技术咨询、信息服务等为一体的高 科技企业,是专业高科技电子产品生产厂家,是具有10多年历史的专业电子元器件供应商,是中国最早和 最大的仓储式连锁规模经营大型综合电子零部件代理分销商之一,是一家专业代理和分銷世界各大品牌IC 芯片和電子元器件的连锁经营綜合性国际公司。在香港、北京、深圳、上海、西安、成都等全国主要电子 市场设有直属分公司和产品展示展销窗口门市部专卖店及代理分销商,已在全国范围内建成强大统一的供 货和代理分销网络。 我们专业代理经销、开发生产电子元器件、集成电路、传感器、微波光电元器件、工 控机/DOC/DOM电子盘、专用电路、单片机开发、MCU/DSP/ARM/FPGA软件硬件、二极管、三极管、模 块等,是您可靠的一站式现货配套供应商、方案提供商、部件功能模块开发配套商。专业以现代信息产业 (计算机、通讯及传感器)三大支柱之一的传感器为主营业务,专业经营各类传感器的代理、销售生产、 网络信息、科技图书资料及配套产品设计、工程开发。我们的专业网站——中国传感器科技信息网(全球 传感器数据库)www.SENSOR-IC.COM 服务于全球高科技生产商及贸易商,为企业科技产品开发提供技 术交流平台。欢迎各厂商互通有无、交换信息、交换链接、发布寻求代理信息。欢迎国外高科技传感器、 变送器、执行器、自动控制产品厂商介绍产品到 中国,共同开拓市场。本网站是关于各种传感器-变送器-仪器仪表及工业自动化大型专业网站,深入到工业控制、系统工程计 测计量、自动化、安防报警、消费电 子等众多领域, 把最新的传感器-变送器-仪器仪表买卖信息, 最新技术供求, 最新采购商, 行业动态, 发展方 向,最新的技术应用和市场资讯及时的传递给广大科技开发、科学研究、产品设计人员。本网站已成功为 石油、化工、电力、医药、生物、航空、航天、国防、能源、冶金、电子、工业、农业、交通、汽车、矿 山、煤炭、纺织、信息、通信、IT、安防、环保、印刷、科研、气象、仪器仪表等领域从事科学研究、产 品设计、开发、生产制造的科技人员、管理人员 、和采购人员提供满意服务。 我公司专业开发生产、代 理、经销、销售各种传感器、变送器、敏感元器件、开关、执行器、仪器仪表、自动化控制系统: 专门从 事设计、生产、销售各种传感器、变送器、各种测控仪表、热工仪表、现场控制器、计算机控制系统、数 据采集系统、各类环境监控系统、专用控制系统应用软件以及嵌入式系统开发及应用等工作。如热敏电阻、 压敏电阻、温度传感器、温度变送器、湿度传感器、 湿度变送器、气体传感器、 气体变送器、压力传感 器、 压力变送、称重传感器、物(液)位传感器、物(液)位变送器、流量传感器、 流量变送器、电流 (压) 传感器、溶氧传感器、霍尔传感器 、图像传感器、超声波传感器、位移传感器、速度传感器、加速 度传感器、扭距传感器、红外传感器、紫外传感器、 火焰传感器、激光传感器、振动传感器、轴角传感器、 光电传感器、接近传感器、干簧管传感器、继电器传感器、微型电泵、磁敏(阻)传感器 、压力开关、接 近开关、光电开关、色标传感器、光纤传感器、齿轮测速传感器、 时间继电器、计数器、计米器、温控仪、 固态继电器、调压模块、电磁铁、电压表、电流表等特殊传感器。 同时承接传感器应用电路、产品设计 和自动化工程项目。

#### 更多产品请看本公司产品专用销售网站:

商斯达中国传感器科技信息网: http://www.sensor-ic.com/

商斯达工控安防网: http://www.pc-ps.net/

商斯达电子 元器件网: http://www.sunstare.com/

商斯达微波光电产品网:HTTP://www.rfoe.net/

商斯达消费电子产品网://www.icasic.com/

商斯达军工产品网:http://www.junpinic.com/

商斯达实业科技产品网://www.sunstars.cn/传感器销售热线:

地址:深圳市福田区福华路福庆街鸿图大厦 1602 室

电话: 0755-83607652 83376489 83376549 83370250 83370251 82500323

传真: 0755-83376182 (0) 13902971329 MSN: SUNS8888@hotmail.com

邮编: 518033 E-mail:szss20@163.com QQ: 195847376

深圳赛格展销部: 深圳华强北路赛格电子市场 2583 号 电话: 0755-83665529 25059422

技术支持: 0755-83394033 13501568376

欢迎索取免费详细资料、设计指南和光盘 ; 产品凡多,未能尽录,欢迎来电查询。

北京分公司:北京海淀区知春路 132 号中发电子大厦 3097 号

TEL: 010-81159046 82615020 13501189838 FAX: 010-62543996

上海分公司: 上海市北京东路 668 号上海賽格电子市场 D125 号

TEL: 021-28311762 56703037 13701955389 FAX: 021-56703037

西安分公司: 西安高新开发区 20 所(中国电子科技集团导航技术研究所)

西安劳动南路 88 号电子商城二楼 D23 号

TEL: 029-81022619 13072977981 FAX:029-88789382