# **OKI** Semiconductor

# MSM6262-xx

## DOT MATRIX LCD CONTROLLER WITH 48-DOT COMMON DRIVER

#### GENERAL DESCRIPTION

The MSM6262-xx is a dot matrix LCD controller which is fabricated by OKI's low power consumption CMOS silicon gate technology. In combination with 8-bit microcontroller, the MSM6262-xx can control the dot matrix character type LCD module.

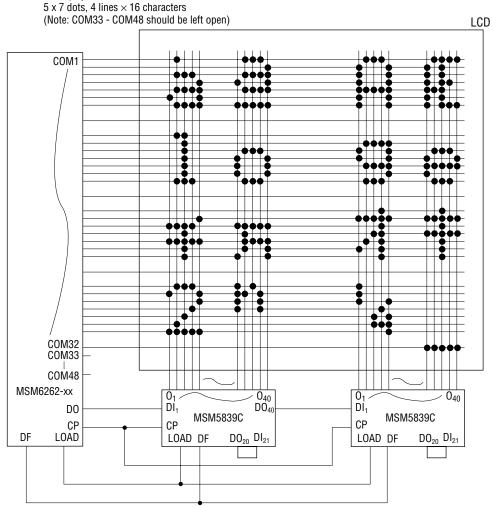

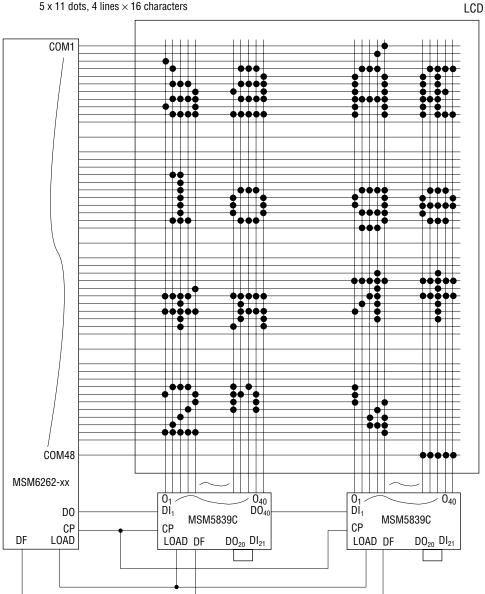

The MSM6262-xx is provided with a serial data transfer output. So, a maximum of 160 characters can be controlled by combining this device with the MSM5259, MSM5839C, or MSM5260.

The MSM6262-xx is recommended for use in an LCD panel which is capable of displaying 81 to 160 characters. If an LCD panel of which display capacity is 80 characters or less is used, the MSM6222B-xx is recommended.

The MSM6262-xx is best suited to be used as an LCD controller for applications such as electronic typewriters, POS system terminals, and data banks.

#### **FEATURES**

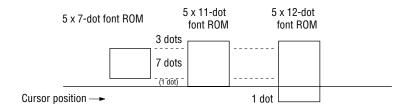

- Dot matrix LCD controller/driver for three different font configuration (5 x 7 dots, 5 x 11 dots and 5 x 12 dots)

- Up to 160 characters can be controlled (Display data RAM ... 160 x 9-bit)

- On-chip character generator ROM (CGROM) for 256 different characters

5 x 7 dots ... 128 characters

5 x 11 dots ... 96 characters

5 x 12 dots ... 32 characters

On-chip character generator RAM (CGRAM) (32 x 8-bit)

5 x 8 dots ... 4 kinds

5 x 12 dots ... 2 kinds

- Easy interface with Z80, 6809, 80C49, and 80C51

- Underline function

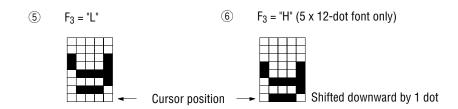

- Shift function for g, i, p, q and y

- Selectable driving duty

| Duty | Font Configuration (dots) | <b>Cursor Display</b> | Display (characters x lines) |

|------|---------------------------|-----------------------|------------------------------|

| 1/16 | 5 x 7                     | Available             | 80 x 2                       |

| 1/24 | 5 x 11                    | Available             | 80 x 2                       |

| 1/32 | 5 x 7                     | Available             | 40 x 4                       |

| 1/48 | 5 x 11                    | Available             | 40 x 4                       |

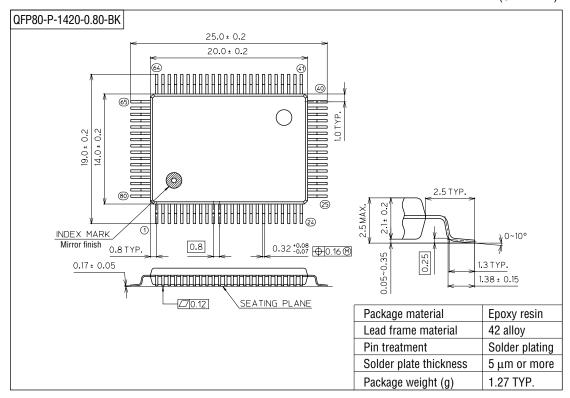

• Package:

80-pin plastic QFP (QFP80-P-1420-0.80-BK) (Product name: MSM6262-xxGS-BK)

xx indicates code number.

This version: Nov. 1997

Previous version: Mar. 1996

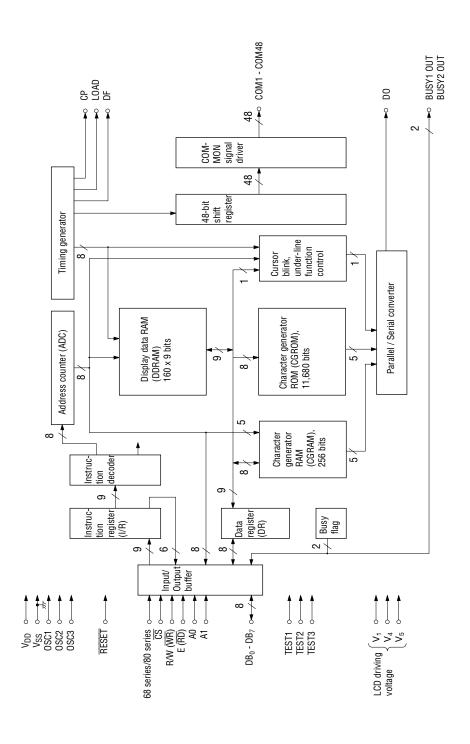

# **BLOCK DIAGRAM**

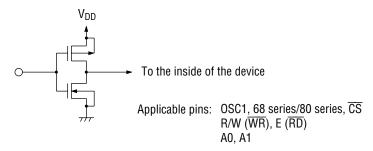

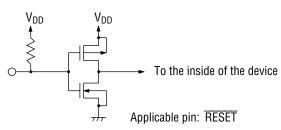

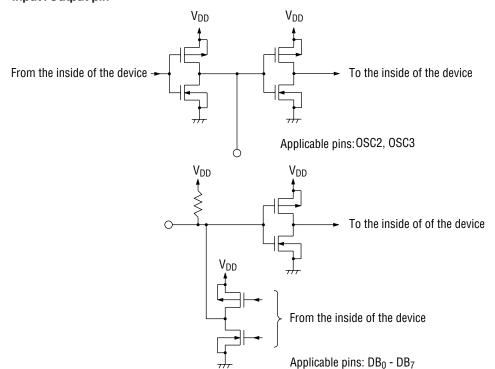

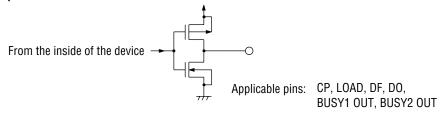

# INPUT AND OUTPUT CONFIGURATION

## Input pin

## Input /Output pin

## **Output pin**

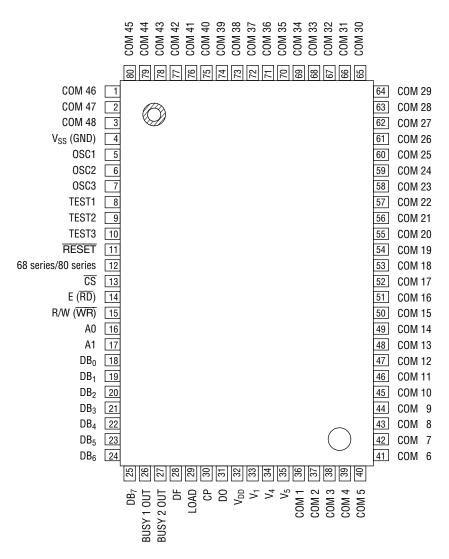

# **PIN CONFIGURATION (TOP VIEW)**

80-Pin Plastic QFP

# **PIN DESCRIPTIONS**

| Symbol                                           | Туре | Description                                                                    |

|--------------------------------------------------|------|--------------------------------------------------------------------------------|

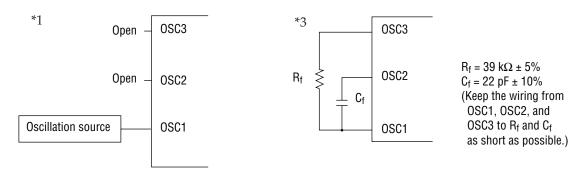

| OSC1                                             | 1/0  | Clock oscillating pins required for internal operation upon receipt            |

| OSC2, OSC3                                       |      | of the LCD drive signal and CPU instruction.                                   |

| RESET                                            | I    | Reset pin                                                                      |

| 68 series/80 series                              | l    | Selection pin for either 68 series CPU or 80 series CPU                        |

| CS                                               | 1    | Chip select pin. By setting $\overline{\text{CS}}$ at "L" level, MSM6262-xx    |

|                                                  |      | is set at selecting condition.                                                 |

| R/W (WR)                                         | I    | R/W pin of 68 series CPU shall be connected to this pin,                       |

|                                                  |      | while $\overline{\text{WR}}$ pin shall be connected to this pin in the case of |

|                                                  |      | 80 series CPU.                                                                 |

| E (RD)                                           | 1    | E pin of 68 series CPU shall be connected to this pin,                         |

|                                                  |      | while $\overline{RD}$ pin shall be connected to this pin in the case of        |

|                                                  |      | 80 series CPU.                                                                 |

| A0, A1                                           | I    | The address bus of CPU shall be connected to these pins.                       |

|                                                  |      | Instruction code is set by these pins.                                         |

| DB <sub>0</sub> - DB <sub>7</sub>                | 1/0  | The data bus of CPU shall be connected to these pins. These                    |

| 01                                               |      | pins are used to set the data of the instruction or to read                    |

|                                                  |      | the data.                                                                      |

| TEST1 - TEST3                                    | 1    | Test pins. Normally these pins should be set at V <sub>SS</sub> or             |

| 12011 12010                                      | '    | open.                                                                          |

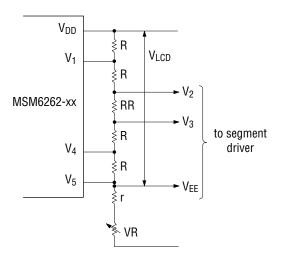

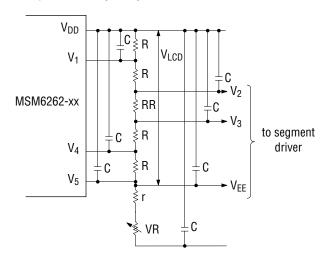

| $V_{DD}$ , $V_{SS}$                              |      |                                                                                |

| vnn¹ ∧22                                         |      | Voltage supply pins. V <sub>DD</sub> is also used for the common               |

|                                                  |      | bias voltage level to drive the LCD.                                           |

| V <sub>1</sub> , V <sub>4</sub> , V <sub>5</sub> |      | Common bias voltage input pins to drive the LCD                                |

|                                                  | 0    | Serial data output pin for SEGMENT drivers                                     |

| CP                                               | 0    | Clock pulse output pin. The clock output from this pin                         |

|                                                  |      | enables the character pattern data, which is output from                       |

|                                                  |      | DO, to input to the SEGMENT drivers (MSM5839C or MSM5259).                     |

| LOAD                                             | 0    | Load signal output pin. The character pattern data to                          |

|                                                  |      | the SEGMENT drivers, which was output from DO and                              |

|                                                  |      | CP, is loaded to the LCD output of the SEGMENT                                 |

|                                                  |      | drivers, synchronized with the COMMON signal.                                  |

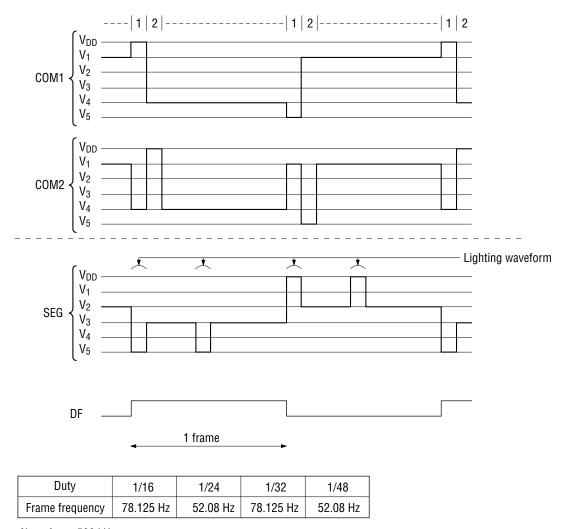

| DF                                               | 0    | B-type AC signal output pin to drive the LCD                                   |

| COM1 - COM48                                     | 0    | COMMON signal output pins to drive the LCD                                     |

| BUSY1 OUT                                        | 0    | This pin shows the internal condition of MSM6262-xx.                           |

|                                                  |      | "H" shows that MSM6262-xx is in internal operation,                            |

|                                                  |      | while "L" shows that MSM6262-xx is ready to receive                            |

|                                                  |      | the instruction from the CPU.                                                  |

| BUSY2 OUT                                        | 0    | This pin shows that MSM6262-xx is in internal operation                        |

| 50012 001                                        |      | based on the instruction from the CPU, or MSM6262-xx                           |

|                                                  |      |                                                                                |

|                                                  |      | is in display revising operation based on the instruction from the CPU.        |

|                                                  |      |                                                                                |

|                                                  |      | "H" shows that MSM6262-xx is in internal operation,                            |

|                                                  |      | while "L" shows that the display on the LCD has been                           |

|                                                  |      | established and the MSM6262-xx is ready to receive an                          |

|                                                  |      | instruction.                                                                   |

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter                         | Symbol                                           | Condition                                   | Rating                                           | Unit | Applicable Pin                                                                                   |

|-----------------------------------|--------------------------------------------------|---------------------------------------------|--------------------------------------------------|------|--------------------------------------------------------------------------------------------------|

| Supply Voltage                    | $V_{DD}$                                         | Ta = 25°C, V <sub>DD</sub> -V <sub>SS</sub> | -0.3 to +7.0                                     | V    | V <sub>DD</sub> , V <sub>SS</sub>                                                                |

| Supply Voltage<br>for Driving LCD | V <sub>1</sub> , V <sub>4</sub> , V <sub>5</sub> | Ta = 25°C                                   | V <sub>DD</sub> – 12 to<br>V <sub>DD</sub> + 0.3 | V    | V <sub>1</sub> , V <sub>4</sub> , V <sub>5</sub>                                                 |

| Input Voltage                     | V <sub>IN</sub>                                  | Ta = 25°C                                   | –0.3 to V <sub>DD</sub> + 0.3                    | V    | OSC1, RESET 68 series / 80 series CS, A0, A1, R/W (WR) E (RD), DB <sub>0</sub> - DB <sub>7</sub> |

| Power Dissipation                 | $P_{D}$                                          | Ta = 25°C                                   | 500                                              | mW   | _                                                                                                |

| Storage Temperature               | T <sub>STG</sub>                                 |                                             | −55 to +125                                      | °C   |                                                                                                  |

# RECOMMENDED OPERATING CONDITOINS

| Parameter             | Symbol           | Condition Range                                |            | Unit | Applicable Pin          |  |

|-----------------------|------------------|------------------------------------------------|------------|------|-------------------------|--|

| Supply Voltage        | $V_{DD}$         | _                                              | 4.5 to 5.5 | V    | V <sub>DD,</sub> GND    |  |

|                       | V <sub>LCD</sub> | 1/5 bias, V <sub>DD</sub> –V <sub>5</sub>      | 3.0 to 11  | V    |                         |  |

| LCD Driving Voltage   |                  | 1/6, 1/7 bias, V <sub>DD</sub> -V <sub>5</sub> | 4.0 to 11  | V    | $V_{DD,} V_1, V_4, V_5$ |  |

|                       |                  | 1/8 bias, V <sub>DD</sub> –V <sub>5</sub>      | 4.5 to 11  | V    |                         |  |

| Operating Temperature | T <sub>op</sub>  | _                                              | -20 to +75 | °C   |                         |  |

Note: For bias, refer to \*3 in the section "DC Characteristics".

## **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics**

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, Ta = -20 \text{ to } +75^{\circ}\text{C})$

|                        | (-86              |                                                               | ( 00                                 | - BB - 110 - 10 - 110 - 1 |      |                      |      |                                                  |

|------------------------|-------------------|---------------------------------------------------------------|--------------------------------------|---------------------------|------|----------------------|------|--------------------------------------------------|

| Parameter              | Symbol            | Coi                                                           | ndition                              | Min.                      | Тур. | Max.                 | Unit | Applicable Pin                                   |

| "H" Input Voltage      | V <sub>IH1</sub>  |                                                               |                                      | 2.2                       |      | V <sub>DD</sub>      | V    | CS, R/W (WR)<br>E (RD), A0, A1                   |

| "L" Input Voltage      | V <sub>IL1</sub>  |                                                               |                                      | -0.3                      | _    | 0.7                  | V    | DB <sub>0</sub> - DB <sub>7</sub>                |

| "H" Output Voltage     | V <sub>OH1</sub>  | I <sub>0</sub> = -                                            | -250 μΑ                              | 2.4                       | _    | _                    | V    | DB <sub>0</sub> - DB <sub>7</sub>                |

| "L" Output Voltage     | V <sub>OL1</sub>  | I <sub>0</sub> =                                              | 1.8 mA                               | _                         | _    | 0.4                  | V    | 000-007                                          |

| "H" Input Voltage      | V <sub>IH2</sub>  |                                                               |                                      | $V_{DD}$ -0.8             |      | $V_{DD}$             | V    | OSC1, RESET                                      |

| "L" Input Voltage      | V <sub>IL2</sub>  |                                                               |                                      | -0.3                      | _    | 0.8                  | V    | 68series/80series                                |

| "H" Output Voltage     | V <sub>OH2</sub>  | I <sub>0</sub> = -                                            | –500 μΑ                              | $0.85\ V_{DD}$            |      |                      | V    | DO, LOAD, DF                                     |

| "L" Output Voltage     | V <sub>0L2</sub>  | I <sub>0</sub> =                                              | 500 μΑ                               |                           |      | 0.15 V <sub>DD</sub> | V    | , ,                                              |

| "H" Output Voltage     | V <sub>OH3</sub>  | I <sub>0</sub> = -                                            | –1 mA                                | $0.85\ V_{DD}$            |      |                      | V    | CP                                               |

| "L" Output Voltage     | V <sub>0L3</sub>  | I <sub>0</sub> =                                              | 1 mA                                 | <del></del>               |      | 0.15 V <sub>DD</sub> | V    | OF                                               |

| "H" Output Voltage     | V <sub>OH4</sub>  | I <sub>0</sub> = -                                            | –100 μΑ                              | 2.4                       |      |                      | V    | BUSY1 OUT                                        |

| "L" Output Voltage     | V <sub>0L4</sub>  | I <sub>0</sub> =                                              | I <sub>0</sub> = 1.6 mA              |                           |      | 0.4                  | V    | BUSY2 OUT                                        |

| COM Voltage Drop       | V <sub>COM</sub>  | $I_0 = \pm 50 \mu\text{A}$ *1                                 |                                      |                           |      | 2.9                  | V    | COM1 - COM48                                     |

| "H" Input Current      | I <sub>ILH1</sub> | V <sub>IN</sub> =                                             | $V_{IN} = V_{DD}$                    |                           | _    | 1                    | μΑ   | CS, R/W (WR)<br>E (RD), A0, A1                   |

| "L" Input Current      | I <sub>ILL1</sub> | V <sub>IN</sub> =                                             | V <sub>SS</sub>                      |                           | _    | -1                   | μΑ   | E (RD), AÒ, AÍ<br>OSC1, 68series/<br>80series    |

| Supply Current         | I <sub>DD1</sub>  | $V_{DD}$ = 5 V, *2<br>$f_{OSC}$ = 500 kHz<br>(RC oscillation) |                                      | _                         | _    | 1.5                  | mA   | V                                                |

| Supply Current         | I <sub>DD2</sub>  | V <sub>DD</sub> =<br>f <sub>IN</sub> = 5<br>(externa          | 5 V, *2<br>00 kHz<br>al oscillation) |                           |      | 1.5                  | mA   | V <sub>DD</sub>                                  |

|                        |                   | *3                                                            | 1/5 bias                             | 3.0                       |      | 11                   | V    |                                                  |

| LCD Driving<br>Voltage | V <sub>LCD</sub>  |                                                               | 1/6-1/7<br>bias                      | 4.0                       |      | 11                   | V    | V <sub>1</sub> , V <sub>4</sub> , V <sub>5</sub> |

|                        |                   |                                                               | 1/8 bias                             | 4.5                       | _    | 11                   | V    |                                                  |

| "H" Input Current      | I <sub>ILH2</sub> | V <sub>IN</sub>                                               | = V <sub>DD</sub>                    |                           |      | 2                    | μA   | DECET                                            |

| "L" Input Current      | I <sub>ILL2</sub> | V <sub>IN</sub> = V <sub>5</sub>                              | $SS,V_{DD} = 5 V$                    | -8                        | -20  | -60                  | μΑ   | RESET                                            |

|                        | _                 | _                                                             |                                      |                           | _    |                      | _    |                                                  |

<sup>\*1.</sup> This is applicable to the voltage drop which is caused between  $V_{DD}$ ,  $V_1$ ,  $V_4$ ,  $V_5$  and COM1 - COM48 when a current of 50  $\mu$ A is flowed in/out to/from all of COM1 - COM48. (When the output level is either  $V_{DD}$  or  $V_1$ , it should be applied only when the current flows in. When the output level is either  $V_4$  or  $V_5$ , it should be applied only when the current flows in.

In this case, +5V is applied to  $V_{DD}$  and  $V_1$ , while -6 V is applied to  $V_4$  and  $V_5$ .)

<sup>\*2.</sup> This is applicable to the current which flows in to  $V_{DD}$  under following conditions.  $V_{DD} = 5 \text{ V}$ ,  $V_{SS} = 0 \text{ V}$ ,  $V_1 = 2.8 \text{ V}$ ,  $V_4 = -3.8 \text{ V}$ ,  $V_5 = -6 \text{ V}$ , No load, No interface with CPU

<sup>\*3.</sup>  $V_1$  to  $V_5$  should be set at as follows.

| No. of lines    |                                | nes                                | 4 lines                            |                                    |  |  |

|-----------------|--------------------------------|------------------------------------|------------------------------------|------------------------------------|--|--|

| Font (N)<br>Pin | 5 x 8                          | 5 x 12                             | 5 x 8                              | 5 x 12                             |  |  |

| V <sub>1</sub>  | $V_{DD} - \frac{1}{5} V_{LCD}$ | $V_{DD} - \frac{1}{6} V_{LCD}$     | $V_{DD} - \frac{1}{7} V_{LCD}$     | $V_{DD} - \frac{1}{8} V_{LCD}$     |  |  |

| $V_4$           | $V_{DD} - \frac{4}{5} V_{LCD}$ | $V_{DD} - \frac{5}{6} V_{LCD}$     | $V_{DD} - \frac{6}{7} V_{LCD}$     | $V_{DD} - \frac{7}{8} V_{LCD}$     |  |  |

| V <sub>5</sub>  | $V_{DD} - V_{LCD}$             | V <sub>DD</sub> – V <sub>LCD</sub> | V <sub>DD</sub> - V <sub>LCD</sub> | V <sub>DD</sub> – V <sub>LCD</sub> |  |  |

V<sub>LCD</sub> = LCD driving voltage

# **AC Characteristics**

$$(V_{DD} = 4.5 \text{ to } 5.5 \text{V} , Ta = -20 \text{ to } +75 ^{\circ}\text{C})$$

| Parameter             | Symbol            | Condition                           | Min. | Тур. | Max. | Unit | Applicable Pin                    |

|-----------------------|-------------------|-------------------------------------|------|------|------|------|-----------------------------------|

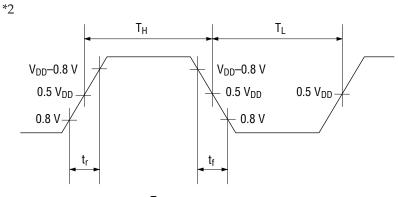

| Input Frequency       | f <sub>IN</sub>   | *1, *2                              | 300  | 500  | 700  | kHz  |                                   |

| Input Clock Duty      | f <sub>DUTY</sub> | *2                                  | 45   | 50   | 55   | %    | 0SC1                              |

| Input Clock Rise Time | t <sub>r</sub>    | *2                                  | _    | _    | 100  | ns   | 0301                              |

| Input Clock Fall Time | t <sub>f</sub>    | *2                                  |      |      | 100  | ns   |                                   |

| RC Oscillation        | 4                 | *3                                  | 200  | 500  | 700  | LII- | 0001 0000 0000                    |

| Frequency             | f <sub>CR</sub>   | 3                                   | 300  | 500  | 700  | kHz  | OSC1, OSC2, OSC3                  |

| "H" Input Current     | I <sub>ILH3</sub> | $V_{IN} = V_{DD}$                   | _    | _    | 1    | μΑ   |                                   |

| "L" Input Current     | I <sub>ILL3</sub> | $V_{IN} = V_{SS}$<br>$V_{DD} = 5 V$ | -45  | -120 | -250 | μА   | DB <sub>0</sub> - DB <sub>7</sub> |

$$f_{DUTY} = \frac{T_H}{T_H + T_L} \times 100\%$$

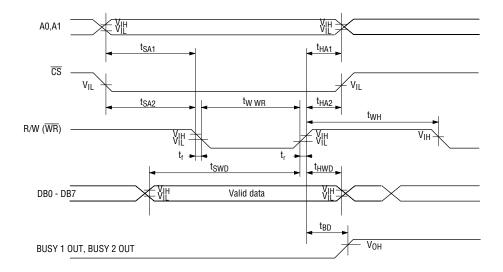

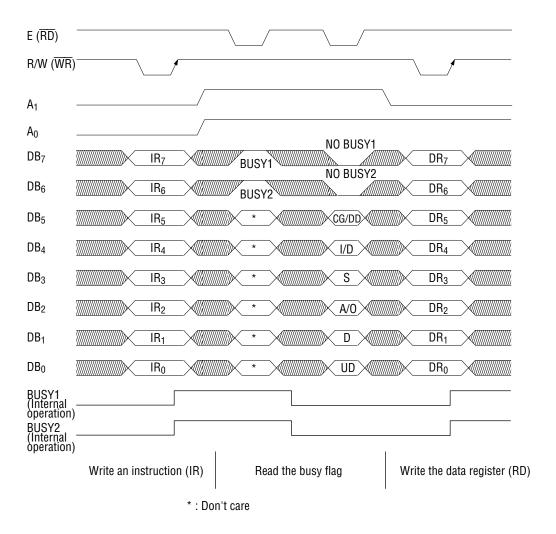

# **TIMING DIAGRAM**

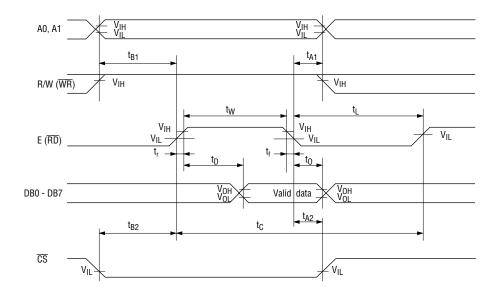

## Interface with 80 Series CPU

$(V_{DD} = 4.5 \text{ to } 5.5V, Ta = -20 \text{ to } +75^{\circ}C)$

| Parameter                        | Symbol           | Min. | Max. | Unit |

|----------------------------------|------------------|------|------|------|

| Address Set-up Time              | t <sub>SA1</sub> | 110  | _    | ns   |

| CS Set-up Time                   | t <sub>SA2</sub> | 100  | _    | ns   |

| WR "L" Pulse Width               | t <sub>WWR</sub> | 320  | _    | ns   |

| RD "L" Pulse Width               | t <sub>WRD</sub> | 320  | _    | ns   |

| WR, RD "H" Pulse Width           | t <sub>WH</sub>  | 210  | _    | ns   |

| Address Hold Time                | t <sub>HA1</sub> | 25   | _    | ns   |

| CS Hold Time                     | t <sub>HA2</sub> | 25   | _    | ns   |

| Data Set-up Time                 | t <sub>SWD</sub> | 300  | _    | ns   |

| Data Hold Time (Write operation) | t <sub>HWD</sub> | 20   | _    | ns   |

| WR, RD Fall Time                 | t <sub>f</sub>   |      | 25   | ns   |

| WR, RD Rise Time                 | t <sub>r</sub>   | _    | 25   | ns   |

| Data Delay Time                  | t <sub>SRD</sub> | _    | 190  | ns   |

| Data Hold Time (Read operation)  | t <sub>HRD</sub> | 0    | _    | ns   |

| Busy Output Delay Time           | t <sub>BD</sub>  | _    | 410  | ns   |

## Write operation

## **Read operation**

Refer to the DC Characteristics for the definition of  $V_{IH},\,V_{IL},\,V_{OH}$  and  $V_{OL}.$

# • Interface with Z80

$<sup>^{\</sup>star}$  A pull-up resistor of about 50  $k\Omega$  is required when the output of CPU becomes high impedance.

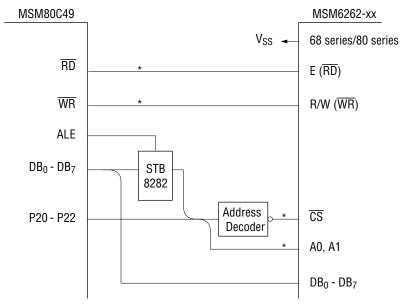

## • Interface with 80C49

$<sup>^{\</sup>star}$  A pull-up resistor of about 50 k $\Omega$  is required when the output of CPU becomes high impedance.

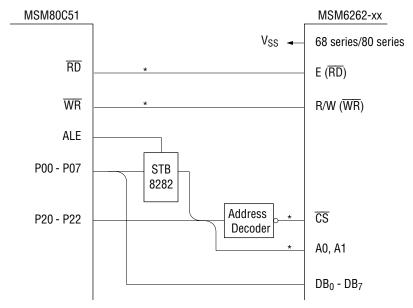

## • Interface with 80C51

$<sup>^{\</sup>star}$  A pull-up resistor of about 50  $k\Omega$  is required when the output of CPU becomes high impedance.

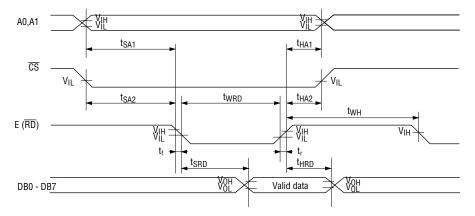

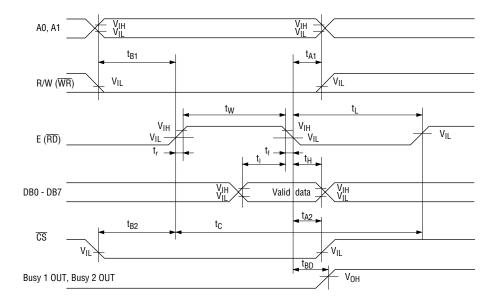

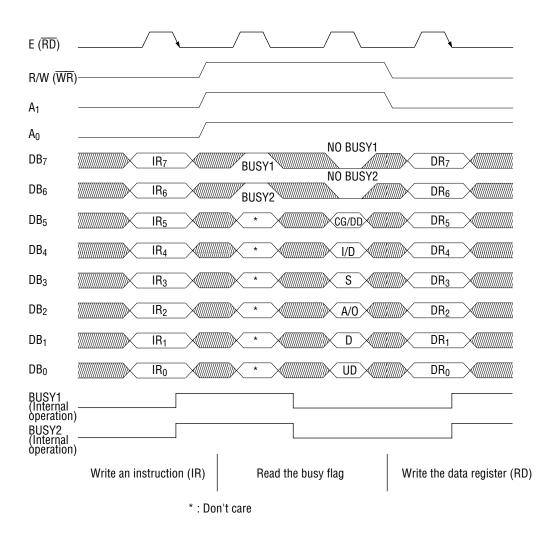

# Interface with 68 Series CPU

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Ta} = -20 \text{ to } +75^{\circ}\text{C})$

| Parameter                        | Symbol          | Min. | Max. | Unit |

|----------------------------------|-----------------|------|------|------|

| Cycle Time                       | t <sub>C</sub>  | 500  | _    | ns   |

| Address, R/W Set-up Time         | t <sub>B1</sub> | 100  | _    | ns   |

| CS Set-up Time                   | t <sub>B2</sub> | 90   | _    | ns   |

| E signal "H" Pulse Width         | t <sub>W</sub>  | 220  | _    | ns   |

| E signal "L" Pulse Width         | tL              | 210  | _    | ns   |

| Address, R/W Hold Time           | t <sub>A1</sub> | 20   | _    | ns   |

| CS Hold Time                     | t <sub>A2</sub> | 20   | _    | ns   |

| Data Set-up Time                 | t <sub>l</sub>  | 225  | _    | ns   |

| Data Hold Time (Write operation) | t <sub>H</sub>  | 30   | _    | ns   |

| E signal Rise Time               | t <sub>r</sub>  | _    | 25   | ns   |

| E signal Fall Time               | t <sub>f</sub>  | _    | 25   | ns   |

| Data Delay Time                  | t <sub>D</sub>  | _    | 180  | ns   |

| Data Hold Time (Read operation)  | t <sub>0</sub>  | 10   | _    | ns   |

| Busy Output Delay Time           | t <sub>BD</sub> | _    | 410  | ns   |

## Write operation

## **Read operation**

Refer to the DC Characteristics for the definition of  $V_{IH}$ ,  $V_{IL}$ ,  $V_{OH}$ , and  $V_{OL}$ .

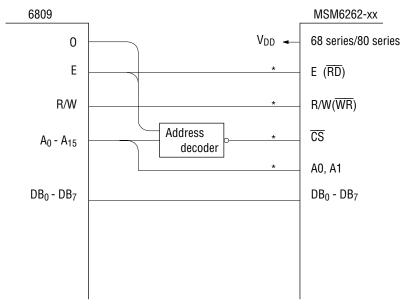

# • Interface with 6809

$<sup>^{\</sup>star}$  A pull-up resistor of about 50  $\text{k}\Omega$  is required when the output of CPU becomes high impedance.

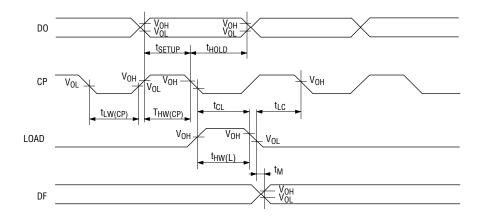

# **Interface with Segment Driver**

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Ta} = -20 \text{ to } +75^{\circ}\text{C}, f_{OSC} = 500 \text{ kHz})$

| Parameter               | Symbol              | Min. | Max. | Unit |

|-------------------------|---------------------|------|------|------|

| Clock "L" Pulse Width   | t <sub>LW(CP)</sub> | 400  | _    | ns   |

| Clock "H" Pulse Width   | t <sub>HW(CP)</sub> | 400  | _    | ns   |

| Do Set-up Time          | t <sub>SETUP</sub>  | 200  | _    | ns   |

| Do Hold Time            | t <sub>HOLD</sub>   | 200  | _    | ns   |

| LOAD, Clock Set-up Time | t <sub>CL</sub>     | 200  | _    | ns   |

| LOAD, Clock Hold Time   | t <sub>LC</sub>     | 100  | _    | ns   |

| LOAD, "H" Pulse Width   | t <sub>HW(L)</sub>  | 400  | _    | ns   |

| DF Delay Time           | t <sub>M</sub>      | -500 | 500  | ns   |

Refer to the DC Characteristics for the definition of  $V_{IH}$ ,  $V_{IL}$ ,  $V_{OH}$ , and  $V_{OL}$ .

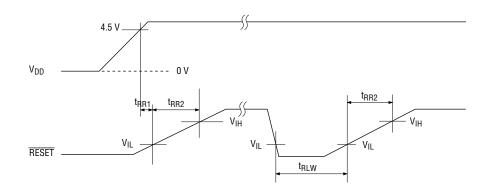

## **Reset Waveform**

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Ta} = -20 \text{ to } +75^{\circ}\text{C})$

| Parameter                         | Symbol           | Min. | Max. | Unit |

|-----------------------------------|------------------|------|------|------|

| "L" Input Time upon power on      | t <sub>RR1</sub> | 0.25 | _    | ms   |

| "L" Input Width when in operation | t <sub>RLW</sub> | 0.5  | _    | ms   |

| Rise Time                         | t <sub>RR2</sub> | 0.1  | 200  | ms   |

Refer to the DC Characteristics for the definition of  $V_{IH}$ ,  $V_{IL}$ ,  $V_{OH}$ , and  $V_{OL}$ .

#### **FUNCTIONAL DESCRIPTION**

## 1. Instruction Register (IR) and Data Register (DR)

The MSM6262-xx has two registers, instruction register (IR) and data register (DR). IR is used to store the address code or instruction code of display data RAM (DD RAM) or character generator RAM (CG RAM).

This register can be written by the CPU, but cannot be read out by the CPU.

DR is used to store the data to write into (or read out) the data to /from DD RAM or CG RAM. The data written into DR by the CPU is automatically written into the DD RAM or CG RAM. When an address code is written into IR, the data of the specified address is automatically transferred to the DR from either DD RAM or CG RAM. By having the CPU subsequently read the DR, it is possible to verify DD RAM or CG RAM data.

After the writing of DR by the CPU, the DD RAM or CG RAM of the next address is selected to be ready for the next CPU writing.

Likewise, after the reading operation of the CPU, DD RAM or CG RAM data of the next address is transferred to the DR, when CPU is ready for the next reading operation.

# 2. Busy Flag (BF)

When the output of BUSY 1 OUT is "H", MSM6262-xx is engaged in internal operation. When the output of BUSY 2 OUT is "H", it indicates that MSM6262-xx is engaged in internal operation or MSM6262-xx is engaged in the revising of the display starting line on the LCD. (Refer to the instruction table.)

When the output of BUSY 1 OUT is "H", any input of new instruction is ignored. So, before setting a new instruction, it is necessary to check whether BUSY 1 OUT and BUSY 2 OUT are at "L".

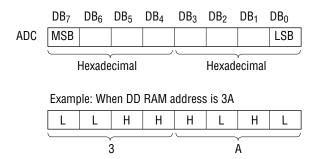

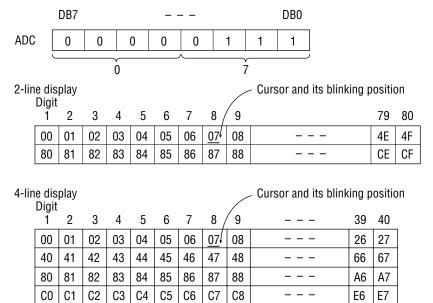

#### 3. Address Counter (ADC)

The address counter (ADC) allocates the address for the DD RAM and CG RAM write/read and also for the cursor display.

When the instruction code for a DD RAM address or CG RAM address setting is input to IR, after deciding whether it is DD RAM or CG RAM, the address counter code is transferred from IR to ADC. After writing (reading) the display data to (from) the DD RAM or CG RAM, the ADC increments (or decrements) by 1 automatically as its internal operation.

MSM6262-xx

## 4. Timing Generator Circuit

This circuit generates the timing signal for the internal operation by CPU's instruction as well as to operate the internal circuit of DD RAM, CG RAM, CG ROM and so forth. It also generates the transfer signal to the SEGMENT driver (MSM5839C or MSM5259).

The internal operation accessed by the CPU and internal operation for LCD display is independent.

So, a manipulation such as writing data from CPU to DD RAM will not have an influence such as display flickering upon any part other than the display part to which the data is written.

## 5. Display Data RAM (DD RAM)

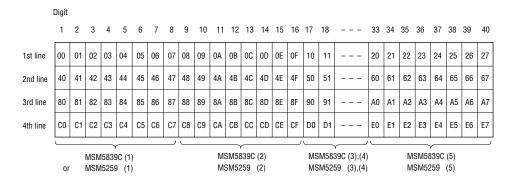

DD RAM is used to store the 8-bit character code (refer to Table 1) and 1-bit under-line data. The address of DD RAM corresponds to the display position on the LCD. The correspondence is described below.

DD RAM address (set to ADC) is described as hexadecimal.

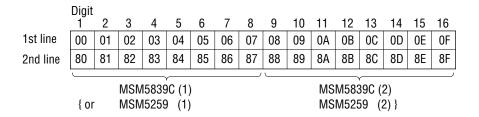

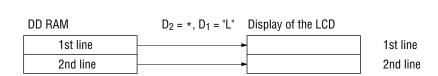

(1) Relation between DD RAM and display position in 2-line display mode

|          | Digit<br>1 | 2  | 3  | 4  | 5  | <br>79 | 80 — | - Display position |

|----------|------------|----|----|----|----|--------|------|--------------------|

| 1st line | 00         | 01 | 02 | 03 | 04 | <br>4E | 4F   | - DD RAM address   |

| 2nd line | 80         | 81 | 82 | 83 | 84 | <br>CE | CF + | (hexadecimal)      |

Note: The address of the last digit of the first line and the first digit of the second line does not have any continuity.

(2) When 2 pieces of MSM5389C(or MSM5259) are connected to MSM6262-xx, 32 characters can be displayed from the first digit to yhe 16th degit.

When the display is shifted by an instruction, the relation between the DD RAM address and the display position becomes as follows.

|                      | (Shif                                                                         | t to th | ne rig | ht)   |     |    |          |    |    |          |    |      |       |     |          |       |

|----------------------|-------------------------------------------------------------------------------|---------|--------|-------|-----|----|----------|----|----|----------|----|------|-------|-----|----------|-------|

|                      | Digit 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16                                  |         |        |       |     |    |          |    |    |          |    |      |       |     |          |       |

| 1st line             | 4F                                                                            | 00      | 01     | 02    | 03  | 04 | 05       | 06 | 07 | 08       | 09 | 0A   | 0B    | 00  | 0D       | 0E    |

| 2nd line             | CF                                                                            | 80      | 81     | 82    | 83  | 84 | 85       | 86 | 87 | 88       | 89 | 8A   | 8B    | 8C  | 8D       | 8E    |

|                      | Cr   00   01   02   03   04   03   00   87   88   89   8A   6B   8C   8D   8E |         |        |       |     |    |          |    |    |          |    |      |       |     |          |       |

|                      | MSM5839C (1) MSM5839C (2) MSM5259 (1) MSM5259 (2) }                           |         |        |       |     |    |          |    |    |          |    |      |       |     |          |       |

|                      | { or                                                                          |         |        |       |     |    |          |    |    |          |    |      |       |     |          |       |

|                      | { or                                                                          |         |        |       | (1) |    |          |    |    |          | MS | M525 | 59 (2 | 2)} |          |       |

| 1st line             | { or 01                                                                       |         |        |       |     |    | 07       | 08 | 09 | 0A       |    |      |       |     | 0F       | 10    |

| 1st line<br>2nd line |                                                                               |         | MSN    | 15259 | (1) |    | 07<br>87 | 08 | 09 | 0A<br>8A | MS | M525 | 59 (2 | 2)} | 0F<br>8F | 10 90 |

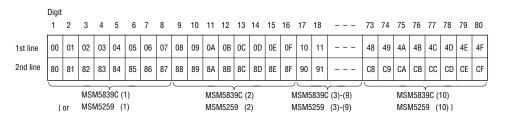

(3) The maximum DD RAM capacity of MSM6262-xx is for 160 characters. So, up to 10 pieces of MSM5839C (or MSM5259) can be connected in the case of 2-line display mode.

(4) Relation between the DD RAM and display position in 4-line display mode

|          | Digit |    |    |    |    |        |      |                                      |

|----------|-------|----|----|----|----|--------|------|--------------------------------------|

|          | 1     | 2  | 3  | 4  | 5  | <br>39 | 40 — | <ul> <li>Display position</li> </ul> |

| 1st line | 00    | 01 | 02 | 03 | 04 | <br>26 | 27 — |                                      |

| 2nd line | 40    | 41 | 42 | 43 | 44 | <br>66 | 67 — | DD RAM address                       |

| 3rd line | 80    | 81 | 82 | 83 | 84 | <br>A6 | A7 — | (hexadecimal)                        |

| 4th line | CO    | C1 | C2 | C3 | C4 | <br>E6 | E7 - |                                      |

Note: The address of the last digit of the previous line and the first digit of the next line does not have any continuity.

(5) When 2 pieces of MSM5839C (or MSM5259) are connected to MSM6262-xx, 64 characters can be displayed from the first digit to the 16th digit.

|          | Digit    |    |    |                |         |    |    |    |    |    |    |              |               |            |    |    |

|----------|----------|----|----|----------------|---------|----|----|----|----|----|----|--------------|---------------|------------|----|----|

|          | <u>1</u> | 2  | 3  | 4              | 5       | 6  | 7  | 8  | 9  | 10 | 11 | 12           | 13            | 14         | 15 | 16 |

| 1st line | 00       | 01 | 02 | 03             | 04      | 05 | 06 | 07 | 80 | 09 | 0A | 0B           | 00            | 0D         | 0E | 0F |

| 2nd line | 40       | 41 | 42 | 43             | 44      | 45 | 46 | 47 | 48 | 49 | 4A | 4B           | 4C            | 4D         | 4E | 4F |

| 3rd line | 80       | 81 | 82 | 83             | 84      | 85 | 86 | 87 | 88 | 89 | 8A | 8B           | 8C            | 8D         | 8E | 8F |

| 4th line | CO       | C1 | C2 | C3             | C4      | C5 | C6 | C7 | C8 | C9 | CA | СВ           | CC            | CD         | СВ | CF |

|          |          |    |    |                |         |    |    |    |    |    |    |              | $\overline{}$ |            |    |    |

|          | { or     |    |    | 15839<br>15259 |         | )  |    |    |    |    |    | M583<br>M525 |               | 2)<br>2) } |    |    |

|          | ( 01     |    |    |                | ( ' ( ' |    |    |    |    |    |    |              | ,             | -,,        |    |    |

When the display is shifted by an instruction, the relation between the DD RAM address and the display position becomes as follows.

|                      | (shift to right direction) |          |           |                |          |          |          |          |            |          |                |              |            |                  |          |          |

|----------------------|----------------------------|----------|-----------|----------------|----------|----------|----------|----------|------------|----------|----------------|--------------|------------|------------------|----------|----------|

|                      | Digit                      |          |           |                |          |          |          |          |            |          |                |              |            |                  |          |          |

|                      | <u>1</u>                   | 2        | 3         | 4              | 5        | 6        | 7        | 8        | 9          | 10       | 11             | 12           | 13         | 14               | 15       | 16       |

| 1st line             | 27                         | 00       | 01        | 02             | 03       | 04       | 05       | 06       | 07         | 08       | 09             | 0A           | 0B         | 0C               | 0D       | 0E       |

| 2nd line             | 67                         | 40       | 41        | 42             | 43       | 44       | 45       | 46       | 47         | 48       | 49             | 4A           | 4B         | 4C               | 4D       | 4E       |

| 3rd line             | A7                         | 80       | 81        | 82             | 83       | 84       | 85       | 86       | 87         | 88       | 89             | 8A           | 8B         | 8C               | 8D       | 8E       |

| 4th line             | E7                         | CO       | C1        | C2             | C3       | C4       | C5       | C6       | <b>C</b> 7 | C8       | C9             | CA           | СВ         | CC               | CD       | CE       |

|                      |                            |          |           |                |          |          |          |          |            |          |                |              |            |                  |          | $\equiv$ |

|                      |                            |          | _         | ١ .            | r _      |          |          | _        | ,          | r _      |                |              |            |                  |          |          |

|                      | ( 0 "                      |          |           | 15839          | )./      |          |          |          |            |          |                | M583         |            | 2)               |          |          |

|                      | { or                       |          |           | 15839<br>15259 |          |          |          |          |            |          |                | M583<br>M525 |            | 2)<br>2) }       |          |          |

| 1st line             | { or 01                    |          |           |                | )./      |          | 07       | 08       | 09         | 0A       |                |              |            |                  | 0F       | 10       |

| 1st line<br>2nd line |                            |          | MSN       | 15259          | (1)      |          | 07<br>47 | 08<br>48 | 09<br>49   | 0A<br>4A | MS             | M525         | 9 (2       | 2)}              | 0F<br>4F | 10 50    |

|                      | 01                         | 02       | MSN<br>03 | 04             | 05       | 06       |          |          |            | -        | MS<br>0B       | M525<br>0C   | 9 (2<br>0D | 2) }<br>0E       |          | -        |

| 2nd line             | 01                         | 02<br>42 | 03<br>43  | 04<br>44       | 05<br>45 | 06<br>46 | 47       | 48       | 49         | 4A       | MS<br>0B<br>4B | 0C<br>4C     | 0D<br>4D   | 2) }<br>0E<br>4E | 4F       | 50       |

(6) The maximum DD RAM capacity of MSM6262-xx is for 160 characters. So, up to 5 pieces of MSM5839C (or MSM5259) can be connected in the case of 4-line display mode.

## 6. Cursor/Blink Control Circuit

This is the circuit to control the generation of cursor and its blinking. This circuit is controlled by the program of the CPU.

The position of the cursor and its blink appears on the position according to the ADC contents, which correspond to the address of DD RAM. For example, when the ADC is set as "07" (hex.), the position of cursor and its blinking becomes as follows.

Note: Cursor display and blinking can be performed even when the CG RAM address is set in the ADC. So, it is necessary to disable the cursor display and blinking when the CG RAM address is set in the ADC.

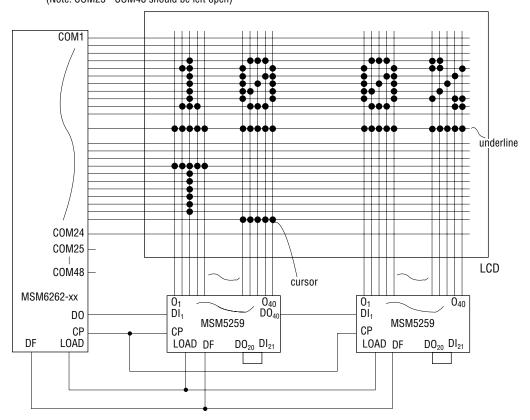

# 7. Underline Control Circuit

First, either underline display mode or underline blinking mode has to be set by the CPU. When an instruction to enable the underline function is input from the CPU, the cursor display shifts to the right direction (increment) or left direction (decrement). Display of underline appears (or disappears) on the same position where cursor was displayed. An input of "H" data enables the underline display, while an input of "L" data deletes the underline.

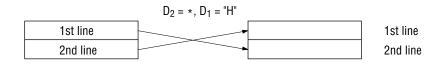

## 8. Character Generator ROM (CG ROM)

CG ROM stores the character pattern. MSM6262-xx has 128 kinds of  $5 \times 7$ -dot patterns, 96 kinds of  $5 \times 11$ -dot patterns and 32 kinds of  $5 \times 12$ -dot patterns. The character pattern corresponds to the character code which is written into the DD RAM.

The relation between 8-bit character code and character pattern is described in Table 1. When the 8-bit character code of CG ROM is written into the DD RAM, the character pattern of the corresponding character code of the CG ROM is displayed on the LCD position corresponding to the DD RAM address.

When all of the upper 4 bits of CG ROM code are "L", CG ROM can be switched to CG RAM.

Table 1 Character code and character pattern of Standard Code (MSM6262-04)

| Upper 4 bits  | 00       | 00           | 00 | 01           | 00 | 10             | 00 | 11       | 01   | 00         | 01 | 01      | 01 | 10         | 01       | 11           | 10 | 00   | 10          | 01  | 10 | 10   | 10 | 11         | 11 | 00            | 11          | 01  | 11 | 10            | 11   | 11        |

|---------------|----------|--------------|----|--------------|----|----------------|----|----------|------|------------|----|---------|----|------------|----------|--------------|----|------|-------------|-----|----|------|----|------------|----|---------------|-------------|-----|----|---------------|------|-----------|

| Lower 4 bits  | (        | 0)           | (  | 1)           | (  | 2)             | (  | 3)       | (    | 4)         | (  | 5)      | (  | 6)         | (        | 7)           | (  | 8)   | (           | 9)  | (  | A)   | (  | B)         | (  | C)            | (           | D)  | (  | E)            | (1   | F)        |

| 0000          |          | ::::         |    |              |    |                |    | ···.     | _    |            | _  |         | _  | ٠.         |          |              |    |      | ,           |     |    |      |    |            | _  | j             |             |     |    | <u></u> ,     | 4    |           |

| (0)           | <u>a</u> | ****         | α  |              |    |                | W  |          | ſū   |            | Р  |         |    | _          | р        | <b></b>      | á  | •    | Ó           |     |    |      |    | ****       | タ  | ij            | 111         | ₩,  | A  |               | 0    | <b></b> ! |

| 0001          |          |              | _  |              |    | T              | _  | 1        |      |            |    |         |    |            |          |              |    | ٠.   | l ,         |     |    |      | _  |            | _  |               |             |     | λ  |               |      |           |

| (1)           |          | !!           | β  |              | L! | Ŀ              | 1  | .l.      | A    | -          | Q  |         | а  |            | q        |              | à  |      | ö           | (") | ٥  |      | ア  | <u>j'</u>  | 7  | <b></b>       | 4           |     | A  | -             | Ö    | <b></b> ! |

| 0010          | _        |              |    | •.•          | "  | H              |    | ,,       | _    |            | -  |         |    |            |          |              | _  |      | _           | ::: | _  | ľ    | ,  |            |    |               |             |     | Á  |               | _    | <u>.</u>  |

| (2)           | 1        |              | γ  | Ņ            |    |                | 2  |          | В    |            | R  | 13      | Ь  | Ľ          | r        | !·"·         | á  | -    | ō           |     | Γ  | •    | 1  | 1          | ツ  | ·             | Х           | ::  | Á  | -             | ō    | <b></b> ! |

| 0011          | -        | T            | -  | T.           | -  | . 1. 1.        |    | jr       |      |            | _  | ****    | -  |            |          |              |    |      |             |     |    |      |    |            | _  | ***           | _           |     | v  | <u>;::</u> ,  | ~    |           |

| (3)           | 1        | •            | δ  | -:           | #  |                | 3  |          | С    | <u></u> .  | S  |         | С  |            | s        | :::          | ä  | -::: | œ           |     | J  | !    | ゥ  | ·          | テ  | Ţ             | t           |     | Ä  | H             | Œ    | LL.       |

| 0100          |          |              |    |              |    |                |    |          |      | ···.       |    |         | _  |            |          | ı.           | _  |      |             |     |    |      |    |            |    |               |             | :   | _  | ,::: <u>,</u> |      |           |

| (4)           | ±        |              | ε  | :::          | \$ |                | 4  |          | D    | Ŀ          | Т  | L       | d  |            | t        | Ť.           | а  | -::: | æ           |     | `  | ٠.   | エ  | <b></b> .  | ト  | ŀ.            | ヤ           | Ti: | Ā  | M             | Æ    | HL.       |

| 0101          | _        | ,···         |    |              |    | П.             |    |          |      |            |    |         |    |            |          |              |    | •    |             | •   |    | _    |    |            |    |               |             |     |    | '.<br>        |      | •         |

| (5)           | £        | <u>.</u>     | θ  |              | %  | • "            | 5  |          | Ε    | Ľ.,        | U  |         | е  |            | u        | <b>.</b> !   | è  |      | ù           | !   | 0  | III  | オ  |            | ナ  | <b>;:!</b> '' | ユ           | İ.  | È  | <b>!</b>      | Ù    | <b>  </b> |

| 0110          |          |              |    |              |    |                |    |          |      |            |    |         |    |            |          | -            |    |      |             | •   |    |      |    | . <u>.</u> |    |               |             |     |    | :             |      | . :       |

| (6)           | `        | ••           | λ  | <u>, i.,</u> | &  |                | 6  |          | F    |            | ٧  | <u></u> | f  | Ŧ,         | ٧        |              | é  |      | ú           |     | ヲ  |      | カ  | ,I ,I      | =  |               | 3           |     | É  | <u></u>       | Ú    |           |

| 0111          |          | -            |    |              |    |                |    |          |      | , <u>.</u> |    |         |    |            |          |              |    |      |             |     |    |      |    |            |    |               |             |     |    |               |      | •         |

| (7)           |          |              | μ  | Ŀ            | _  | :              | 7  | ľ        | G    |            | W  | <u></u> | g  |            | ₩        | <u>.</u>     | ë  |      | ü           | II  | ア  |      | +  |            | ヌ  | ×             | ラ           | ٠   | Ë  | <b></b>       | Ü    |           |

| 1000          |          |              |    | ١.           |    | _              |    | .,,,,    |      |            |    |         |    |            |          |              | _  |      |             |     |    |      |    |            |    |               |             |     | _  |               | _    |           |

| (8)           | ~        | •            | ν  | . <u>.</u> ! | (  | ١.             | 8  |          | Н    |            | Х  |         | h  | Ľ          | Х        | $\mathbf{x}$ | е  |      | u           |     | 1  | ·1   | ク  |            | ネ  |               | リ           | Ņ   | Ē  | <u></u>       | Ū    |           |

| 1001          |          |              |    |              |    |                |    | ***      |      | ·i·        |    |         |    |            |          |              |    | ٠.   |             |     |    |      |    |            |    |               |             |     | ,  |               |      | • •       |

| (9)           | Φ        |              | π  | JII.         | )  |                | 9  |          | I    | ļ.         | Υ  | 'n      | i  | 1          | У        |              | ì  | 1.   | ς           | 3.  | ゥ  |      | ケ  | ľŢ.        | 1  | ,i            | ル           |     | ١  | I             | ÿ    |           |

| 1010          |          |              |    |              |    |                |    |          |      |            |    |         |    | -          |          |              |    |      |             |     |    |      |    |            |    |               |             |     |    |               |      |           |

| (A)           | Σ        |              | Р  | <b> </b>     | *  | : <b>-</b>  -: | :  | ##<br>## | J    | !          | Z  |         | j  | 1          | z        | .:           | ĺ  | 1.   | ≠           |     | I  |      |    |            | 71 |               | レ           |     | ĺ  | I             | √    | .,I'''    |

| 1011          |          |              |    |              |    |                |    |          |      |            |    | in      |    |            |          |              |    |      |             |     |    |      |    |            |    |               |             |     |    |               |      |           |

| (B)           | Fr       | ľ            | σ  |              | +  | ··             | ;  | ;        | K    | K          | (  | ľ.      | k  | K          | {        | 4            | ï  | 1.   | 千           | #   | オ  | ;;it | サ  | ļ!         | ۲  | ļ             |             |     | Ϊ  | I             | ~    | ,         |

| 1100          |          |              |    | gran         |    |                |    | _        |      |            |    |         |    |            |          |              |    |      |             |     |    |      |    |            |    |               |             |     |    |               |      |           |

| (C)           | ¢        | <b>:::</b> : | Σ  | :-<br>:      | ,  | ;              | <  | ٤,       | L    | Ĺ          | ¥  |         | ١  |            |          |              | Ī  | 1.   | 万           | F   | ヤ  | 1:   | シ  |            | フ  |               | ワ           |     | Ī  | I             | §    | Ü         |

| 1101          |          |              |    |              |    |                |    |          |      |            |    | ***     |    |            |          | 1_           |    |      |             |     |    |      |    |            |    |               |             |     |    |               |      |           |

| (D)           | !!       |              | ÷  | •••••        | _  |                | =  | •••••    | М    |            | )  |         | m  | ľľ         | }        | }            | i  | I    | 2           | 7   | 그  | .:.  | ス  |            | ^  | ٠.,           | ン           |     | ં  | ٠             | n    | rı        |

| 1110          |          |              |    |              |    |                |    | •        |      |            |    |         |    |            |          |              |    |      |             |     |    |      |    |            |    |               |             |     |    | .""           |      | _         |

| (E)           | ω        |              | Ψ  | ŀŀ           | -  |                | >  |          | N    | Ŀ          | ^  | .**.    | n  | <b>!</b> " | <b>-</b> |              | ñ  | F    | 1/2         |     | 3  |      | セ  |            | 朩  |               | "           | • • | Ñ  | M             | 1/4  | ı<br>i    |

| 1111          |          |              |    |              |    |                |    | ***      |      |            |    |         |    |            |          |              |    |      |             |     |    |      |    | Ħ          |    |               |             | ,   |    | <b></b>       |      |           |

| (F)           | Ω        |              | ∞  | :::          | /  | • •            | ?  |          | 0    |            | L  |         | 0  |            | _        | ·i           | ò  |      | 3/4         |     | ツ  |      | ソ  | <u> </u>   | マ  |               | ٥           | I.I | Ò  |               |      |           |

| Configuration |          |              |    |              | 1  |                |    | 5×7      | 'dot | s          |    |         | 1  |            |          |              |    |      | <del></del> |     | 5  | ×1   |    | ts         | L  | ±==           | <del></del> |     | 5  | ×12           | 2dot | s         |

## 9. Character Generator RAM (CG RAM)

The CG RAM is used to display user's original character pattern other than CG ROM. The CG RAM has capacity (32 bytes = 256 bits) to write 4 kinds of 5 x 8 dots and 2 kinds of 5 x 12 dots.

In displaying the character pattern stored in the CG RAM, CG RAM has to be enabled by an instruction. When CG RAM is enabled, CG ROM code for 16 characters cannot be read out since the CGROM code with all "L" on the upper 4 bits is used as CG RAM code.

The following describes how to write character patterns into the CG RAM and how to display them on the LCD.

- (1) When the character pattern is 5 x 8 dots (See Table 2-1)

- A method to write character pattern into the CG RAM by the CPU

The lower 3 bits (0 - 2) of the CG RAM address correspond to the line position of the character pattern. The upper 2 bits (3, 4) of the CG RAM address correspond to the lower 2 bits (0, 1) of the character code.

First, set increment of decrement by the CPU, and then input CG RAM address. After this, write character pattern data into CG RAM through DB0 to DB7 line by line.

DB0 - DB7 correspond to CG RAM data 0 - 7 in Table 2-1.

Display is turned on when "H" is set as input data and turned off when "L" is set as input data.

Since the ADC is automatically incremented or decremented by 1 after the writing of data to the CG RAM, it is not necessary to set the CG RAM address again.

To enable cursor display, set all input data on the line where the lower 3 bits of the CG RAM (0-2) are all "H" to "L".

0-4 bits of CG RAM data are output to the LCD as the display data; however, 5-7 bits of CG RAM data are not. But it can be used as the data RAM because the data can be written/read through DB0 to DB7.

A method to display the CG RAM character pattern to the LCD

First, an instruction to enable the CG RAM has to be input from the CPU. CG RAM is selected only when all of the upper 4 bits of the character code is "L". So, the character pattern of CG RAM is displayed on the LCD position that corresponds to the DD RAM address, when the character code shown in Table 2-1 is written into DD RAM. Since the bits 2 and 3 of the character code are regarded as invalid, "K" is displayed when the character codes "01", "05", "'09", and "0D" are selected.

- (2) When the character pattern is  $5 \times 12$  dots (See Table 2-2)

- A method to write character pattern into the CG RAM by the CPU

The lower 4 bits of CG RAM address (0-3) correspond to the line position of the character pattern.

The upper 1 bit of CG RAM address bit 4 corresponds to the bit 1 of the character code. First, set increment or decrement by the CPU, and then input CG RAM address.

After this, write the character pattern data into CG RAM through DB0 to DB7 line by line. DB0 - DB7 correspond to CG RAM data 0 - 7 in Table 2-2.

Display is turned on when "H" is set as the input data and turned off when "L" is set

as the input data.

Since the ADC is automatically incremented or decremented by 1 after the writing of data to the CG RAM, it is not necessary to set the CG RAM address again.

To enable cursor display, set all input data on the line where the CG RAM address is "0B" or "1B" (hex.) to "L".

The addresses "0" to "B" (hexadecimal) in the bits 0 to 4 of the CG RAM data are output on the LCD as the display data. However, the addresses "C" to "F" (hexadecimal) in the bits 0 to 4, and 5 to 7 of the CG RAM data are not output on the LCD. But these CG RAM data can be used as the data RAM so that they can be written into or read out through DB0 to DB7.

A method to display the CG RAM character pattern on the LCD

First, an instruction to enable the CG RAM has to be input from the CPU. CG RAM is selected only when all of the upper 4 bits of the character code is "L".

So, the character pattern of CG RAM is displayed on the LCD position corresponding to the DD RAM address, when the character code shown in Table 2-2 is written into the DD RAM

Since bits 0, 2 and 3 of the character code are regarded as invalid, the character of " $\mu$ " is displayed when the character codes "00", "01", "04", "05", "08", "09", "0C" and "0D" are selected.

#### (3) A method to read out the CG RAM data

First, set the CG RAM address by inputting a CG RAM address set instruction from the CPLL

Then, execute the CG RAM/DD RAM data read instruction. The set data of CG RAM address is output from the DB0 to DB7. The 8-bit data, read out from the MSM6262-xx, corresponds to the data which is written into the CG RAM. Since the CG RAM address is automatically incremented or decremented by 1, the CG RAM read out instruction can be successfully input. It is necessary, however, to set the DD RAM at data transferring condition by executing the DD RAM address set instruction after all of CG RAM data are read out.

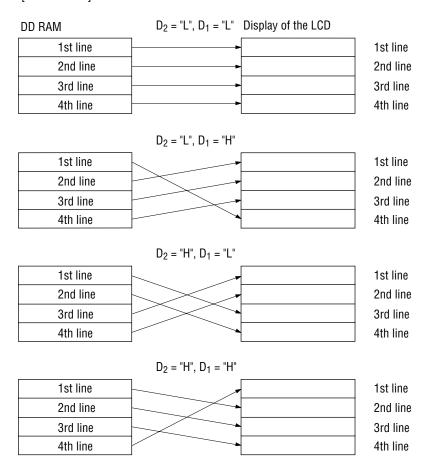

Table 2-1 Relation between CG RAM data (character pattern) vs. CGRAM address and DDRAM data vs. character pattern when the character pattern is  $5 \times 8$  dots.

| CG RAM<br>ADDRESS                                                                                       | CG RAM DATA<br>(Character Pattern)                                                                                              | DD RAM DATA<br>(Character Code ) |

|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 4 3 2 1 0<br>LSB                                                                                        | 7 6 5 4 3 2 1 0<br>MSB LSB                                                                                                      | 7 6 5 4 3 2 1 0<br>MSB LSB       |

| L L L L L L L L H L L H H L L H L H H L H H L H H H L H H H H L H H H H H H H H H H H H H H H H H H H H | X X X L H H H L H L L L H H L L L H H L L L H H L L L H H L L L H L H H L L L H                                                 | LLLLXXLL                         |

| L H L L L                                                                                               | X X X H L L H L H L L H L L H L L L H L L L H L L L H L L L H L L L H L L L H L L L L H L L L L L L L L L L L L L L L L L L L L | LLLLXXLH                         |

| H H L L L L H L L H L L H H H L L H L H H L H H H H H                                                   | X X X L H H H L L L L H L L L L H L L L L                                                                                       | LLLLXXHH                         |

X: Don't care

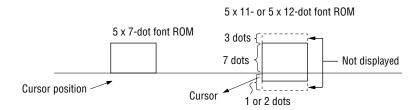

Table 2-2 Relation between CGRAM data (character pattern) vs. CGRAM address and DDRAM data vs. character pattern when the character pattern is  $5 \times 12$  dots.

| CG RAM<br>ADDRESS                       | CG RAM DATA (Character Pattern)           | DD RAM DATA<br>(Character Code) |               |

|-----------------------------------------|-------------------------------------------|---------------------------------|---------------|

| 4 3 2 1 0                               | 7 6 5 4 3 2 1 0                           | 7 6 5 4 3 2 1 0                 |               |

| LSB                                     | MSB LSB                                   | MSB LSB                         |               |

|                                         | X X X L L L L L L L L L L L L L L L L L   | LLLLXXLX                        | <b>◄</b> ── B |

| H L L L L L L L L L L L L L L L L L L L | X X X L L L L L L L L L L L L L L L L L L | LLLLXXHX                        | <b></b> B     |

X: Don't care

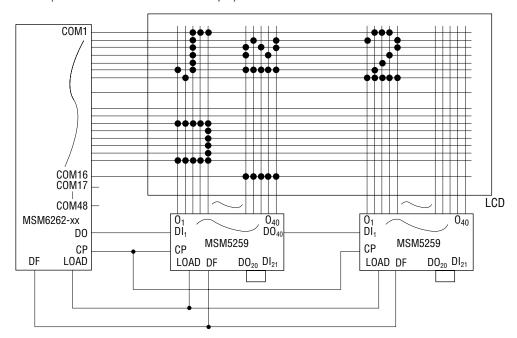

## 9. LCD Display Circuit (COM1 to COM48, DO, CP, LOAD, DF)

The MSM6262-xx is provided with COMMON signal output. So, maximum 160 characters can be displayed when it is used together with SEGMENT drivers (MSM5259 or MSM5839C). Interface between MSM6262-xx and SEGMENT drivers can be done by using DO, CP, LOAD and DF.

The SEGMENT data is serially output from DO pin, synchronized with the pulse which is output from the CP pin.

This data, input to the SEGMENT driver, is converted from serial data to parallel data by the latch pulse which is output from the LOAD pin of MSM6262-xx and this converted data is used as the display data. This parallel/serial conversion is performed synchronized with the COMMON signal of MSM6262-xx and LCD display AC signal which is output from DF pin. So, this signal can drive dot matrix LCD panel.

#### 10. Reset Circuit

Power-on-reset is required for MSM6262-xx when it is powered-on. So, a capacitor has to be connected between  $\overline{RESET}$  pin and  $V_{SS}$  pin.

It is also advisable to connect a diode between  $\overline{RESET}$  pin and  $V_{DD}$  pin when it is required to connect a capacitor of more than 3.3  $\mu F$  to  $\overline{RESET}$  pin.

When the power-on reset circuit normally operates, the busy flags 1 and 2 become at "H" level for about 10 ms after the power-on. During this period, a initialization of MSM6262-xx is performed by following procedures.

- 1 Display is cleared

- 2 CG ROM becomes enabled

- 3 No display shift

- 4 ADC is incremented

- 5 2-line display mode

- 6 5 x 8 dots font configuration

- 7 No display shift for "g", "j", "p", "q" and "y"

- 8 Display off

- 9 No display of cursor, blinking and underline

## 11. Data Bus with CPU

MSM6262-xx can be interfaced with 8-bit CPU, such as 6809, Z80, 80C49 and 80C51. When MSM6262-xx is connected with 6809, the 68 series/80 series pin has to be connected to  $V_{DD}$ . When MSM6262-xx is connected with Z80, 80C49 or 80C51, the 68 series/80 series pin has to be connected to  $V_{SS}$ . The level at 68 series/80 series cannot be switched during MSM6262-xx's operation. It must be connected with either  $V_{DD}$  or  $V_{SS}$  before MSM6262-xx is turned on.

Note: It is possible, indeed, to change the 68 series / 80 series pin's level when a reset signal is being input to RESET pin. However, the 68 series / 80 series pin does not have characteristics to have an interface with MCU, nor does it have an antichattering circuit.

Further, if a reset signal is input, the MSM6262-xx is initialized as described above. So, in this case, changing the 68 series /80 series pin level is not recommended.

## 80 series CPU data transfer

## 68 series CPU data transfer

# **Instruction Table**

| * | DON'T CAR | Е |

|---|-----------|---|

|   | DUN I GAN | _ |

| 80series Cou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Note<br>1                                                                                               | A <sub>1</sub>                                                      | A <sub>0</sub> | DB <sub>7</sub> | DB <sub>6</sub>                                                                           | DB <sub>5</sub>                                                                    | $DB_4$                                                                                    | DB <sub>3</sub>                                                                              | DB <sub>2</sub>            | DB₁                     | DB <sub>0</sub>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | * : DON'T CARE  Execution Time (MAX),                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------|-----------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------|-------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 80series CPU<br>68series CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1<br>R/W                                                                                                | A <sub>1</sub>                                                      | A <sub>0</sub> | DB <sub>7</sub> | DB <sub>6</sub>                                                                           | DB <sub>5</sub>                                                                    | DB <sub>4</sub>                                                                           | DB <sub>3</sub>                                                                              | DB <sub>2</sub>            | DB <sub>1</sub>         | DB <sub>0</sub>    | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | When fosc = 500kHz                                               |

| Display Clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | L                                                                                                       | L                                                                   | L              | L               | L                                                                                         | L                                                                                  | L                                                                                         | L                                                                                            | L                          | L                       | Н                  | Clears all of the display, and sets<br>address 0 of DD RAM in the address<br>counter.                                                                                                                                                                                                                                                                                                                                                                                                    | 3.22 ms                                                          |

| Return                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | L                                                                                                       | L                                                                   | L              | L               | L                                                                                         | L                                                                                  | L                                                                                         | L                                                                                            | L                          | Н                       | CR/C               | CR/C = L: Cursor home<br>CR/C = H: Carriage Return                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.62 ms                                                          |