## **OKI** Semiconductor

# MSM60808

### PCI to PCMCIA R2.1/CardBus Controller (PPCC)

### **FEATURES**

- PCI Local Bus Specification Rev. 2.1 Compliant

- PC Card Standard 95 Compliant

- PC Card auto-detect configuration

- 2-socket multifunction PCI device

- Intel 82365 register-compatible

- Power supply voltage +3.0~+3.6 V (core)

- +3.0~+3.6 V, +4.5~+5.5 V (I/O)

- Maximum operating frequency: 33 MHz

- Serial interface with power control IC TI TPS2202AI

- ZV port mode supported

- Clock control (CLKRUN#) supported

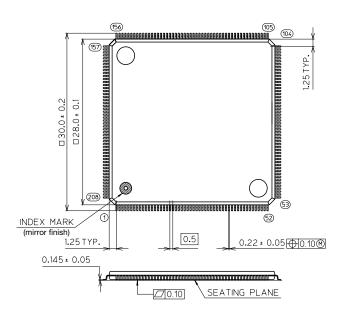

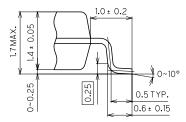

- Package: 208-pin plastic LQFP (LQFP208-P-2828-0.50-K) (Product name: MSM60808GS-K)

### **Table of Contents**

### 1. General Description

- 1.1 PCI Interface

- 1.2 CardBus Card Interface

- 1.3 16-Bit Card Interface

- 1.4 Configuration

- 1.5 PC Card Registers

- 1.6 Determining Card Types

- 1.7 Address Decoding

- 1.8 Interrupts

- 1.9 Socket Power Control

- 1.10 Clock Control

- 1.11 Reset

- 1.12 ZV Port

- 1.13 Restrictions

- 2. Block Diagram

- 3. System Configuration Example

- 4. Pin Descriptions

- 4.1 Signal Types

- 4.2 PCI Bus Interface Signals

- 4.3 CardBus Interface Signals

- 4.4 16-Bit Card Interface Signals

- 4.5 Interrupt Signals

- 4.6 Audio Signals

- 4.7 PC Card Power Switch Signals

- 4.8 Voltage Supply Signals

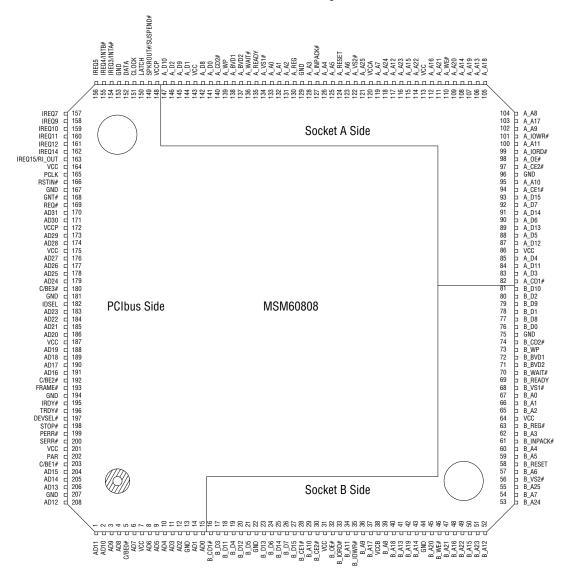

- 4.9 Pinout

- 4.9.1 PCI Bus CardBus Pinout

- 4.9.2 PCI Bus 16-Bit Pinout

### 5. Registers

- 5.1 Configuration Registers

- 5.2 16-Bit Card Registers

- 5.3 CardBus Registers

- 6. Electrical Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 Recommended Operating Conditions

- 6.3 DC Characteristics

- 6.4 AC Characteristics

- 7. Package Dimentions

MSM60808

### 1. General Description

The MSM60808 is a bridge chip to interface a PCI bus and a two-socket PC Card bus. The PCI bus interface is based on the PCI 2.1 standard. The PC Card interface works with 16-bit cards and 32-bit CardBus cards based on the PCMCIA 2.1/JEIDA 4.2 standard. This new PC Card standard enables high-speed data transfer at a maximum clock frequency of 33 MHz, with a data width of 8 bits or 16 bits for 16-bit PC Cards and a data width of 32 bits for CardBus PC Cards.

When a PC Card is inserted in a socket, the MSM60808 automatically detects the card type and the power supply voltage requested by the card. After it detects card type and power supply voltage, the MSM60808 automatically switches to 16-bit PC Card mode or CardBus PC Card mode depending on the type of card inserted. In 16-bit PC Card mode, the MSM60808 operates as a target device on the PCI bus, and in CardBus PC Card mode, the MSM60808 operates as a PCI-to-PCI bridge. After this, software will configure the MSM60808's internal control registers, and data transfer from the PCI bus to the card can begin.

After the card's power supply voltage has been confirmed, the MSM60808 performs serial data access to the TPS2202AI voltage control chip and applies voltage to the card using the TPS2202AI. When the card is removed, the MSM60808 automatically stops applying voltage to the socket.

After a card is inserted, it will have numerous status changes and request service routines, which will generate various interrupts. These interrupts can be made on the ISA bus IREQ signal or the PCI bus INT# signal.

### 1.1 PCI Interface

The MSM60808 is a multifunction PCI device that supports PC Cards in two sockets.

When a CardBus card is inserted in a socket, the MSM60808 will operate as a PCI-to-PCI bridge. When a 16-bit card is inserted, the MSM60808 will operate as a PCI target device. Table 1.1 shows each of the bus commands supported by the MSM60808 for different cards. When MSM60808 is a target, the response speed of DEVSEL# is medium speed.

**Table 1.1 PCI Bus Commands For Different Cards**

| C/BE[3:0]# | Command Type            | 16-Bit Cards  | Target CardBus<br>Cards | Master CardBus<br>Cards | Buffer Control |

|------------|-------------------------|---------------|-------------------------|-------------------------|----------------|

| 0000       | Interrupt Acknowledge   | Not Supported | Not Supported           | Not Supported           | _              |

| 0001       | Special Cycle           | Not Supported | Not Supported           | Not Supported           | _              |

| 0010       | IO Read                 | Supported     | Supported               | Supported               | No             |

| 0011       | IO Write                | Supported     | Supported               | Supported               | No             |

| 0100       | Reserved                | _             | _                       | _                       | _              |

| 0101       | Reserved                | _             | _                       | _                       | _              |

| 0110       | Memory Read             | Supported     | Supported               | Supported               | Yes            |

| 0111       | Memory Write            | Supported     | Supported               | Supported               | Yes            |

| 1000       | Reserved                | _             | _                       | _                       | _              |

| 1001       | Reserved                | _             | _                       | _                       | _              |

| 1010       | Configuration Read      | Supported     | Supported               | Not Supported           | No             |

| 1011       | Configuration Write     | Supported     | Supported               | Not Supported           | No             |

| 1100       | Memory Read Multiple    | Supported     | Supported               | Supported               | No             |

| 1101       | Dual Address Cycle      | Not Supported | Not Supported           | Not Supported           | _              |

| 1110       | Memory Read Line        | Supported     | Supported               | Supported               | No             |

| 1111       | Memory Write Invalidate | Supported     | Supported               | Supported               | No             |

**OKI** Semiconductor

MSM60808

Data transfers from PCI to CardBus and from CardBus to PCI are performed as delayed transactions for configuration read/write cycles, IO read/write cycles, and memory read cycles, and are performed as posted writes for memory write cycles. For 16-bit cards, this applies to transfers from PCI to the card.

The MSM60808 can also control the depth of the internal FIFO used for data transfers (memory read/write cycles). This control enables switching between single transfers and burst transfers.

The PCI lock function and bus parking function are not supported.

### 1.2 CardBus Card Interface

The maximum operating frequency between the PCI bus and the MSM60808 is 33 MHz. The CardBus clock outputs the PCI system clock as is, so the CardBus maximum operating frequency is also 33 MHz. When a CardBus card is inserted, the MSM60808 operates as a PCI-to-PCI bridge. Applicable bus commands are shown in Table 1.1.

Configuration write cycles also issue special cycles.

The MSM60808 has an internal counter to measure the number of retries received, so when a target card returns a retry the MSM60808 will issue commands to the card until the counter finishes. It transfers target aborts and master aborts generated by the CardBus to the PCI bus in accordance with the bridge control register settings.

For master cards, data transfers are processed as delayed transactions and posted writes, identical to the PCI interface. The response speed of CDEVSEL# is also medium speed.

### 1.3 16-Bit Card Interface

The MSM60808 uses a data width of 32 bits to transfer data between itself and the PCI bus, and a data width of either 8 bits or 16 bits to transfer data between itself and a 16-bit PC Card. Applicable bus commands are shown in Table 1.1.

When a 16-bit card is inserted, the MSM60808's 16-bit card control logic will be selected. The card interface will be Intel 82365 compatible. The 16-bit card control logic transfers data by converting the 32-bit data of the PCI bus to the 8-bit or 16-bit data requested by the PC Card. Memory write commands are performed as posted writes and all other commands use delayed transactions, so this conversion does not have a large effect on the transfer efficiency of the PCI bus. As a result data can be transferred without degrading system transfer speed.

The MSM60808 supports the READY/BUSY# signal of memory cards and INPACK# signal of I/O cards.

### 1.4 Configuration

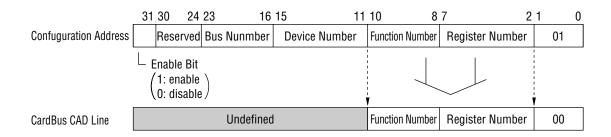

The MSM60808 is a CardBus controller for two sockets, so it has two independent configuration spaces. As shown in Table 1.2, Function 0 is used for Socket A and Function 1 is used for Socket B. In order to access the configuration of a CardBus card, MSM60808 decodes the Function Number Field, sets CAD[1:0] to 00b, and issues a configuration on the CardBus.

When the bus number of a Type 1 configuration command matches MSM60808's CardBus number (CBBUSN), MSM60808 responds to the configuration cycle and generates a Type 0 configuration cycle on the CardBus. If the bus number is greater than the CardBus number (CBBUSN), and if it is less than or equal to the subordinate bus number (SUBBUSN), then MSM60808 will forward the Type 1 configuration cycle.

Figure 1.1 Configuration Type 1 → Type 0 Conversion

Table 1.2 Slot Selected by Function Number

| <b>Function Number</b> | Selected socket |

|------------------------|-----------------|

| 0h                     | Socket A        |

| 1h                     | Socket B        |

| 2h~3h                  | Reserved        |

OKI Semiconductor MSM60808

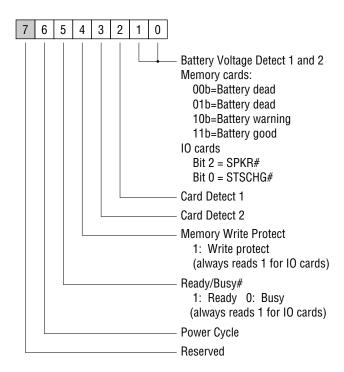

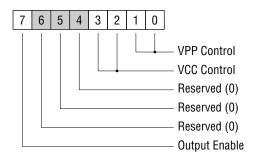

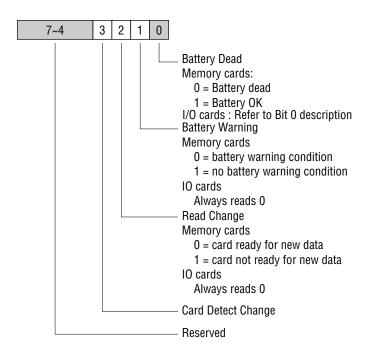

### 1.5 PC Card Registers

In order to control PC Cards in two sockets, MSM60808 has CardBus card registers and 16-bit card registers for each socket.

The CardBus registers are configured from two types of registers (CardBus Socket Status Register and Clock Control Register). These registers are mapped to memory space by the PC Card Socket Status Address Register (PCCBADR) and can be directly accessed.

The 16-bit card registers are configured from four types of registers (Setup Register, Interrupt Control Register, IO Mapping Control Register, and Memory Mapping Control Register). These registers can be mapped to both memory space and IO space. When mapped to memory space, they can be directly accessed using the PC Card Socket Status Address Register (PCCBADR), similarly to the CardBus registers. In this case the 16-bit card registers are located in the upper 2 Kbytes of the 4 Kbytes saved by the PC Card Socket Status Address Register (PCCBADR). When mapped to IO space, they can be indirectly accessed using the Index/Data Register at the address pointed to by the R21 Register Base Address (R21BADR).

### 1.6 Determining Card Types

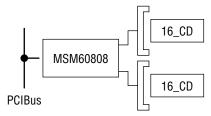

MSM60808 decodes the CVS[2:1] and CCD[2:1] pins as shown in Table 1.3, determines the card type and voltage to apply, and then reflects the result in MSM60808's internal Socket Present Register. After MSM60808 has checked the card, it switches its internal control logic to conform to the type of card inserted. The types of cards that may be inserted into the sockets correspond to the cases shown in Figure 1.2.

Table 1.3 CCD#[2:1]/CVS[2:1] and PC Card Interface

| CCD2#              | CCD1#              | CVS2                | CVS1                | Key              | InterFace          | Voltage                |  |

|--------------------|--------------------|---------------------|---------------------|------------------|--------------------|------------------------|--|

| Ground             | Ground             | Open                | Open                | 5V 16bit PC Card |                    | 5V                     |  |

| Ground             | Ground             | Open                | PD                  | 5V 16bit PC Card |                    | 5V and 3.3V            |  |

| Ground             | Ground             | Ground              | PD                  | 5V               | 16bit PC Card      | 5V and 3.3V            |  |

| Ground             | Ground             | Open                | Ground              | LV               | 16bit PC Card      | 3.3V                   |  |

| Ground             | Connect to<br>CVS1 | Open                | Connect to<br>CCD1# | LV               | CardBus PC Card    | 3.3V                   |  |

| Ground             | Ground             | Ground              | Ground              | LV               | 16bit PC Card      | 3.3V and X.XV          |  |

| Connect to CVS2    | Ground             | Connect to CCD2#    | Ground              | LV               | CardBus PC Card    | 3.3V and X.XV          |  |

| Connect to<br>CVS1 | Ground             | Ground              | Connect to CCD2#    | LV               | CardBus PC Card    | 3.3V, X.XV and<br>Y.YV |  |

| Ground             | Ground             | Ground              | Open                | LV               | 16bit PC Card      | X.XV                   |  |

| Connect to CVS2    | Ground             | Connect to CCD2#    | Open                | LV               | CardBus PC Card    | X.XV                   |  |

| Ground             | Connect to CVS2    | Connect to CCD1#    | Open                | LV               | CardBus PC Card    | X.XV and Y.YV          |  |

| Connect to<br>CVS1 | Ground             | Open                | Connect to CCD2#    | LV               | LV CardBus PC Card |                        |  |

| Ground             | Connect to CVS1    | Ground              | Connect to CCD1#    | Reserved         |                    |                        |  |

| Ground             | Connect to CVS2    | Connect to<br>CCD1# | Ground              | Reserved         |                    |                        |  |

Note: X.XV and Y.YV have not been standardized and are not supported.

# 1) CardBus PC Card CB\_CD CB\_CD CB\_CD

# MSM60808 CB\_CD PCIBus

3) CardBus card/16-bit PC Card

2) 16-bit PC Card

CB\_CD: CardBus PC Card 16\_CD: 16-bit PC Card

Figure 1.2 Card Combinations

### 1.7 Address Decoding

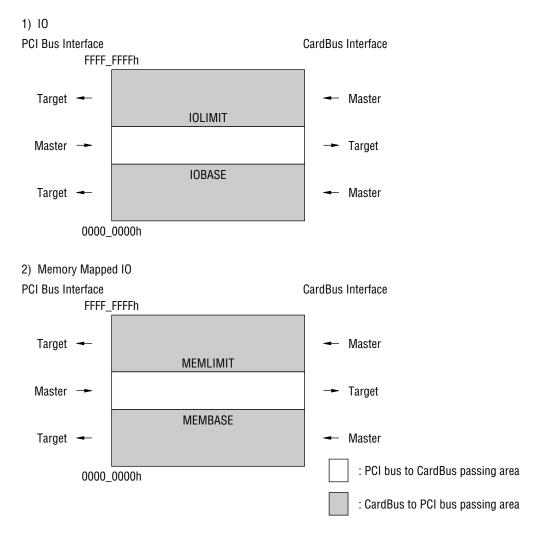

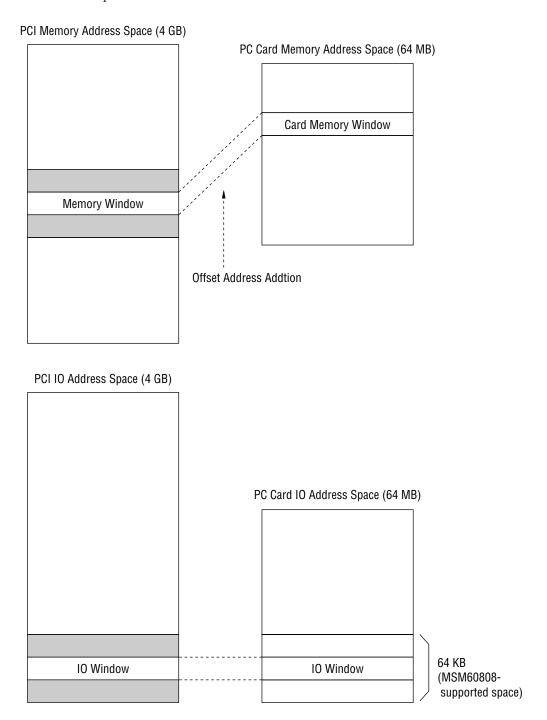

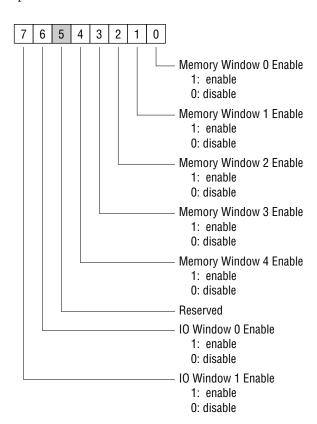

The MSM60808's Base Registers and Limit Registers (MEMBASE0/1, MEMLIMIT0/1, IOBASE0/1L, IOBASE0/1H, IOLIMIT0/1L) define the address window for forwarding transactions from the PCI bus to the CardBus.

Two address windows, a memory window and IO window, can be opened. The range of these windows can be set up to 4 GB for memory and 64 KB for IO in 4 KB units. The windows can be placed at any position in the 4 GB space with these registers.

These registers are used and decoded when transactions are data transfers forwarded from the CardBus to the PCI bus to determine MSM60808's CardBus address range. Figure 1.3 shows MSM60808's address decode method when a CardBus card is inserted.

Figure 1.3 Address Decoding Method (CardBus PC Card)

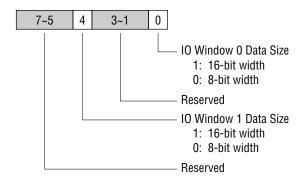

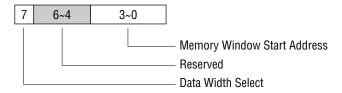

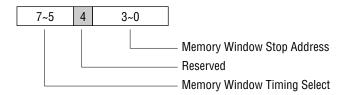

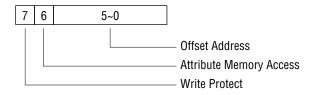

When a 16-bit card is inserted, the IO mapping control registers (IOCREG, IOSL[1:0], IOSH[1:0], IOSTL[1:0], IOSTL[

Figure 1.4 Address Decoding Method (16-bit PC Card)

SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83778810 FAX:0755-83376182 E-MAIL:szss20@163.com

### 1.8 Interrupts

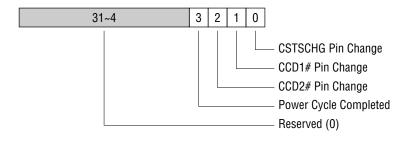

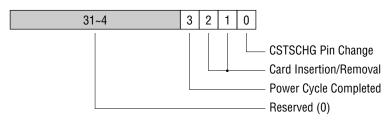

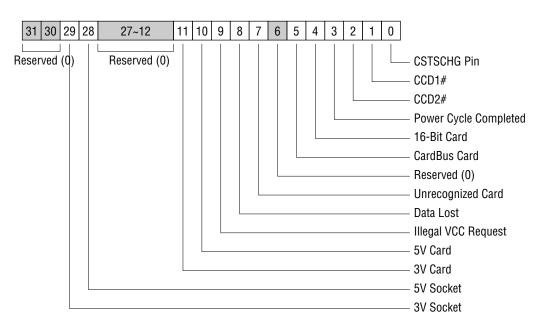

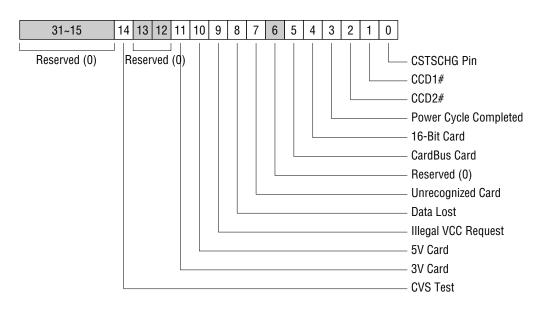

Interrupts are used to inform the system of card status changes like card detect pin transitions, battery discharge, and ready transitions, and of interrupt service requests from the PC Card to the system. For card status changes, 16-bit memory cards will generate interrupts when a bit in the Card Status Change Register (CSTCH) changes, and CardBus cards will generate interrupts when a bit in the Event Register (EVENT) changes. Generation of these card status change interrupts can be controlled by setting bits in the Card Status Change Interrupt Configuration Register (CSCICR) for 16-bit cards or the Interrupt Mask Register (MASK) for CardBus cards. For service requests, cards will generate interrupts to the system when card pin signal transitions are received (IREQ for 16-bit IO cards or CINT for CardBus cards). Table 1.4 lists the PC Card interrupt types and descriptions.

The MSM60808 supports ten ISA-compatible direct system interrupts (IREQ) and PCI interrupts (INTA/B#).

For PCI interrupts INTA# is assigned to Socket A and INTB# is assigned to Socket B. The ISA and PCI lines are multiplexed on the same pins, with the signals switched by setting bits in the Bridge Control Register (BRGCTL) and Card Control Register (CDCTL).

System interrupts can be executed without modification on ISA-compatible platforms. PC Card interrupts can be directly connected to the IREQ line. Edge-triggered system interrupt signals are supported with 16-bit cards.

Table 1.4 PC Card Interrupts

| Card Type     | Event                  | Interrupt Type         | Signal Line              | Description                                                 |

|---------------|------------------------|------------------------|--------------------------|-------------------------------------------------------------|

|               | Dottory status shangs  | CSC                    | BVD1                     | Notification of battery status chante by BVD1 signal        |

| 16-bit memory | Battery status change  | CSC                    | BVD2                     | Notification of battery status chante by BVD2 signal        |

|               | Card ready             | CSC                    | READY                    | Notification PC Card can accept data transfers              |

| 16-bit IO     | Card status change     | Card status change CSC |                          | Notification of card status change from PC Card             |

|               | Interrupt request      | FUNC                   | IREQ#                    | Interrupt service request from PC Card                      |

|               | Card status change     | CSC                    | CSTSCHG                  | Notification of card status change from PC Card             |

| CardBus       | Interrupt request      | FUNC                   | CINT#                    | Interrupt service request from PC Card                      |

|               | Power cycle done       | CSC                    | _                        | Notification to system of power cycle completion            |

| All cards     | Card insertion/removal | CSC                    | CD1#/CCD1#<br>CD2#/CCD2# | Notification of card insertion/<br>removal by CD pin change |

### 1.9 Socket Power Control

The MSM60808 has functions to control power. It performs socket power control through its internal Socket Present Register (PRESENT), Socket Control Register (CONTROL), CCD#[2:1], and CVS[2:1].

Power-up of both 16-bit cards and CardBus cards is done after card detection by software reading the PRESENT register and writing the contents to the CONTROL register. The MSM60808 uses the contents to output signals directly to the TI TPS2202AI, a socket power control IC.

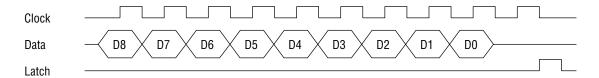

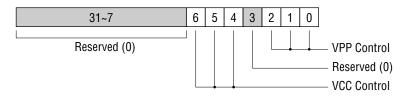

The TI TPS2202AI has three control lines (clock, data, latch) with which MSM60808 performs serial data transfers. Transfer speed is the clock from dividing the PCI bus clock by 16. Figure 1.5 and Table 1.5 show the serial data transfer protocol and contents. For details on the TI TPS2202AI, please refer to the TI TPS2202AI data sheet.

When PCIRST# is generated, register power is reset, prompting power-down. Power-down is performed automatically, without software writes to registers. For card removal power-down, data will be transferred only to the socket from which the card was removed. However, when reset by PCIRST#, the D8 bit (shutdown bit) will output low and both sockets will power down (at other times the D8 bit will always output high).

Figure 1.5 Control Output Signals For Power Control IC

| Table 1.5 Control Output Signals For Power Control IC | Table 1.5 ( | Control ( | Dutput Si | anals For | Power ( | Control IC |

|-------------------------------------------------------|-------------|-----------|-----------|-----------|---------|------------|

|-------------------------------------------------------|-------------|-----------|-----------|-----------|---------|------------|

|      | Socket B |    |    |      |    |    |      |    | Soci | cet A |    |    |

|------|----------|----|----|------|----|----|------|----|------|-------|----|----|

| SHDN | VCC      | D7 | D6 | VPP  | D5 | D4 | VPP  | D3 | D2   | VCC   | D1 | D0 |

| 1    | 0V       | 1  | 1  | Hi-Z | 1  | 1  | 0V   | 1  | 1    | Hi-Z  | 1  | 1  |

| 1    | 5V       | 1  | 0  | 12V  | 1  | 0  | 5V   | 1  | 0    | 12V   | 1  | 0  |

| 1    | 3.3V     | 0  | 1  | VCC  | 0  | 1  | 3.3V | 0  | 1    | VCC   | 0  | 1  |

| 1    | 0V       | 0  | 0  | 0V   | 0  | 0  | 0V   | 0  | 0    | 0V    | 0  | 0  |

| 0    | Χ        | Χ  | Χ  | Χ    | Χ  | Χ  | Χ    | Χ  | Χ    | Χ     | Χ  | Х  |

### 1.10 Clock Control

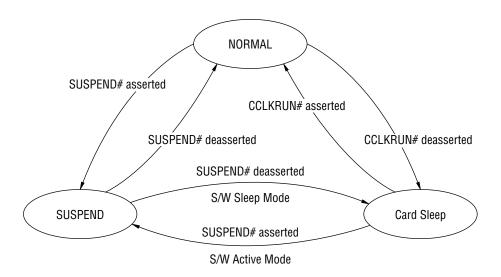

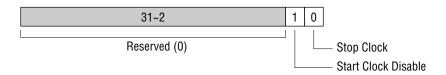

The MSM60808 has two clock control methods for reducing power to PC Cards as well as the MSM60808 itself.

The MSM60808's own clock will stop supplying MSM60808 internally when the SUSPEND# pin of the Card Control Register (CDCTL) is asserted low.

The clock to the card can be controlled by setting the Clock Control Register. However, just setting these bits will not stop the clock supply to the card. The MSM60808 communicates with the card using the CCLKRUN# pin, and it will stop the clock if that pin's state allows it.

In clock control the suspend mode has higher precedence than clock run mode. Therefore, care is needed in the sequence of events when stopping the clock supply. Figure 1.6 shows the transitions between each mode.

Figure 1.6 MSM60808 Power Management Transition Diagram

### 1.11 Reset

The MSM60808 will generate a reset signal to a card during the following states.

- 1) During a power cycle generated when the card is inserted or removed.

- 2) When the CRST# bit of the Bridge Control Register is set. (Note: Software reset is not supported for 16-bit cards.)

### 1.12 **ZV** Port

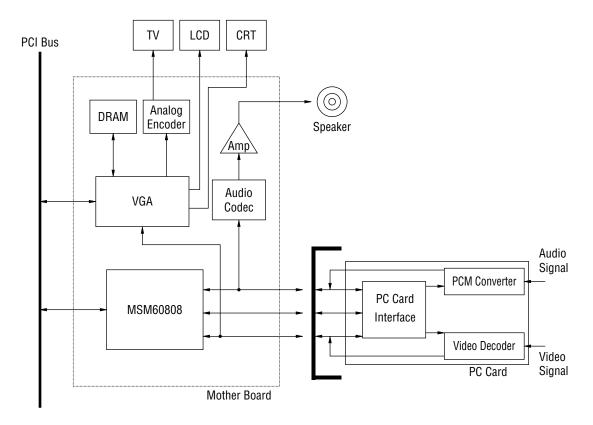

The MSM60808 can also be used for a ZV port. When a ZV card is inserted, the ZV Mode Enable Bit of the Card Control Register (CDCTL) will be set. In ZV port mode the address lines A[25:4] are used by the card, so MSM60808 will put these pins in a Hi-Z state. Figure 1.7 shows a system configuration example of a ZV port using the MSM60808.

Figure 1.7 ZV Port System Example

### 1.13 Restrictions

The MSM60808 does not support the following functions.

- 68-pin IDE interface mode

- DMA transfers

- PCI LOCK#

- Multifunction cards

- Serial IREQ

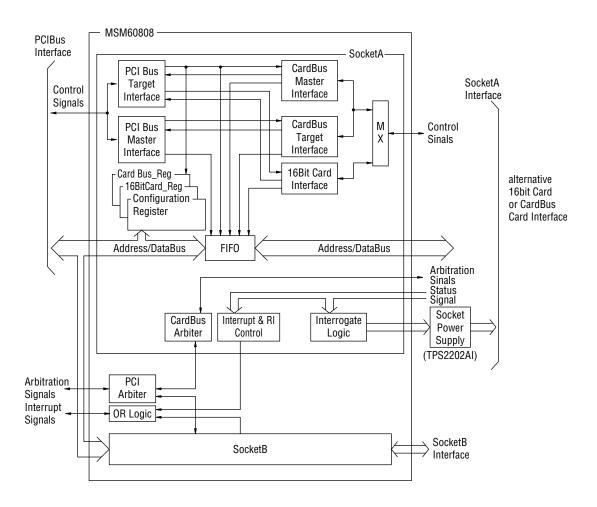

### 2. Block Diagram

Figure 2. Block Diagram

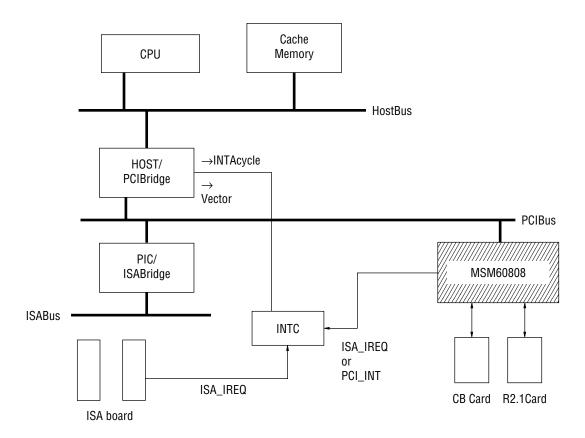

### 3. System Configuration Example

Figure 3.1 shows a configuration example of a system using the MSM60808.

Figure 3.1 System Configuration Example

### 4. Pin Descriptions

### 4.1 Signal Types

| IN    | Standard input signal.           |

|-------|----------------------------------|

| OUT   | Totem pole output signal.        |

| O/D   | Open drain output signal.        |

| T/S   | Bi-directional tri-state signal. |

| T/S/O | Tri-state output signal.         |

S/T/S Active-low sustained tri-state signal driven by only one agent at a time. The agent that drives an S/T/S signal low must drive it high for at least one clock before letting it float. A new agent cannot start driving the S/T/S signal any sooner than one clock after the previous owner tri-states it. When no agent is driving the S/T/S signal, an external pullup must be supplied by the central resource to sustain the inactive state.

### 4.2 PCI Bus Interface Signals

If a 16-bit card is inserted, then the MSM60808 converts the PCI interface to a PCMCIA interface. If a CardBus card is inserted, then the MSM60808 interfaces between the PCI local bus and the CardBus.

Table 4.1 PCI Bus Interface Signals

| Signal Name | I/O    | Description                                                                                                                                                               |

|-------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |        | PCI system clock signal. All PCI signals except RSTIN#, INTA#, and INTB# are                                                                                              |

| PCLK        | IN     | synchronized to the rising edge of PCLK. The MSM60808 is designed to operate up to 33 MHz.                                                                                |

|             |        | PCI system reset signal. When RSTIN# goes active, all MSM60808 internal functions                                                                                         |

| RSTIN#      | IN     | are reset and all MSM60808 internal registers are set to their default values.  RSTIN# operates asynchronously with PCLK. Also, the socket will enter a                   |

|             |        | power-down state when RSTIN# is active.                                                                                                                                   |

|             |        | Address/data bus signals. Addresses and data are multiplexed on the same PCI pins.                                                                                        |

| AD[31:0]    | T/S    | During the first clock of a transaction AD[31:0] carry a physical address (32 bits).                                                                                      |

|             |        | During the following clocks AD[31:0] carry data.                                                                                                                          |

|             |        | Command and byte enable signals. During the address phase of a transaction                                                                                                |

| C/BE#[3:0]  | T/S    | C/BE#[3:0] define the bus command. During the data phase C/BE#[3:0] are used as                                                                                           |

|             |        | byte enables.  Parity signal. PAR provides even parity across AD[31:0] and C/BE#[3:0]. Address                                                                            |

|             |        | parity is driven by the master that started the bus cycle one clock after the address                                                                                     |

| PAR         | T/S    | phase. In the data phase, the master calculates parity and drives PAR for write cycles,                                                                                   |

| 1741        | 1,0    | and the target does so for read cycles. Just like the address phase, in the data phase                                                                                    |

|             |        | parity for data is output delayed by one clock.                                                                                                                           |

|             | S/T/S  | Cycle frame signal. FRAME# is driven by the master to indicate the start and duration                                                                                     |

| FRAME#      |        | of a bus cycle. FRAME# is asserted to indicate the start of a bus cycle. Bus cycles                                                                                       |

| I I (AIVIL# | 0/1/0  | continue while FRAME# stays asserted. FRAME# is deasserted to indicate that the                                                                                           |

|             |        | next data phase is the final data phase.                                                                                                                                  |

| DEVOEL #    | 0.77.0 | Device select signal. When the MSM60808 is the target, it will respond to bus cycles                                                                                      |

| DEVSEL#     | S/T/S  | where DEVSEL# is asserted. When the MSM60808 is the master, it monitors                                                                                                   |

|             |        | DEVSEL# to determine whether or not the target has responded.                                                                                                             |

|             |        | Initiator ready signal. IRDY# indicates that the master is ready to perform a transfer. IRDY# is used in conjunction with TRDY#. Data transfers are timed to execute when |

|             |        | both IRDY# and TRDY# are asserted. During write cycles IRDY# indicates that valid                                                                                         |

| IRDY#       | S/T/S  | data is on AD[31:0]. During read cycles IRDY# indicates that the device is ready to                                                                                       |

|             |        | accept read data. Wait cycles are inserted until both IRDY# and TRDY# are asserted                                                                                        |

|             |        | together.                                                                                                                                                                 |

|             |        | 1 9                                                                                                                                                                       |

Table 4.1 PCI Bus Interface Signals (continued)

| Signal Name | I/O   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRDY#       | S/T/S | Target ready signal. TRDY# indicates that the target is ready to perform a transfer. TRDY# is used in conjunction with IRDY#. Data transfers are timed to execute when both IRDY# and TRDY# are asserted. During read cycles TRDY# indicates that valid data is on AD[31:0]. During write cycles TRDY# indicates that the device is ready to accept write data. Wait cycles are inserted until both IRDY# and TRDY# are asserted together. |

| STOP#       | S/T/S | Stop signal. STOP# is used by the target to request that the master stop the current transaction.                                                                                                                                                                                                                                                                                                                                          |

| IDSEL       | IN    | Initialization device select signal. IDSEL is used as a chip select signal during configuration cycles.                                                                                                                                                                                                                                                                                                                                    |

| PERR#       | S/T/S | Parity error signal. PERR# reports only data parity errors during all transactions except special cycles.                                                                                                                                                                                                                                                                                                                                  |

| SERR#       | O/D   | System error signal. SERR# reports address parity errors and other fatal system errors.                                                                                                                                                                                                                                                                                                                                                    |

| REQ#        | T/S/0 | Request signal. The MSM60808 asserts REQ# when the CardBus master requests use of the PCI bus.                                                                                                                                                                                                                                                                                                                                             |

| GNT#        | IN    | Grant signal. The PCI arbiter asserts GNT# to indicate the arbiter the MSM60808 bus usage rights.                                                                                                                                                                                                                                                                                                                                          |

### 4.3 CardBus Interface Signals

**Table 4.2 CardBus Interface Signals**

| Signal Name | I/O   | Description                                                                               |

|-------------|-------|-------------------------------------------------------------------------------------------|

|             |       | CardBus clock signal. All CardBus signals except CRST#, CCLKRUN#, CINT#,                  |

| CCLK        | OUT   | CSTSCHG, CAUDIO, CCD1#, CCD2#, CVS1#, and CVS2# are synchronized to the                   |

| COLK        | 001   | rising edge of CCLK. The CardBus clock is 33 MHz, but the clock can also be stopped       |

|             |       | by driving it low.                                                                        |

|             |       | CardBus clock run signal. A CardBus card asserts CCLKRUN# to request the                  |

| CCLKRUN#    | T/S   | MSM60808 clock. The MSM60808 asserts CCLKRUN# while it outputs the clock,                 |

|             |       | and puts the pin in high impedance if it stops the clock.                                 |

| CRST#       | OUT   | CardBus reset signal. CRST# operates asynchronously to CCLK.                              |

|             |       | CardBus address/data bus signals. Address and data are multiplexed on the same            |

| CAD[31:0]   | T/S   | pins. During the first clock of a transaction CAD[31:0] carry a physical address          |

|             |       | (32 bits). During the following clocks CAD[31:0] carry data.                              |

|             |       | Command and byte enable signals. During the address phase of a transaction                |

| CC/BE#[3:0] | T/S   | CC/BE#[3:0] define the bus command. During the data phase CC/BE#[3:0] are used            |

|             |       | as byte enables.                                                                          |

|             |       | CardBus parity signal. CPAR provides even parity across CAD[31:0] and CC/BE#[3:0].        |

|             |       | Address parity is driven by the master that started the bus cycle one clock after the     |

| CPAR        | T/S   | address phase. In the data phase, the master calculates parity and drives CPAR for        |

|             |       | write cycles, and the target does so for read cycles. Just like the address phase, in the |

|             |       | data phase parity for data is output delayed by one clock.                                |

|             | S/T/S | CardBus cycle frame signal. CFRAME# is driven by the master to indicate the start         |

| CFRAME#     |       | and duration of a bus cycle. CFRAME# is asserted to indicate the start of a bus cycle.    |

| OI NAIVIL#  | 3/1/3 | Bus cycles continue while CFRAME# stays asserted. CFRAME# is deasserted to                |

|             |       | indicate that the next data phase is the final data phase.                                |

|             |       | CardBus device select signal. When the MSM60808 is the target, it will respond to         |

| CDEVSEL#    | S/T/S | bus cycles where CDEVSEL# is asserted. When the MSM60808 is the master, it                |

|             |       | monitors CDEVSEL# to determine whether or not the target has responded.                   |

|             |       | CardBus initiator ready signal. CIRDY# indicates that the master is ready to perform a    |

|             |       | transfer. CIRDY# is used in conjunction with CTRDY#. Data transfers are timed to          |

| CIRDY#      | S/T/S | execute when both CIRDY# and CTRDY# are asserted. During write cycles CIRDY#              |

| #ו עחוט     | 3/1/3 | indicates that valid data is on CAD[31:0]. During read cycles CIRDY# indicates that       |

|             |       | the device is ready to accept read data. Wait cycles are inserted until both CIRDY#       |

|             |       | and CTRDY# are asserted together.                                                         |

Table 4.2 CardBus Interface Signals (continued)

| Signal Name | I/O   | Description                                                                             |

|-------------|-------|-----------------------------------------------------------------------------------------|

|             |       | CardBus target ready signal. CTRDY# indicates that the target is ready to perform a     |

|             |       | transfer. CTRDY# is used in conjunction with CIRDY#. Data transfers are timed to        |

| CTRDY#      | S/T/S | execute when both CIRDY# and CTRDY# are asserted. During read cycles CTRDY#             |

| OTTIDI#     | 0/1/0 | indicates that valid data is on CAD[31:0]. During write cycles CTRDY# indicates that    |

|             |       | the device is ready to accept write data. Wait cycles are inserted until both CIRDY#    |

|             |       | and CTRDY# are asserted together.                                                       |

| CSTOP#      | S/T/S | CardBus Stop signal. CSTOP# is used by the target to request that the master stop       |

|             | 3/1/3 | the current transaction.                                                                |

| CBLOCK#     | S/T/S | CardBus block signal. CBLOCK# is an optional signal used when the bus master            |

| UBLUUK#     | 3/1/3 | executes a fatal access. The MSM60808 does not support this signal.                     |

| CPERR#      | S/T/S | CardBus parity error signal. CPERR# reports only data parity errors during all          |

| UPENN#      | 3/1/3 | transactions except special cycles.                                                     |

| CCEDD#      | O/D   | CardBus system error signal. CSERR# reports address parity errors and other fatal       |

| CSERR#      |       | system errors.                                                                          |

|             | IN    | CardBus request signal. CREQ# is asserted when the CardBus master requests use          |

| CREQ#       |       | of the PCI bus. When cards are inserted in two slots, the MSM60808's internal           |

|             |       | arbiter function will respond to request for asserting CGNT# for one or the other card. |

| CGNT#       | T/S/0 | CardBus grant signal. CGNT# asserted by the MSM60808 indicates that the CardBus         |

| GGN1#       |       | master has been granted PCI bus usage rights.                                           |

| CINT#       | IN    | CardBus interrupt signal. CINT# is used to request an interrupt from a CardBus card.    |

| GIN1#       |       | CardBus interrupts are level sensitive.                                                 |

| CSTSCHG     | IN    | CardBus card status change signal. CSTSCHG is used to inform the system when a          |

|             | IIV   | CardBus card's ready state, write protect state, or battery state changes.              |

|             |       | CardBus card audio signal. CAUDIO is a digital audio output signal from the CardBus     |

| CAUDIO      | IN    | card to a system speaker. This signal is output to the system from the MSM60808's       |

|             |       | SPKROUT# pin.                                                                           |

| CCD1#       |       | CardBus card detect signals. CCD1# and CCD2# are used in conjunction with the           |

| CCD2#       | IN    | CardBus voltage sense signals to determine the card type and voltage of a CardBus       |

|             |       | card.                                                                                   |

| CVS1#       | T/S   | CardBus voltage sense signals. CVS1# and CVS2# are used in conjunction with the         |

| CVS2#       | 1/5   | CardBus card detect signals to determine the card type and voltage of a CardBus card.   |

### 4.4 16-Bit Card Interface Signals

Table 4.3 16-bit Card Interface Signals

| Signal Name  | I/O      | Description                                                                                                                                                            |

|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET        | OUT      | Reset signal.                                                                                                                                                          |

| A[25:0]      | T/S/0    | Address signals. A25 is the most significant bit.                                                                                                                      |

| D[15:0]      | T/S      | Data signals. D15 is the most significant bit.                                                                                                                         |

| CE1#         | T/S/0    | Card enable signals. CE1# is used to enable even bytes, and CE2# is used to enable                                                                                     |

| CE2#         | 1/3/0    | odd bytes.                                                                                                                                                             |

|              |          | Attribute memory select signals. A high level on REG# indicates an access to                                                                                           |

| REG#         | T/S/0    | common memory space. A low level indicates an access to attribute memory space                                                                                         |

|              |          | or IO space.                                                                                                                                                           |

| WE#          | T/S/0    | Write enable signal. WE# is asserted when write data is output to a memory card.                                                                                       |

| OE#          | T/S/0    | Output enable signal. OE# is asserted when memory read data is read from a memory card.                                                                                |

| IOWR#        | T/S/0    | IO write signal. IOWR# is asserted when data is written to a card's IO space.                                                                                          |

| IORD#        | T/S/0    | IO read signal. IORD# is asserted when data is read from a card's IO space.                                                                                            |

| INPACK#      | IN       | Input acknowledge signal. INPACK# is asserted by a PC Card when it responds to an                                                                                      |

|              | IIV      | IO read access.                                                                                                                                                        |

| WAIT#        | IN       | Wait signal. WAIT# is asserted by a PC Card when it wants to delay completion of a                                                                                     |

| WAII#        | 114      | bus cycle in progress.                                                                                                                                                 |

|              |          | Ready signal. For memory cards, when READY is driven low it indicates that the card                                                                                    |

| READY        | IN       | is in a busy state. When READY is high it indicates that the card is prepared to accept                                                                                |

| (IREQ#)      | 114      | a new data transfer command. For IO cards, this signal is used as an interrupt request                                                                                 |

|              |          | signal (IREQ#).                                                                                                                                                        |

| WP           |          | Write protect signal. For memory cards, WP reflects the state of the write protect                                                                                     |

| (IOS16#)     | IN       | switch. For IO cards, this signal is asserted low by the card when 16-bit access is                                                                                    |

|              |          | allowed (IOS16#).                                                                                                                                                      |

|              |          | Battery voltage detect signal 1. For memory cards, BVD1 is used in conjunction with                                                                                    |

|              |          | BVD2 by to indicate the battery state of the PC Card. When both BVD1 and BVD2 are                                                                                      |

| BVD1         | INI      | high, the battery is good. When BVD1 is high but BVD2 goes low, the battery enters a                                                                                   |

| (STSCHG#/RI) | IN       | warning state. When BVD1 goes low, the battery cannot supply operating voltage regardless of the state of BVD2. For IO cards, this signal is used to indicate a change |

|              |          | to the card's ready state, write protect state, battery state, or (for modem cards)                                                                                    |

|              |          | ringing indicator (STSCHG#/RI).                                                                                                                                        |

|              |          | Battery voltage detect signal 2. For memory cards, BVD1 is used in conjunction with                                                                                    |

|              |          | BVD2 by to indicate the battery state of the PC Card. When both BVD1 and BVD2 are                                                                                      |

|              |          | high, the battery is good. When BVD1 is high but BVD2 goes low, the battery enters a                                                                                   |

| BVD2         | IN       | warning state. When BVD1 goes low, the battery cannot supply operating voltage                                                                                         |

| (SPKER#)     |          | regardless of the state of BVD2. For IO cards, this signal is used as a binary audio                                                                                   |

|              |          | signal from the card (SPKR#). This signal will be output to the system from the                                                                                        |

|              |          | MSM60808's SPKROUT# pin.                                                                                                                                               |

|              | <u> </u> |                                                                                                                                                                        |

Table 4.3 16-bit Card Interface Signals (continued)

| Signal Name | I/O | Description                                                                       |  |

|-------------|-----|-----------------------------------------------------------------------------------|--|

| CD1#        | IN  | Card detect signals. CD1# and CD2# are used in conjunction with the voltage sense |  |

| CD2#        |     | signals to determine the card type and voltage of a card.                         |  |

| VS1#        | T/S | Card voltage sense signals. VS1# and VS2# are used in conjunction with the card   |  |

| VS2#        |     | detect signals to determine the card type and voltage of a card.                  |  |

### 4.5 Interrupt Signals

**Table 4.4 Interrupt Signals**

| Signal Name | I/O | Description                                                                              |  |

|-------------|-----|------------------------------------------------------------------------------------------|--|

| IREQ3/INTA# | OUT | Interrupt request signals 2 and 4. Those pin connect to DCI or ICA interrupts            |  |

| IREQ4/INTB# |     | Interrupt request signals 3 and 4. These pin connect to PCI or ISA interrupts.           |  |

| IREQ5       | 7.0 | Interrupt request signals 5, 7, 9, 10, 11, 12, and 14. These signals are ISA interrupts. |  |

| IREQ7       |     |                                                                                          |  |

| IREQ9       |     |                                                                                          |  |

| IREQ10      | T/S |                                                                                          |  |

| IREQ12      |     |                                                                                          |  |

| IREQ14      |     |                                                                                          |  |

| IREQ15      | OUT | Interrupt request signal 15. This signal is used as either an interrupt line or as an    |  |

| /RI_OUT     |     | output pin for a modem's ring indicator.                                                 |  |

### 4.6 Audio Signals

Table 4.5 Audio Signals

| Signal Name           | I/O    | Description                                                                                                                                                                                                                           |  |

|-----------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SPKROUT#<br>/SVSPEND# | IN/OUT | Speaker out signal. SPKROUT# outputs the digital audio signal from a PC Card to the system speaker. When the suspend mode bit: bit 1 of the card control register (CDCTL) is enabled, this pin is used as the suspend # input signal. |  |

### 4.7 PC Card Power Switch Signals (TPS2202Al Interface)

**Table 4.6 PC Card Power Switch Signals**

| Signal Name | I/O                                                                             | Description                                                                            |  |

|-------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|

| LATCH       | OUT                                                                             | Power switch latch signal. LATCH is asserted to indicate that data on the DATA line is |  |

|             |                                                                                 | valid.                                                                                 |  |

| CLOCK       | OUT                                                                             | Power switch clock signal. Data on the DATA line is sampled on the rising edge of      |  |

|             |                                                                                 | CLOCK. The maximum frequency value is 2 MHz.                                           |  |

| DATA        | OUT Power switch data signal. DATA serially transmits socket power control info |                                                                                        |  |

### 4.8 Voltage Supply Signals

**Table 4.7 Voltage Supply Signals**

| Signal Name | I/O | Description                                               |  |

|-------------|-----|-----------------------------------------------------------|--|

| GND         | IN  | Device ground.                                            |  |

| VCCA        | IN  | PC Card A voltage supply. 5V or 3.3V may be supplied.     |  |

| VCCB        | IN  | PC Card B voltage supply. 5V or 3.3V may be supplied.     |  |

| VCCP        | IN  | PCI interface voltage supply. 5V or 3.3V may be supplied. |  |

| VCC         | IN  | Core logic voltage supply. Fixed at 3.3V.                 |  |

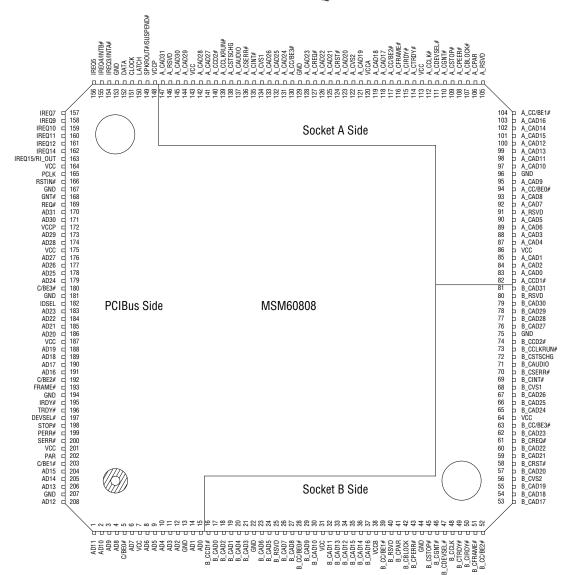

### 4.9 Pinout

### 4.9.1 PCI Bus - CardBus Pinout

### 208-Pin Plastic LQFP

### 4.9.2 PCI Bus - 16-Bit Pinout

### 208-Pin Plastic LQFP

### 5. Registers

### **5.1 Configuration Registers**

Configuration registers determine the basic operation of the MSM60808 bridge.

| Addr     |          |          |           |            |

|----------|----------|----------|-----------|------------|

| 00h      | Devi     | ceID     | Ven       | dID        |

| 04h      | PCI S    | Status   | PCI Coi   | mmand      |

| 08h      |          | CCODE    |           | REVID      |

| 0Ch      | Reserved | HTYPE    | LTCTM     | Reserved   |

| 10h      |          | PCCD     | BADR      |            |

| 14h      | CBS      | STS      | Rese      | rved       |

| 18h      | CBLTCTM  | SUBUSN   | CBBUSN    | PCIBUSN    |

| 1Ch      |          | MEMBASE0 |           |            |

| 20h      |          | MEML     | IMIT0     |            |

| 24h      |          | MEME     | BASE1     |            |

| 28h      |          | MEML     | IMIT1     |            |

| 2Ch      | IOBA     | SE0U     | IOBA      | SE0L       |

| 30h      | IOLIN    | 1IT0U    | IOLIN     | 1ITOL      |

| 34h      | IOBA     | SE1U     | IOBA      | SE1L       |

| 38h      | IOLIN    | MIT1U    | IOLIN     | /IIT1L     |

| 3Ch      | BRG      | iCTL     | INTPIN    | INTLIN     |

| 40h      | SubSy    | stemID   | SubSystem | n VendorID |

| 44h      | R21BADR  |          |           |            |

| 48 - 8Ch | Reserved |          |           |            |

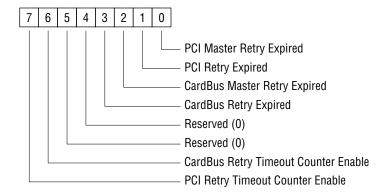

| 90h      | BFFCTL   | DVCTL    | CDCTL     | RTYCTL     |

| 94 - FFh | Reserved |          |           |            |

Figure 5.1 Configuration Register Space

### 5.1.1 Vendor ID Register (Vend ID)

Register offset : 00h

Default value : 1021h

Access : Read-only

Size : 16-bit

1021h indicates the OKI product.

### 5.1.2 Device ID Register (Device ID)

Register offset : 02h

Default value : 3002h

Access : Read-only

Size : 16-bit

3002h indicates the specific ID of the MSM60808 device.

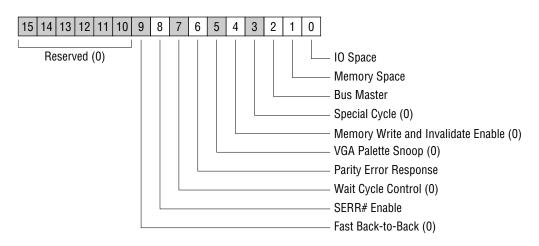

### 5.1.3 PCI Command Register (PCI Command)

Register offset : 04h

Default value : 0000h

Access : Read/write

Size : 16-bit

| Bit         | Description                                                                                       |

|-------------|---------------------------------------------------------------------------------------------------|

| Bit [15:10] | These reserved bits always read as 0.                                                             |

| Bit 9       | The MSM60808 does not support the Fast Back-to-Back function. This bit will always read as 0.     |

| Bit 8       | The SERR# Enable bit determines whether or not to report system errors. If 1, then system         |

| DIL O       | errors will be reported. If 0, then SERR# will not be reported even when errors occur.            |

| Bit 7       | The Wait Cycle Control bit's function is not supported by the MSM60808. This bit will always      |

| DIL /       | read as 0.                                                                                        |

| Dit C       | The Parity Error Response bit controls whether or not a parity error will be reported if a one is |

| Bit 6       | detected.                                                                                         |

| Bit 5       | The VGA Palette Snoop bit's function is not supported by the MSM60808. This bit will always       |

| C IID       | read as 0.                                                                                        |

| D:+ 4       | The Memory Write and Invalidate Enable bit's function is not supported by the MSM60808.           |

| Bit 4       | This bit will always read as 0.                                                                   |

| Bit 3       | The MSM60808 will not respond to the command of a Special Cycle bit.                              |

| DIL 3       | This bit will always read as 0.                                                                   |

|             | The Bus Master bit controls whether or not the MSM60808 will operate as the bus master.           |

| Bit 2       | If set to 1, the card will operate as the bus master. If 0, then the card will be recognized as a |

|             | target device.                                                                                    |

|             | The Memory Space bit controls whether or not to respond to memory accesses on the PCI bus.        |

| Bit 1       | If this bit is 0, then the MSM60808 will not respond to memory commands. If 1, then it will       |

|             | respond.                                                                                          |

| Di+ O       | The IO Space bit controls whether or not to respond to IO accesses on the PCI bus. If this bit is |

| Bit 0       | 0, then the MSM60808 will not respond to IO commands. If 1, then it will respond.                 |

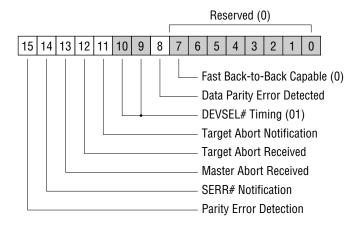

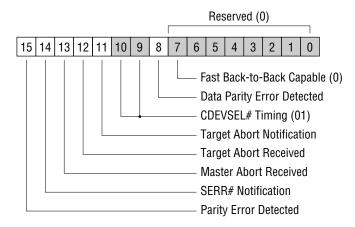

### 5.1.4 PCI Status Register (PCI Status)

Register offset : 06h

Default value : 0000h

Access : Read/write

Size : 16-bit

| Bit        | Description                                                                                       |  |  |

|------------|---------------------------------------------------------------------------------------------------|--|--|

| Bit 15     | The Parity Error Detected bit is set to 1 when a parity error is detected. Writing 1 to this bit  |  |  |

|            | clears it. Writing 0 has no effect.                                                               |  |  |

| Bit 14     | The SERR# Notification bit is set to 1 when the bridge reports a system error. Writing 1 to this  |  |  |

| DIL 14     | bit clears it. Writing 0 has no effect.                                                           |  |  |

| Bit 13     | The Master Abort Received bit is set to 1 when a master abort is received. Writing 1 to this bit  |  |  |

| DIL 13     | clears it. Writing 0 has no effect.                                                               |  |  |

| D:+ 10     | The Target Abort Received bit is set to 1 when a target abort is received by the MSM60808         |  |  |

| Bit 12     | during a PCI bus access. Writing 1 to this bit clears it. Writing 0 has no effect.                |  |  |

| D:+ 11     | The Target Abort Notification bit is set to when this MSM60808 device reports a target abort.     |  |  |

| Bit 11     | Writing 1 to this bit clears it. Writing 0 has no effect.                                         |  |  |

| Di+ [10·0] | The DEVSEL# Timing bits are encoded with the device response time. Since the MSM60808 is          |  |  |

| Bit [10:9] | medium speed, these bits are encoded with 01b. These bits are read-only.                          |  |  |

|            | Only bus masters need to implement the Data Parity Error Detected bit. The MSM60808 has           |  |  |

| Bit 8      | been implement for master cards. This bit is set to 1 when a data parity error is detected on the |  |  |

|            | PCI bus. Writing 1 to this bit clears it. Writing 0 has no effect.                                |  |  |

| D: 7       | The MSM60808 does not support the Fast Back-to-Back Capable function.                             |  |  |

| Bit 7      | This bit always reads as 0.                                                                       |  |  |

| Bit [6:0]  | These reserved bits always read as 0.                                                             |  |  |

### 5.1.5 Revision ID Register (REVID)

Register offset : 08h Default value : 01h

Access : Read-only Size : 8-bit

This register contains the revision number of the device. The MSM60808's revision level is 01h.

### 5.1.6 Class Code Programming Interface Byte Register (CCPIB)

Register offset : 09h Default value : 00h

Access : Read-only Size : 8-bit

There is no specific register-level programming for this class code (indicated by the CCCB register). Therefore, the value of this field is 00h.

### 5.1.7 Class Code Sub-Class Code Byte Register (CCCB)

Register offset : 0Ah

Default value : 0607h

Access : Read-only

Size : 16-bit

Bits [15:8]: 06h indicate a bridge function. Bits [7:0]: 07h indicate the PCI-CardBus bridge function.

### 5.1.8 Latency Timer Register (LTCTM)

Register offset : 0Dh Default value : 00h

Access : Read/write

Size : 8-bit

This register is used only for the PCI bus interface. When the MSM60808 is the master, GNT # is deasserted, and the MSM60808 will complate data transfers after the latency timer expires.

**OKI** Semiconductor

MSM60808

| Bit        | Description                      |

|------------|----------------------------------|

| Bit [7:;0] | Timer setting.                   |

|            | Oh : Do not start latency timer. |

|            | 1h : 8 clocks                    |

|            | 2h : 16 clocks                   |

|            | 3h : 24 clocks                   |

|            | 4h : 32 clocks                   |

|            | 5h : 40 clocks                   |

|            | 6h : 48 clocks                   |

|            | 7h : 56 clocks                   |

|            | 8h : 64 clocks                   |

|            | 9h~FFh : Reserved                |

### 5.1.9 Header Type Register (HTYPE)

Register offset : 0Eh

Default value : 82h

Access : Read-only

Size : 8-bit

The MSM60808 is a multifunction bridge device, so the value of this register is 82h. This register is read-only.

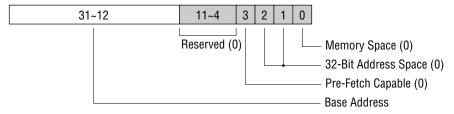

### 5.1.10 PC Card Socket Status Base Address Register (PCCDBADR)

Register offset : 10h

Default value : 0000 0000h Access : Read/write Size : 32-bit

This register stores the base address of CardBus registers and 16-bit card registers. The address pointed to by this register is mapped into memory space.

Bits 31~12 are read/write. Bits 11~0 are read-only, and will output 0, when read.

| Bit         | Description                                                                                     |  |  |

|-------------|-------------------------------------------------------------------------------------------------|--|--|

| D# [04.40]  | The Base Address determines the starting address of PC Card socket status control registers     |  |  |

| Bit [31:12] | mapped into system memory space.                                                                |  |  |

| Bit [11:4]  | Reserved (0). All bits are fixed 0 and read-only.                                               |  |  |

| Bit 3       | Pre-Fetch Capable bit is fixed 0. Pre-fetch reads cannot be performed.                          |  |  |

| Bit [2:1]   | These bits are fixed 00 to indicate that a 32-bit address space is used.                        |  |  |

| Bit 0       | The Memory Space indicator bit is fixed 0 to indicate that there is mapped in the memory space. |  |  |

### 5.1.11 CardBus Status Register (CBSTS)

Register offset : 16h

Default value : 0000h

Access : Read/Write

Size : 16-bit

| Bit        | Description                                                                                      |  |  |

|------------|--------------------------------------------------------------------------------------------------|--|--|

| Bit 15     | The Parity Error Detected bit is set to 1 when a parity error is detected.                       |  |  |

| Dit 4.4    | The SERR# Notification bit is set to 1 when the bridge reports a system error. Writing 1 to this |  |  |

| Bit 14     | bit clears it. This bit is 0 after reset.                                                        |  |  |

| Bit 13     | The Master Abort Received bit is set to 1 when a master abort is received                        |  |  |

|            | The Target Abort Received bit is set to 1 when a target abort is received by the MSM60808        |  |  |

| Bit 12     | during a CardBus access. Writing 1 to this bit clears it. Writing 0 has no effect.               |  |  |

|            | This bit is 0 after reset.                                                                       |  |  |

| Dirdd      | The Target Abort Notification bit is set to 1 when this MSM60808 device reports a target abort.  |  |  |

| Bit 11     | Writing 1 to this bit clears it. Writing 0 has no effect. This bit is 0 after reset.             |  |  |

| D:+ [40.0] | The CDEVSEL# Timing bits are encoded with the device response time. Since the MSM60808 is        |  |  |

| Bit [10:9] | medium speed, these bits are encoded with 01b. These bits are read-only.                         |  |  |

| Dit 0      | Only bus masters need to implement the Data Parity Error Detected bit. The MSM60808 has          |  |  |

| Bit 8      | been implement for master cards. This bit is set to 1 when a data parity error is detected.      |  |  |

| Bit 7      | The MSM60808 does not support the Fast Back-to-Back Capable function.                            |  |  |

|            | This bit always reads as 0.                                                                      |  |  |

| Bit [6:0]  | These reserved bits always read as 0.                                                            |  |  |

MSM60808

**OKI** Semiconductor

### 5.1.12 PCI Bus Number (PCIBUSN)

Register offset : 18h Default value : 00h

Access : Read/write

Size : 8-bit

This read/write register is used to store the number of the PCI bus connected to the MSM60808. It is set by configuration or socket services software.

### 5.1.13 CardBus Bus Number (CBBUSN)

Register offset : 19h Default value : 00h

Access : Read/write

Size : 8-bit

This read/write register is used to store the number of the CardBus bus connected to the MSM60808. The PCIBIOS writes a value to this register. The MSM60808 uses this register to determine whether or not to respond to Type 1 configuration cycles on the PCI bus. If it does respond, the MSM60808 will generate a Type 0 configuration cycle on the CardBus interface.

### 5.1.14 Subordinate Bus Number (SUBUSN)

Register offset : 1Ah Default value : 00h

Access : Read/write

Size : 8-bit

This read/write register stores the maximum bus number of the CardBus. The PCIBIOS writes a value to this register. The MSM60808 uses this register along with CBBUSN to determine whether or not to forward Type 1 configuration cycles on the CardBus.

**OKI** Semiconductor

MSM60808

## 5.1.15 CardBus Latency Timer Register (CBLTCTM)

Register offset : 1Bh Default value : 00h

Access : Read/write

Size : 8-bit

This register is used only for the CardBus interface. When the MSM60808 is the master, it will complete data transfers after the latency timer expires.

| Bit        | Description                      |

|------------|----------------------------------|

| Bit [7:;0] | Timer setting.                   |

|            | Oh : Do not start latency timer. |

|            | 1h : 8 clocks                    |

|            | 2h : 16 clocks                   |

|            | 3h : 24 clocks                   |

|            | 4h : 32 clocks                   |

|            | 5h : 40 clocks                   |

|            | 6h : 48 clocks                   |

|            | 7h : 56 clocks                   |

|            | 8h : 64 clocks                   |

|            | 9h~FFh : Reserved                |

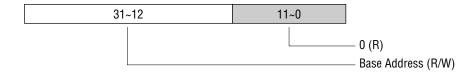

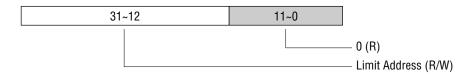

#### 5.1.16 Memory Base Register 0 (MEMBASE0)

Register offset : 1Ch

Default value : 0000 0000h Access : Read/write Size : 32-bit

The Memory Base Register defines the base address of a memory mapped IO address range that is used by the MSM60808 to determine whether or not to forward memory transactions from one interface to the other. This window is enabled by bit 1 of the Command Register.

| Bit         | Description                                                                          |

|-------------|--------------------------------------------------------------------------------------|

| Bit [31:12] | The Base Address corresponds to AD[31:12]. It is read/write.                         |

| Bit [11:0]  | All bits AD[11:0] are 0 (4 KB window). These bits are read-only and always return 0. |

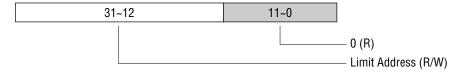

#### 5.1.17 Memory Limit Register 0 (MEMLIMIT0)

Register offset : 20h

Default value : 0000 0000h Access : Read/write

Size : 32-bit

The Memory Limit Register defines the highest address of a memory mapped IO address range that is used by the MSM60808 to determine whether or not to forward memory transactions from one interface to the other. This window is enabled by bit 1 of the Command Register.

| Bit         | Description                                                                          |

|-------------|--------------------------------------------------------------------------------------|

| Bit [31:12] | The Limit Address corresponds to AD[31:12]. It is read/write.                        |

| Bit [11:0]  | All bits AD[11:0] are 0 (4 KB window). These bits are read-only and always return 0. |

#### 5.1.18 Memory Base Register 1 (MEMBASE1)

Register offset : 24h

Default value : 0000 0000h Access : Read/write Size : 32-bit

The Memory Base Register defines the base address of a memory mapped IO address range that is used by the MSM60808 to determine whether or not to forward memory transactions from one interface to the other. This window is enabled by bit 1 of the Command Register.

| Bit         | Description                                                  |

|-------------|--------------------------------------------------------------|

| Bit [31:12] | The Base Address corresponds to AD[31:12]. It is read/write. |

| Bit [11:0]  | These bits are read-only and always return 0.                |

#### 5.1.19 Memory Limit Register 1 (MEMLIMIT1)

Register offset : 28h

Default value : 0000 0000h Access : Read/write Size : 32-bit

The Memory Limit Register defines the highest address of a memory mapped IO address range that is used by the MSM60808 to determine whether or not to forward memory transactions from one interface to the other. This window is enabled by bit 1 of the Command Register.

| Bit         | Description                                                                          |

|-------------|--------------------------------------------------------------------------------------|

| Bit [31:12] | The Limit Address corresponds to AD[31:12]. It is read/write.                        |

| Bit [11:0]  | All bits AD[11:0] are 0 (4 KB window). These bits are read-only and always return 0. |

**OKI** Semiconductor

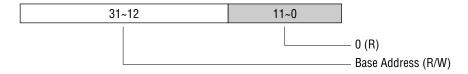

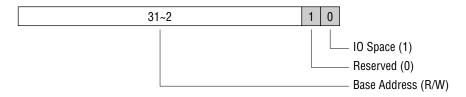

#### 5.1.20 IO Base Register 0L (IOBASE0L)

Register offset : 2Ch

Default value : 0000h

Access : Read/write

Size : 16-bit

The IO Base Register defines the bottom of the address range that is used by the MSM60808 to determine whether or not to forward IO transactions to the CardBus. This register's bits correspond to AD[15:0]. Bits [1:0] are read-only, and always return 0. When the address is decoded, only AD[15:12] are decoded; AD[11:2] are ignored. The minimum IO address range will be 4 KB.

#### 5.1.21 IO Base Register 0U (IOBASE0U)

Register offset : 2Eh

Default value : 0000h

Access : Read/write

Size : 16-bit

This register's bits correspond to AD[31:16]. This register is used to specify the location of the IO address block which is specified by the IO Base Register 0L and IO Limit Register 0L.

#### 5.1.22 IO Limit Register 0L (IOLIMIT0L)

Register offset : 30h

Default value : 0000h

Access : Read/write

Size : 16-bit

The IO Limit Register defines the top of the address range that is used by the MSM60808 to determine whether or not to forward IO transactions to the CardBus. This register's bits correspond to AD[15:0]. When the address is decoded, only AD[15:12] are decoded; AD[11:0] are ignored.

#### 5.1.23 IO Limit Register 0U (IOLIMIT0U)

Register offset : 32h

Default value : 0000h

Access : Read/write

Size : 16-bit

This register's bits correspond to AD[31:16]. This register has no relation to address decoding. It will return 0 when read.

**OKI** Semiconductor

MSM60808

#### 5.1.24 IO Base Register 1L (IOBASE1L)

Register offset : 34h

Default value : 0000h

Access : Read/write

Size : 16-bit

The IO Base Register defines the bottom of the address range that is used by the MSM60808 to determine whether or not to forward IO transactions to the CardBus. This register's bits correspond to AD[15:0]. Bits [1:0] are read-only, and always return 0. When the address is decoded, only AD[15:12] are decoded; AD[11:2] are ignored. The minimum IO address range will be 4 KB.

#### 5.1.25 IO Base Register 1U (IOBASE1U)

Register offset : 36h

Default value : 0000h

Access : Read/write

Size : 16-bit

This register's bits correspond to AD[31:16]. This register is used to specify the location of the IO address block which is specified by The IO Base Register 1L and IO Limit Register 1L.

#### 5.1.26 IO Limit Register 1L (IOLIMIT1L)

Register offset : 38h

Default value : 0000h

Access : Read/write

Size : 16-bit

The IO Limit Register defines the top of the address range that used by the MSM60808 to determine whether or not to forward IO transactions to the CardBus. This register's bits correspond to AD[15:0]. When the address is decoded, only AD[15:12] are decoded; AD[11:0] are ignored.

#### 5.1.27 IO Limit Register 1U (IOLIMIT1U)

Register offset : 3Ah

Default value : 0000h

Access : Read/write

Size : 16-bit

This register's bits correspond to AD[31:16]. This register has no relation to address decoding. It will return 0 when read.

## 5.1.28 Interrupt Line Register (INTLIN)

Register offset : 3Ch Default value : 00h

Access : Read/write

Size : 8bit

Bits [7:0]: the value of this register is recognized as the level of an interrupt request from the system interrupt controller connected to the MSM60808's interrupt pins.

#### 5.1.29 Interrupt Pin Register (INTPIN)

Register offset : 3Dh Default value : 00h

Access : Read-only

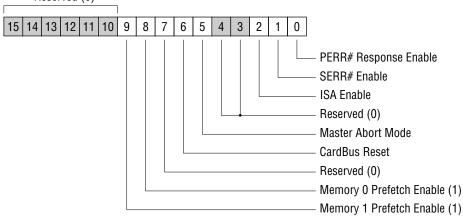

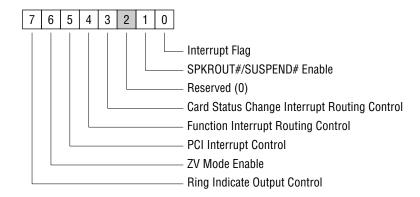

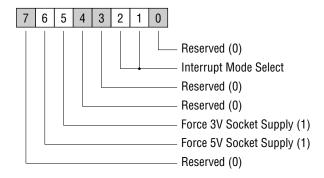

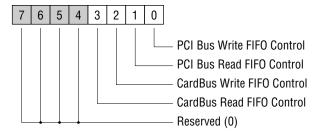

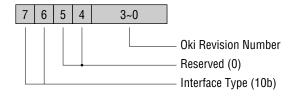

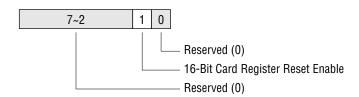

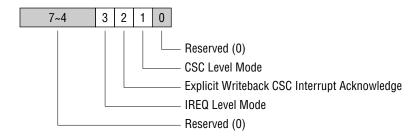

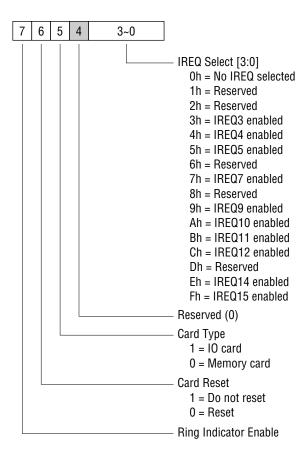

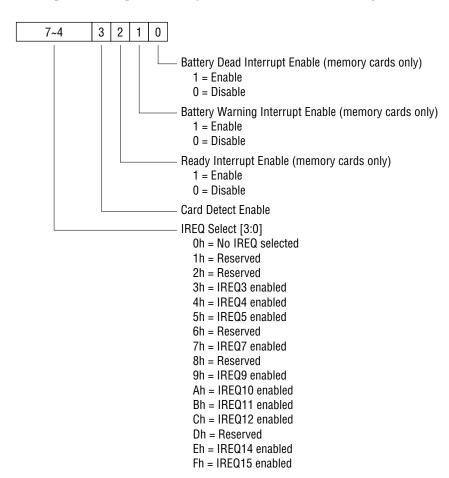

Size : 8bit